STM32将HSI通过PLL倍频到64MHZ

一、配置系统时钟

/***************************************************************

*函数名: vSystem_Clock_Config

*描 述: 配置系统时钟

*说 明: 将HSI通过PLL倍频到64MHZ

*注 意: HSI通过PLL倍频最大只能倍频到64MHZ

***************************************************************/

void vSystem_Clock_Config(void)

{

u32 startUpCount = 0, status = 0;

RCC_DeInit();//Resets RCC default state

RCC_HSICmd(ENABLE);//Enables HSI

do

{

status = RCC_GetFlagStatus(RCC_FLAG_HSIRDY);//HSI ready or not

startUpCount++;

}

while((status == RESET) || (startUpCount < HSE_STARTUP_TIMEOUT));

if(status == SET)

{

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);//Enable Prefetch Buffer

FLASH_SetLatency(FLASH_Latency_2);//Set code latency value Two Latency cycles

RCC_HCLKConfig(RCC_SYSCLK_Div1);//HCLK=SYSCLK

RCC_PCLK1Config(RCC_HCLK_Div1);//PCLK1/APB1=HCLK

RCC_PCLK2Config(RCC_HCLK_Div1);//PCLK2/APB2=HCLK

RCC_PLLConfig(RCC_PLLSource_HSI_Div2, RCC_PLLMul_16);//PLL clock=4M

RCC_PLLCmd(ENABLE);//Enables PLL

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);//System clock is PLLCLK

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08);

}

else

{

}

}

注意:

1.STM32系列HSI通过PLL倍频最大只能倍频到64MHZ。

2. 所用到的库有:

#include "stm32f10x_flash.h"

#include "stm32f10x_gpio.h"

#include "stm32f10x_rcc.h"

#include "stm32f10x_tim.h"

#include "misc.h"

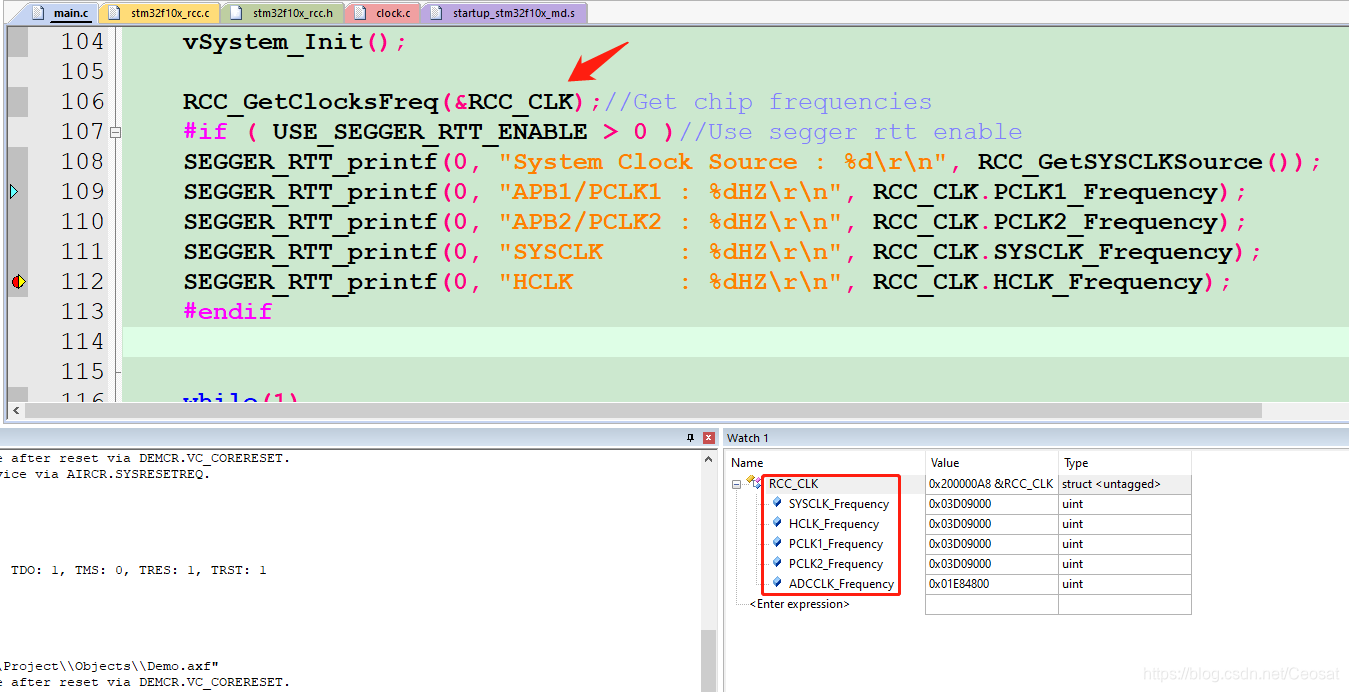

二、打印输出系统各时钟频率

RCC_ClocksTypeDef RCC_CLK;

int main(void)

{

vSystem_Init();

RCC_GetClocksFreq(&RCC_CLK);//Get chip frequencies

#if ( USE_SEGGER_RTT_ENABLE > 0 )//Use segger rtt enable

SEGGER_RTT_printf(0, "System Clock Source : %d\r\n", RCC_GetSYSCLKSource());

SEGGER_RTT_printf(0, "APB1/PCLK1 : %dHZ\r\n", RCC_CLK.PCLK1_Frequency);

SEGGER_RTT_printf(0, "APB2/PCLK2 : %dHZ\r\n", RCC_CLK.PCLK2_Frequency);

SEGGER_RTT_printf(0, "SYSCLK : %dHZ\r\n", RCC_CLK.SYSCLK_Frequency);

SEGGER_RTT_printf(0, "HCLK : %dHZ\r\n", RCC_CLK.HCLK_Frequency);

#endif

while(1)

{

vKeyBoard_Service_Handle();

PAout(6) = 0;

vDelay_ms(100);

PAout(6) = 1;

vDelay_ms(1000);

}

}

三、系统初始化vSystem_Init()

static void vSystem_Init(void)

{

SystemInit();

vSystem_Clock_Config();

vSysTick_Init();

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_4);

vTIM_Init();

vLCD1602_Init();

LED_Init();

vKEY_GPIO_Config();

#if ( USE_SEGGER_RTT_ENABLE > 0 )//Use segger rtt enable

SEGGER_RTT_Init();

SEGGER_RTT_printf(0, "Build Times: %s %s\r\n", __DATE__, __TIME__);

SEGGER_RTT_printf(0, "STM32F103xx Start Running......\r\n\r\n");

#endif

#if ( USE_KEIL_MACRO_INFO_ENBALE > 0 )//Use Keil macro information enable

vKeil_Macro_Information();

#endif

}

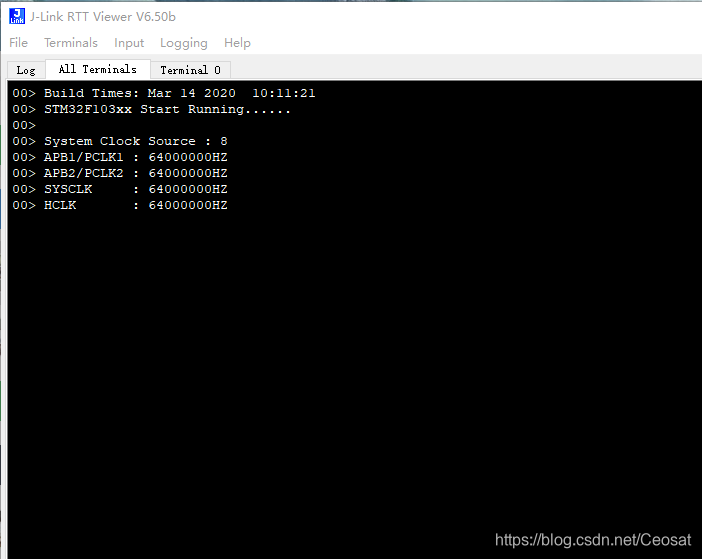

四、运行结果

00> Build Times: Mar 14 2020 10:11:21

00> STM32F103xx Start Running......

00>

00> System Clock Source : 8

00> APB1/PCLK1 : 64000000HZ

00> APB2/PCLK2 : 64000000HZ

00> SYSCLK : 64000000HZ

00> HCLK : 64000000HZ

STM32 HSI PLL 64MHz 配置

STM32 HSI PLL 64MHz 配置

本文详细介绍了如何在STM32上将HSI通过PLL倍频至64MHz,包括系统时钟配置、时钟频率打印及系统初始化过程。通过具体代码实现,展示了STM32系统时钟的精确控制。

本文详细介绍了如何在STM32上将HSI通过PLL倍频至64MHz,包括系统时钟配置、时钟频率打印及系统初始化过程。通过具体代码实现,展示了STM32系统时钟的精确控制。

2946

2946

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?