本文主要介绍在使用Vivado HLS的命令窗口执行时遇到问题及解决办法。

前言

相信大家平时在使用Vivado等系列软件进行开发时,会用到Tcl脚本命令等方法来进行快速原型开发和脚本编程,Vivado HLS也是支持Tcl脚本方法的。

这里主要说一下Vivado HLS的Tcl执行过程中出现的问题。

问题描述

笔者在复现一个开源项目时,根据该帖子https://zhuanlan.zhihu.com/p/41372775?from_voters_page=true中步骤一的指引,要在Vivado HLS 2018.2 Command Prompt中执行几条指令。

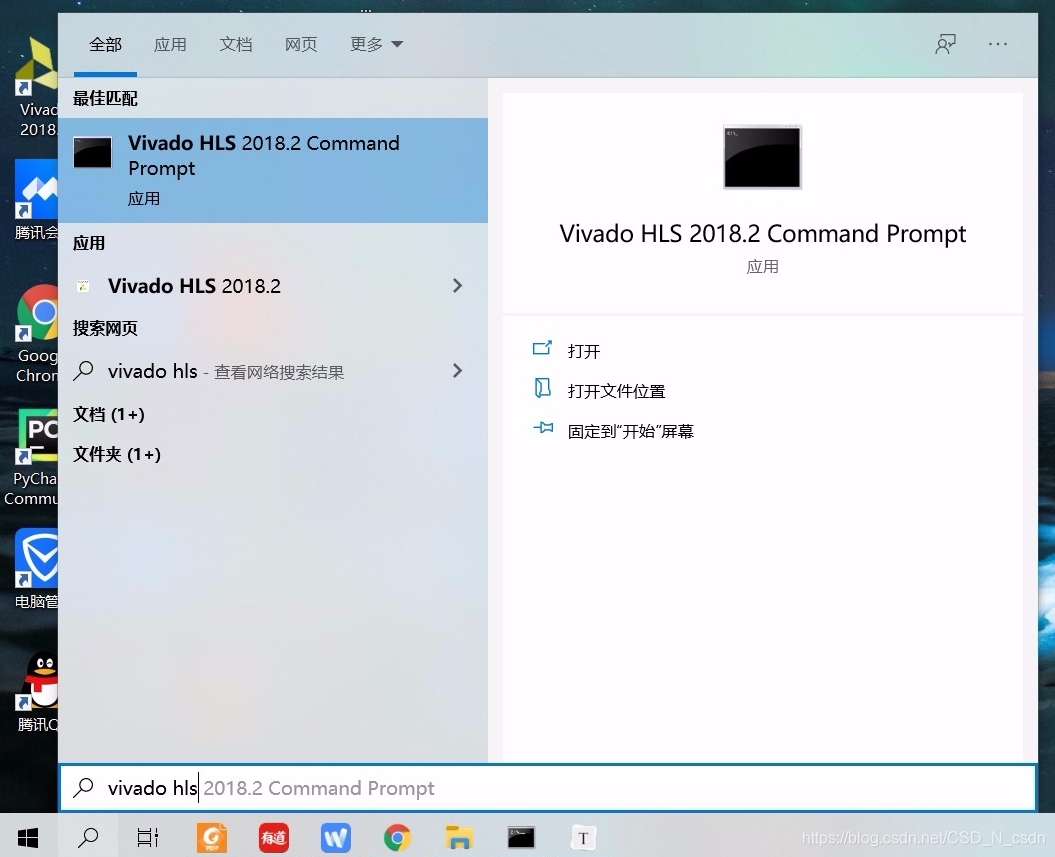

首先,在windows搜索栏键入vivado hls,打开vivado hls命令行,如图

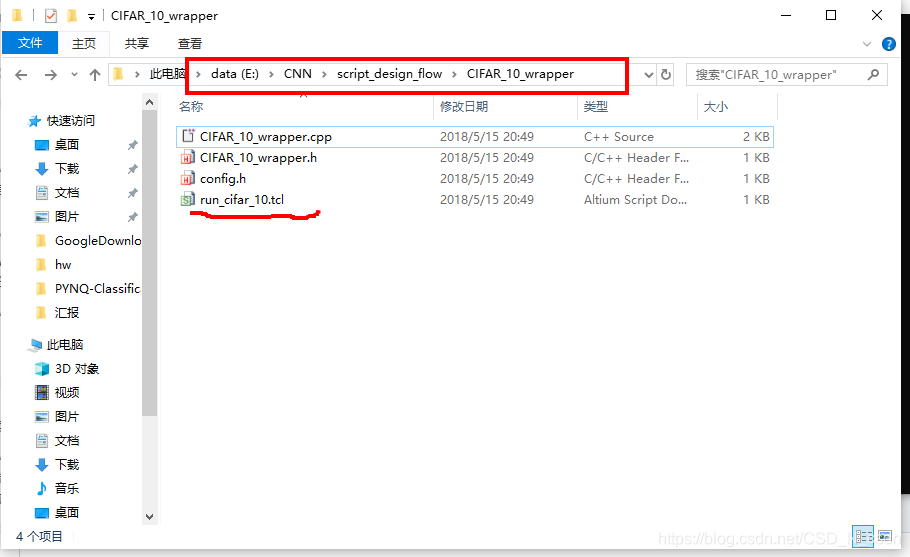

下面,我要进入E盘的一个文件夹下面,然后执行文件夹里的一个run_cifar_10.tcl文件。

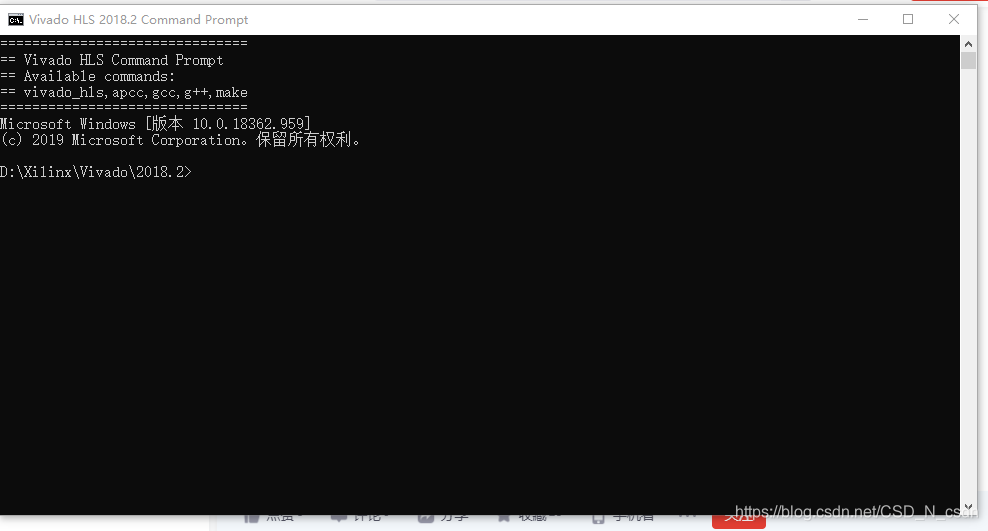

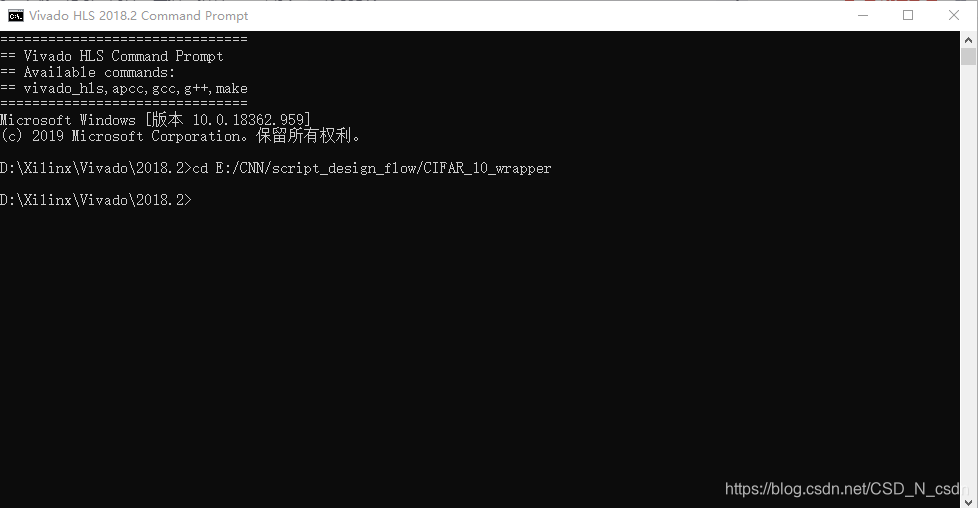

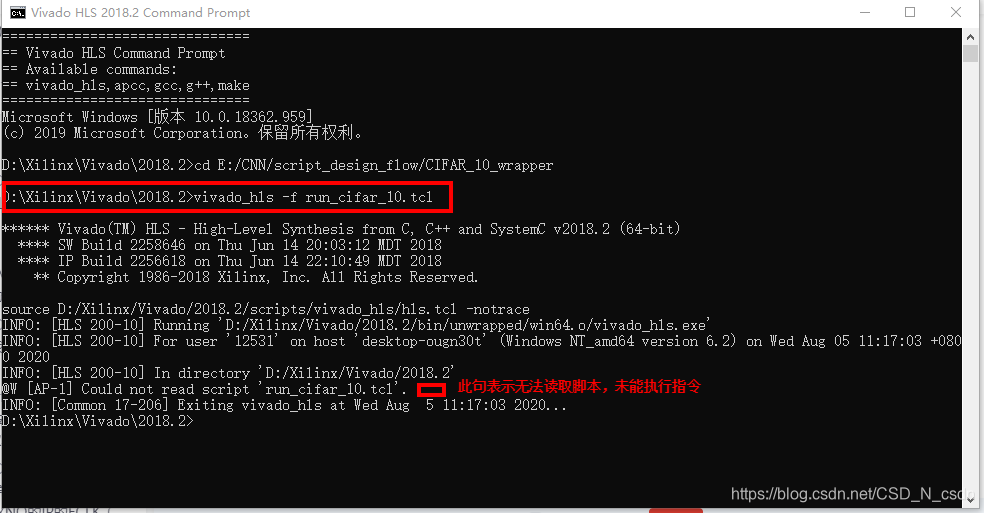

直接键入如下命令:cd E:/CNN/script_design_flow/CIFAR_10_wrapper 然后回车,发现并没有执行,如图左。我又检查了一下文件路径是否正确,发现没问题,如图右。

然后,我心想,文件路径都进不去,更别说下一步执行编译Tcl文件的指令了,果然,当我接着输入下一条指令然后回车,并没有执行。

解决方法

经过我的认真思考,觉着会不会是当时安装软件Vivado hls时,环境变量配置的问题,所以导致无法编译,然后我又去找了一下此软件的安装教程,发现并没有关于配置环境变量的步骤,好吧,看来问题不是出在这。

一顿百度之后,我觉着好像并没有人遇到过这个问题,所以我又去请教计算机专业的同学,她告诉我,在linux和windows的系统下,有些命令是有差别的,所以,在windows系统下的命令窗口,输入指令也有差别!

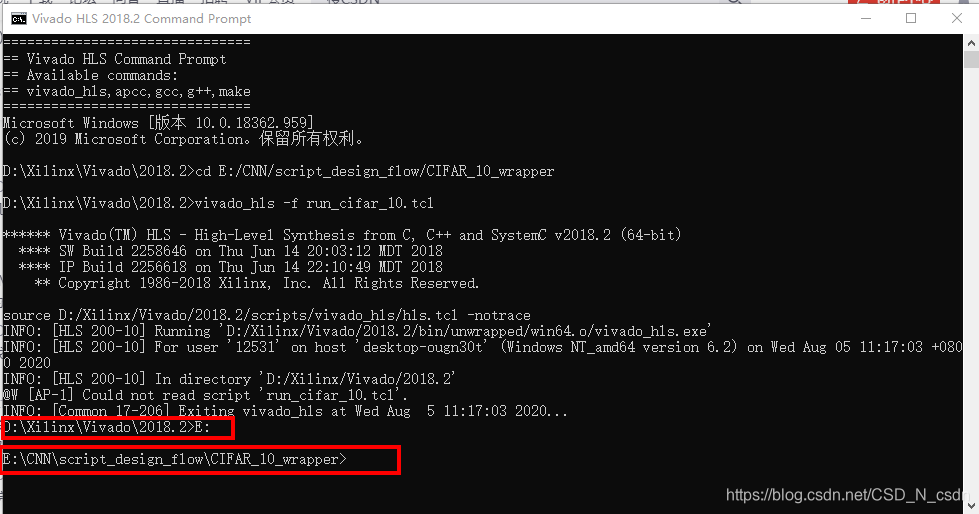

解决方法是,直接输入:E:按回车,就可以进入E盘的文件夹了,而且是直接进入到了之前指定的文件夹,如图,这也说明,之前cd E:/CNN/script_design_flow/CIFAR_10_wrapper 这条指令虽然没有执行,但是已经存储在了缓存中。

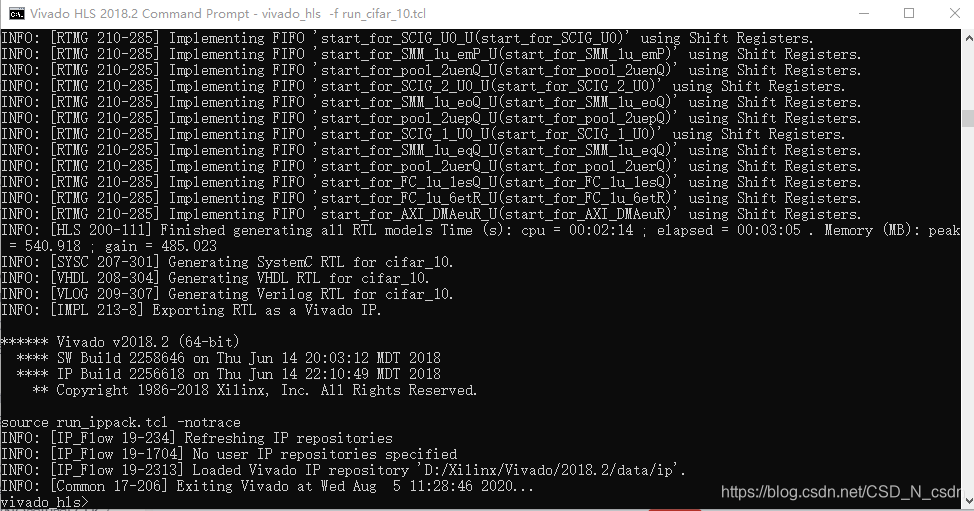

后面执行其他的编译指令就一帆风顺了,瞬间通畅!

总结

这个看似很小的问题,却困扰了我整晚的时间,原因其实是,windows与Linux系统的文件管理不同,在windows下,从D盘是无法cd到E盘的,因为这两个盘是并列的关系,而在Linux中,有根目录的概念,所以可以cd跳转。嗯,目前我的理解就这样!

如果本文对你有帮助,请点赞鼓励,谢谢!

本文解决在VivadoHLS中通过TCL命令执行文件路径切换的问题,阐述了Windows与Linux系统下文件路径管理的区别,提供了解决方案。

本文解决在VivadoHLS中通过TCL命令执行文件路径切换的问题,阐述了Windows与Linux系统下文件路径管理的区别,提供了解决方案。

1433

1433

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?