////

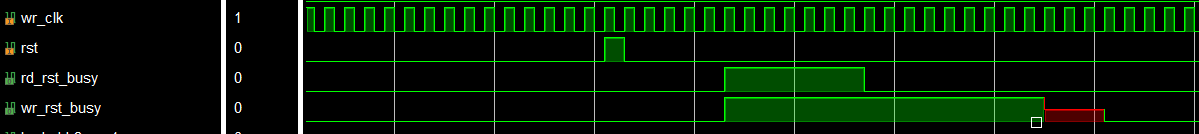

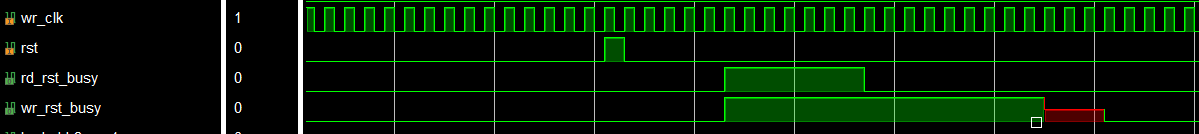

图1:Vivado的fifo复位信号使能后,wr_rst_busy复位需要经过约20个clock才能结束;这个与ISE的FIFO复位所需时钟周期数的差异很大;

说明:FIFO复位后,缓存的数据被清零。

////

文章对比了Vivado和ISE工具中FIFO与Bram复位信号的时序行为。在Vivado中,FIFO的wr_rst_busy复位需要约20个clock周期,而Bram的rsta_busy复位只需3个clock。值得注意的是,Vivado的FIFO复位后数据会被清零,而Bram复位后数据保持不变。

文章对比了Vivado和ISE工具中FIFO与Bram复位信号的时序行为。在Vivado中,FIFO的wr_rst_busy复位需要约20个clock周期,而Bram的rsta_busy复位只需3个clock。值得注意的是,Vivado的FIFO复位后数据会被清零,而Bram复位后数据保持不变。

////

图1:Vivado的fifo复位信号使能后,wr_rst_busy复位需要经过约20个clock才能结束;这个与ISE的FIFO复位所需时钟周期数的差异很大;

说明:FIFO复位后,缓存的数据被清零。

////

1787

1787

2874

2874

821

821

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?