BUG描述

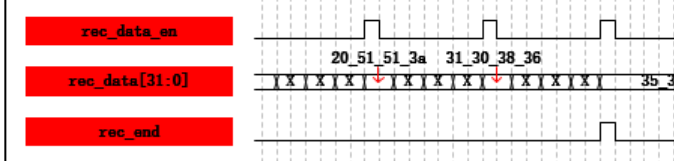

在写以太网时,时常会不自觉地把收尾信号跟FIFO存储信号混为一谈,导致最后一个信号的接收出现严重的BUG:

就像上图这样,最后的收尾标志信号与FIFO写入信号重合,导致最后的信号无法正常读出。

如上图所示,但结束信号与最后的读取信号同时到达时,就不会有正常的enable信号产生。

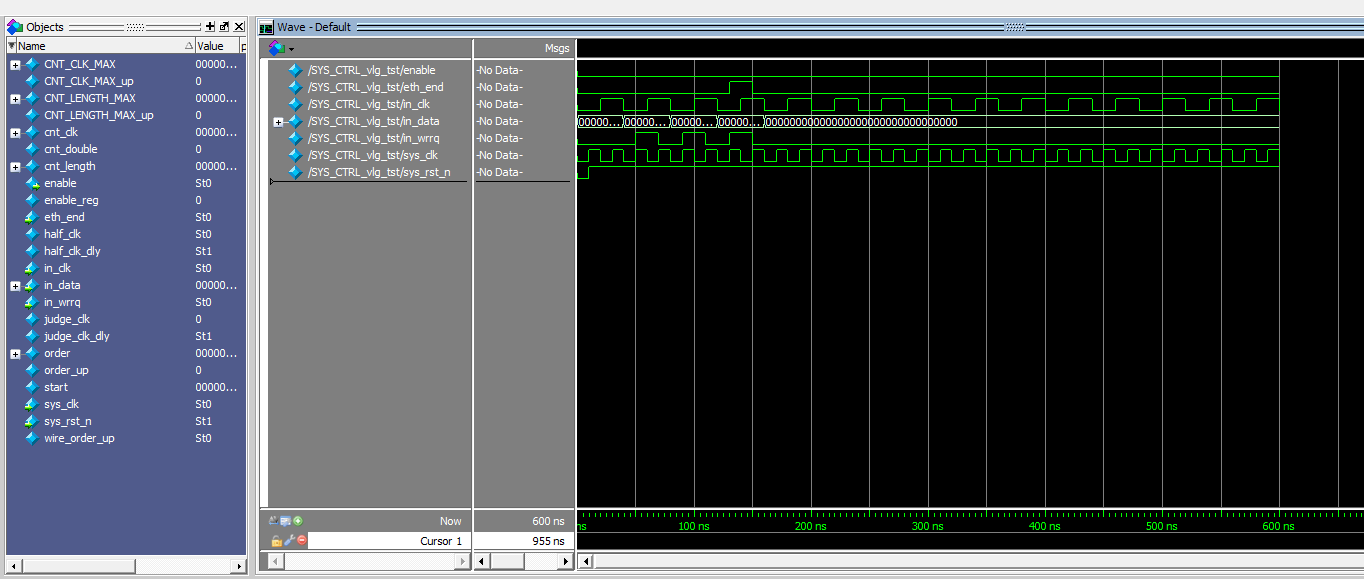

解决方案

将终止标志信号向后延申两个周期即可。

module Signal_Dly_T

(

input wire sys_rst_n,

input wire signal_clk,

input wire signal,

output wire signal_dly_t

);

reg signal_dly;

reg signal_dly_dly;

assign signal_dly_t = signal_dly_dly;

//signal_dly

always@(negedge signal_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

signal_dly <= 1'b0;

else

signal_dly <= signal;

//signal_dly_dly

always@(negedge signal_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

signal_dly_dly <= 1'b0;

else

signal_dly_dly <= signal_dly;

endmodule

添加这样的工具,就可以使信号延后。

文章描述了一个在编写以太网代码时常遇到的问题,即收尾信号与FIFO存储信号混淆,导致最后一个信号接收错误。解决方案是通过延迟终止标志信号两个周期,确保不会与读取信号同时到达,从而保证正常的enable信号产生。实现方法是使用一个信号延迟模块Signal_Dly_T来延迟信号。

文章描述了一个在编写以太网代码时常遇到的问题,即收尾信号与FIFO存储信号混淆,导致最后一个信号接收错误。解决方案是通过延迟终止标志信号两个周期,确保不会与读取信号同时到达,从而保证正常的enable信号产生。实现方法是使用一个信号延迟模块Signal_Dly_T来延迟信号。

1052

1052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?