01/技术背景与必要性

随着半导体技术节点向28纳米以下持续缩小,仅依靠光学邻近效应修正(OPC)已无法满足光刻分辨率和工艺窗口的要求。在28纳米及以上技术节点,通常采用固定形状光源(如环型、双极型等),并基于既定光源通过OPC修正掩模形状。但当技术节点推进至14纳米及以下时,图形尺寸逼近193纳米浸没式光刻的物理极限,传统光源难以提供足够工艺窗口,光源掩模协同优化(SMO)技术应运而生。

02/SMO的基本概念与必要性

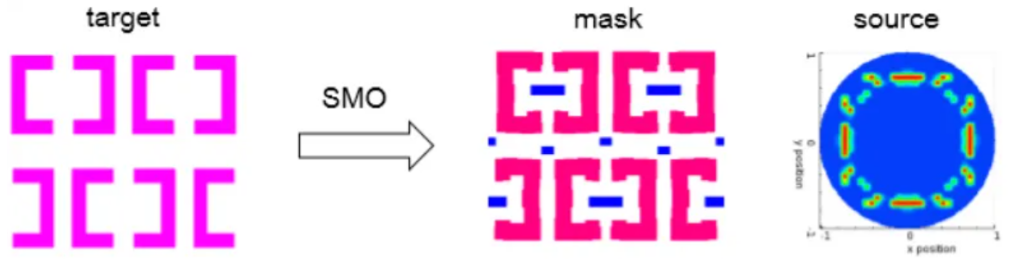

光源掩模协同优化(SMO)是面向极小尺寸图形光刻的核心分辨率增强技术,核心目标是通过同步优化光刻工艺中的光源与掩模参数,改善超小尺寸技术节点的光刻工艺窗口与光学成像表现。

在28纳米及以上技术节点,光刻工艺通常采用环形、双极型等固定形状光源,光学邻近效应校正(OPC)技术仅需基于既定光源对掩模形状进行修正,即可满足工艺需求。但当技术节点推进至14纳米及以下时,图形尺寸逼近193纳米浸没式光刻的物理极限,传统固定光源已无法提供足够工艺窗口,此时SMO技术成为破解这一瓶颈的有效方案。

03/关键技术要素

关键图形筛选

由于SMO需覆盖整块芯片,对所有图形直接优化耗时巨大,因此需通过关键图形筛选技术提前剔除重复或冗余图形。ASML Brion团队开发的基于频谱分析的图形筛选方法具有代表性:通过分析图形衍射级次,优先选择小节距图形作为计算对象,确保筛选出的关键图形能在频谱上代表所有输入图形,大幅降低计算复杂度。

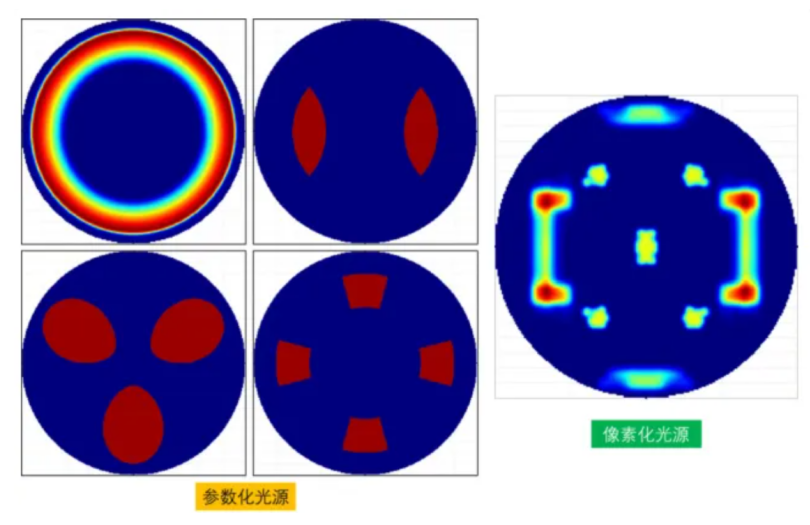

光源表征方法

- 参数化表征:通过定制化参数描述光源,参数少、优化自由度低,但优化速度快,适用于生成简单定制化光源。

- 像素化表征:将光源划分为若干像素块,通过优化每个像素的点亮状态和强度实现复杂光源设计,自由度高但优化效率低,需依赖高效优化算法。

两种表征的光源可通过衍射光学元件(DOE)或FlexRay组件实现。

掩模表征方法

- 多边形表征:将掩模图形分解为多个多边形组合分别优化,速度快但自由度有限。

- 像素化表征:将掩模分解为细小像素方块,可实现精细优化,但自由度呈指数增长,对优化算法要求更高。

04/优化过程与工作流程

优化过程(基于边缘放置误差EPE)

在仿真中,于图形的边、角按规则插入评估点,对各照明条件下的EPE加权求和形成成本函数。通过迭代修饰光源和掩模,使成本函数值最小,直至相邻优化结果差异小于预设值(收敛标准)。

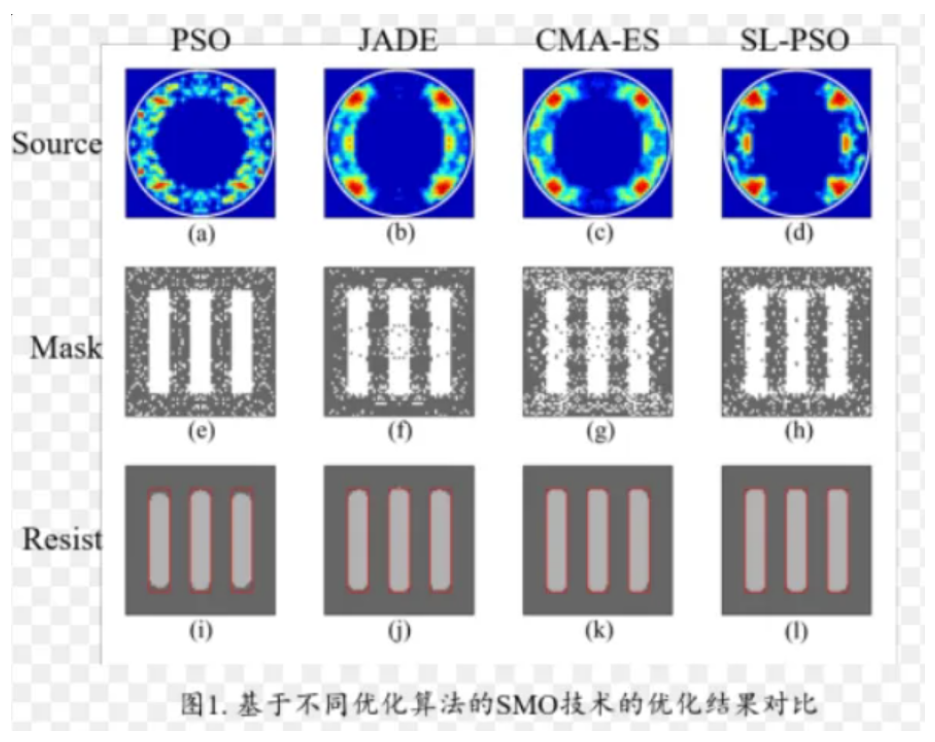

优化算法分为两类:

- 梯度优化算法:基于光刻模型梯度信息优化,速度快但易陷入局部最优。

- 启发式优化算法:结合多种机制保障全域最优,但效率较低。

工作流程

1. 图形选择:用测试图形(如through pitch线宽、尖端对尖端等)结合SRAM结构和工艺弱點,通过频谱分析筛选关键图形。

2. 仿真计算:建立光刻仿真条件(机台信息、照明方式、薄膜堆栈等),开展SMO计算。

3. 优化与验证:以重叠工艺窗口(DOF、EL、MEEF、ILS等指标)为评价标准;若满足需求,进行掩模优化验证(OPC模拟+晶圆数据比对);若发现新弱点,迭代优化直至符合要求。

05/重要性与应用前景

SMO通过协同优化光源和掩模,大幅提升光刻工艺窗口指标(DOF、EL、MEEF等),为14纳米及以下技术节点芯片量产提供了坚实基础。同时,SMO仿真可获取图形极限值(最小节距、最小尖端距离等),为设计规则制定和工艺优化提供依据。

在先进制程中,SMO的成功实施需要SMO、OPC、设计、工艺等多领域人员紧密协作,是推动芯片制造技术持续进步的关键手段。

4019

4019

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?