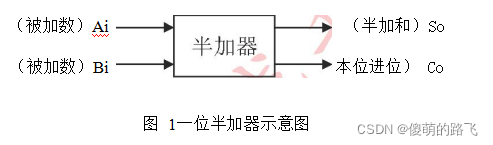

目的:用VHDL文本输入法设计并实现一个一位半加器。

程序(使用quartus II软件进行编写)

library ieee;

use ieee.std_logic_1164.all;

entity add1_half is

port(

Ai,Bi :in std_logic;

So,Co :out std_logic --So半加和,Co进位输出

);

end add1_half;

architecture behave of add1_half is

begin

process(Ai,Bi)

begin

So <= Ai xor Bi;

Co <= Ai and Bi;

end process;

end behave;

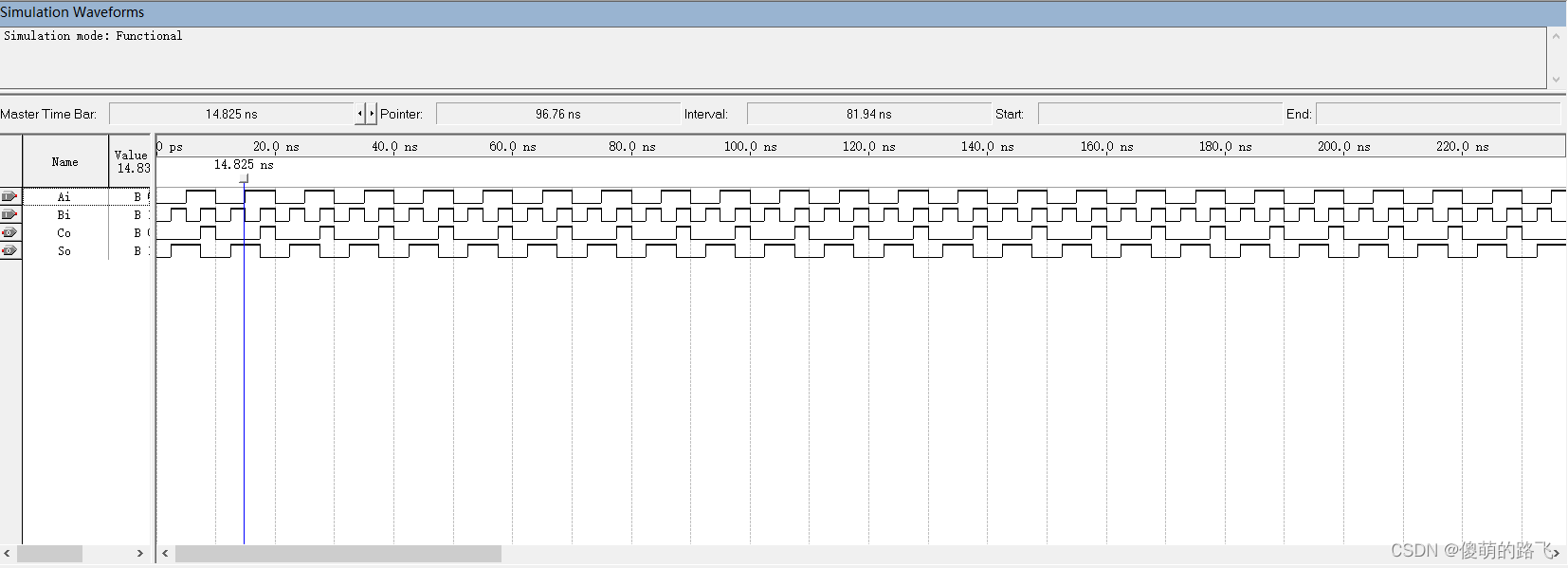

仿真波形图

本文介绍了一种使用VHDL语言设计一位半加器的方法。通过Quartus II软件实现,并详细展示了VHDL源代码。该设计包括两个输入端口Ai和Bi,以及两个输出端口So(半加和)和Co(进位输出)。文章还提供了仿真波形图验证了设计的正确性。

本文介绍了一种使用VHDL语言设计一位半加器的方法。通过Quartus II软件实现,并详细展示了VHDL源代码。该设计包括两个输入端口Ai和Bi,以及两个输出端口So(半加和)和Co(进位输出)。文章还提供了仿真波形图验证了设计的正确性。

1951

1951

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?