遇到一个项目需要用ZYNQ做一个高精度差分同步采集系统,查了下资料貌似网上大多是做单双通道,或者16位AD7606这种多路复用单端输入的ADC,看来得自己搞了,记录一下开发过程。

- ADC选型

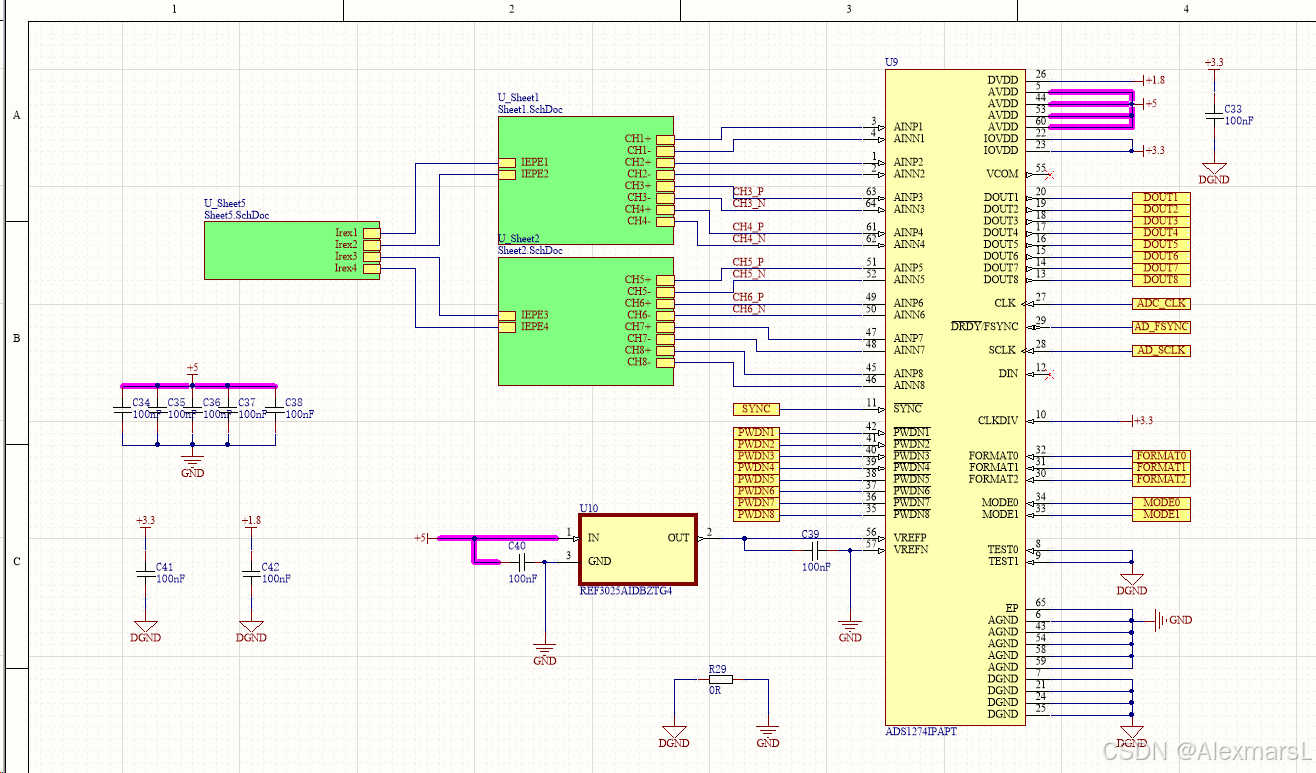

直接打开立创官网开条件筛选,挑了一款TI的ADS1278看了下性能指标价格还行,于是赶紧搜索有没有开源驱动代码,chrom一搜没想到还真有,直接开搞 - 硬件设计

根据数据手册,ADC外围电路比较常规,除电源外没有特殊设计的地方,接口方面除了TEST两个接口没用可接地之外其他接口直接连接FPGAIO。

- 软件设计

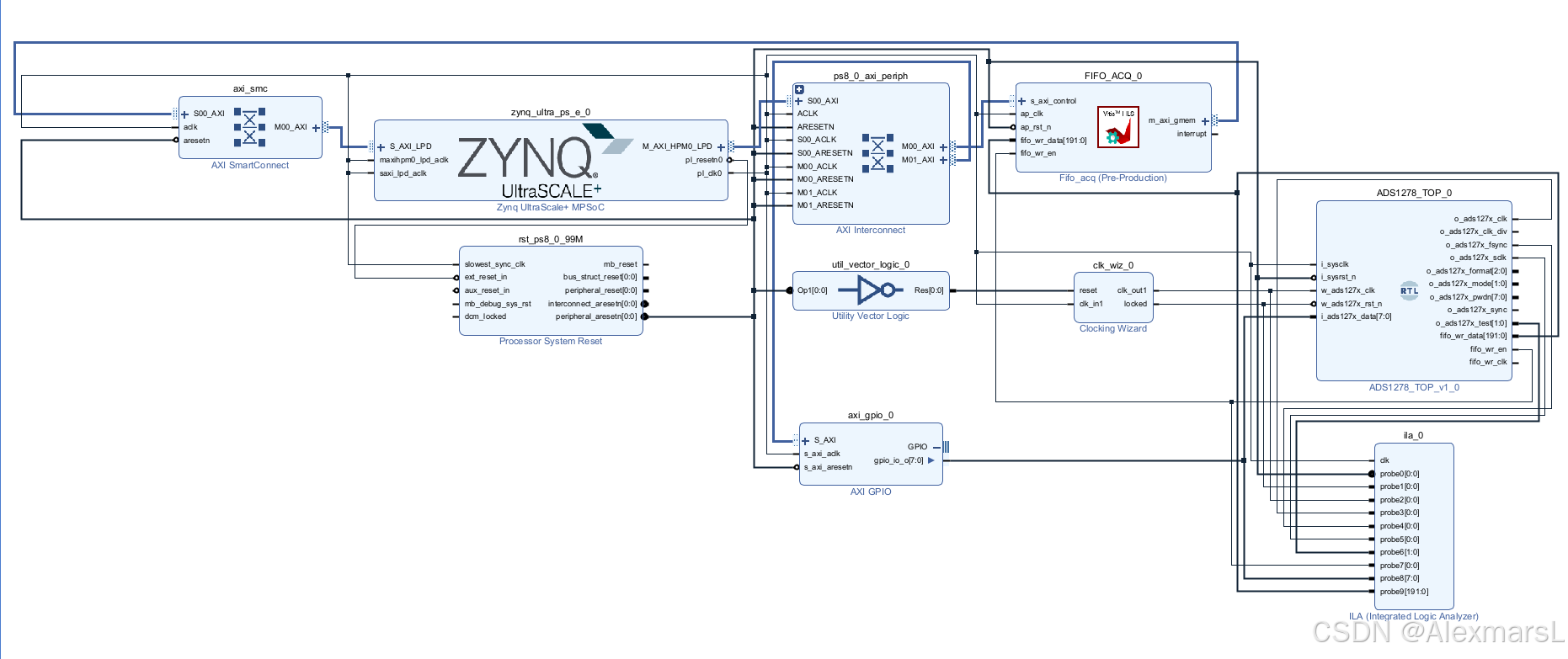

ADC驱动部分:DATASHEET里说道数据有串行或者同步传输,既然做同步采集那肯定是用并口获取数据了,代码是开源的,我根据我的需求修改了一下这里贴一下顶层

module ADS1278_TOP( input i_sysclk , input i_sysrst_n , input w_ads127x_clk , input w_ads127x_rst_n , // 外部锁定信号输入 output o_ads127x_clk , output o_ads127x_clk_div , output o_ads127x_fsync , output o_ads127x_sclk , input [7 :0] i_ads127x_data , output [2 :0] o_ads127x_format , output [1 :0] o_ads127x_mode , output [7 :0] o_ads127x_pwdn , output o_ads127x_sync , output [1 :0] o_ads127x_test , // 添加 FIFO 写端口 output [191:0] fifo_wr_data, // FIFO 写数据 output fifo_wr_en, // FIFO 写使能 output fifo_wr_clk // FIFO 写时钟 // input fifo_wr_full // FIFO 写满标志(可选 ); /***********************网线型**************************/ wire w_sysrst_n ; /***********************例 化**************************/ arsf_module arsf_module_u0( //复位处理:异步复位,同步释放 .i_sysclk (i_sysclk ), .i_sysrst_n (i_sysrst_n ), .o_rst_n (w_sysrst_n ) ); /******************************************************/ wire [191 : 0] w_ads1278_rdata ; wire w_user_rdata_valid; wire w_user_rdata_ready; assign w_user_rdata_ready = w_user_rdata_valid; /******************************************************/ ads1278_drive#( .P_ADS127X_MODE (2'b01 ), //模式设置参数 0-快速 1-精准 2-低功耗 3-超低速 .P_ADS127X_PWDN (8'b1111_1111 ) //通道开关参数 1-开启 0-关闭 ) ads1278_drive_u0 ( .i_sysclk (i_sysclk ), //输入系统时钟 .i_sysrst (~w_sysrst_n ), //输入系统复位 .w_ads127x_clk (w_ads127x_clk) , .w_ads127x_rst_n (w_ads127x_rst_n), // 外部锁定信号输入 .o_ads127x_clk (o_ads127x_clk ), //ADS127X芯片驱动时钟 .o_ads127x_clk_div (o_ads127x_clk_div ), //ADS127X芯片时钟分频设置 .o_ads127x_fsync (o_ads127x_fsync ), //ADS127X芯片帧同步(AD转换控制) .o_ads127x_sclk (o_ads127x_sclk ), //ADS127X数据时钟 .i_ads127x_data (i_ads127x_data ), //ADS127X的8通道数据输入 .o_ads127x_format (o_ads127x_format ), //ADS127X通信格式设置 .o_ads127x_mode (o_ads127x_mode ), //ADS127X工作模式设置 .o_ads127x_pwdn (o_ads127x_pwdn ), //ADS127X通道开关 .o_ads127x_sync (o_ads127x_sync ), //ADS127X多片同步 .o_ads127x_test (o_ads127x_test ), //ADS127X测试模式设置 // 添加 FIFO 写端口 .fifo_wr_clk (fifo_wr_clk), // FIFO 写时钟 .fifo_wr_data (fifo_wr_data), // FIFO 写数据 .fifo_wr_en (fifo_wr_en) // FIFO 写使能 ); endmoduleBD设计:因为要用ZYNQ传PS处理,所以要进行block design,基本思路是RTL部分采集然后FIFO暂存通过AXI传输至PS端,RTL采集代码直接拖进BD,因为我比较懒不想写verilog仿真测试验证了,PL与PS互联这里我直接用HLS封装了一个FIFO和MAXI接口的IP核,为了方便调试查问题,生成了一个ILA抓波形,然后在输出端添加了一个AXI GPIO控制输出模拟数据给AD采集,最后生成比特流准备上开发板测试。

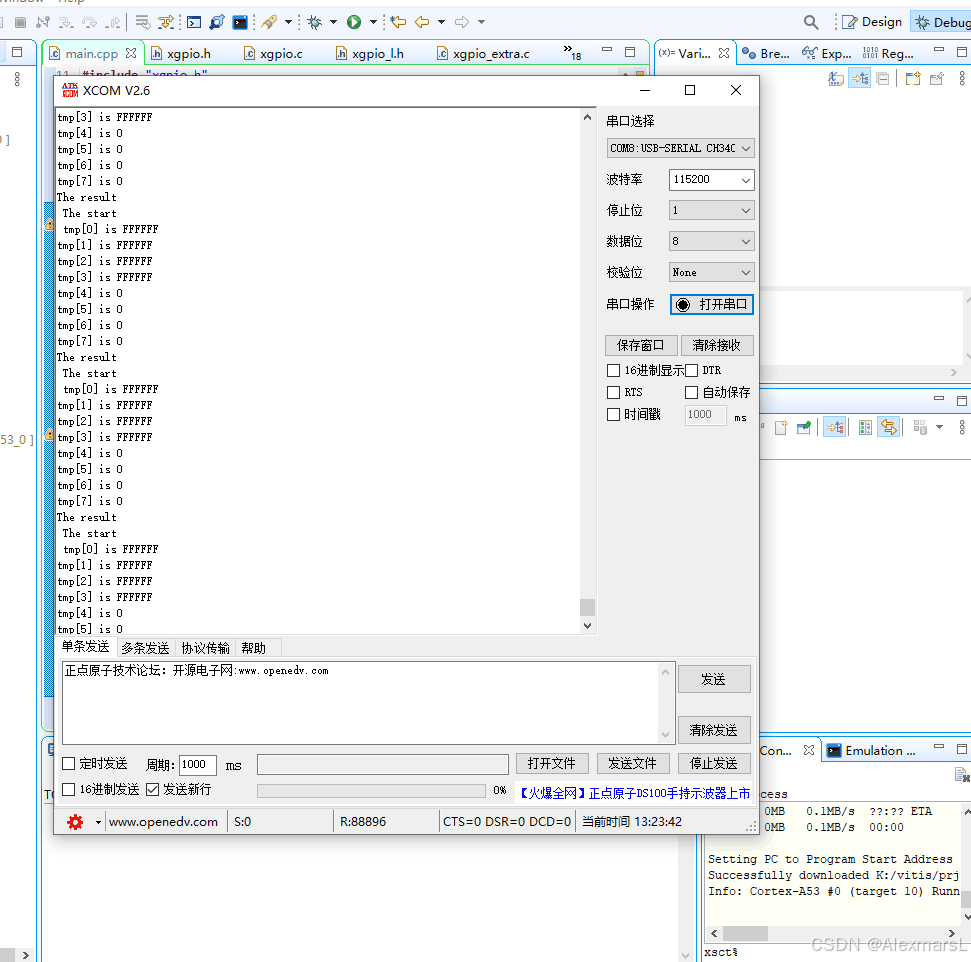

VItis测试:常规开发流程,先配置IP核 ,启动AXI GPIO输出,AXI GPIO输出8位数据0X0F,也就是说AD驱动端采到数据前四个通道是0后四个是FFFF -

XGpio axi_gpio_inst; //PL 端 AXI GPIO 驱动实例 XGpioPs Gpio; //=========输入========= XGpio_Initialize(&axi_gpio_inst, AXI_GPIO_ID); XGpio_SetDataDirection(&axi_gpio_inst, 1, 0); XGpio_DiscreteSet(&axi_gpio_inst, 1, 0x0F);

打开串口,打印输出查看数据 果然与预期一直

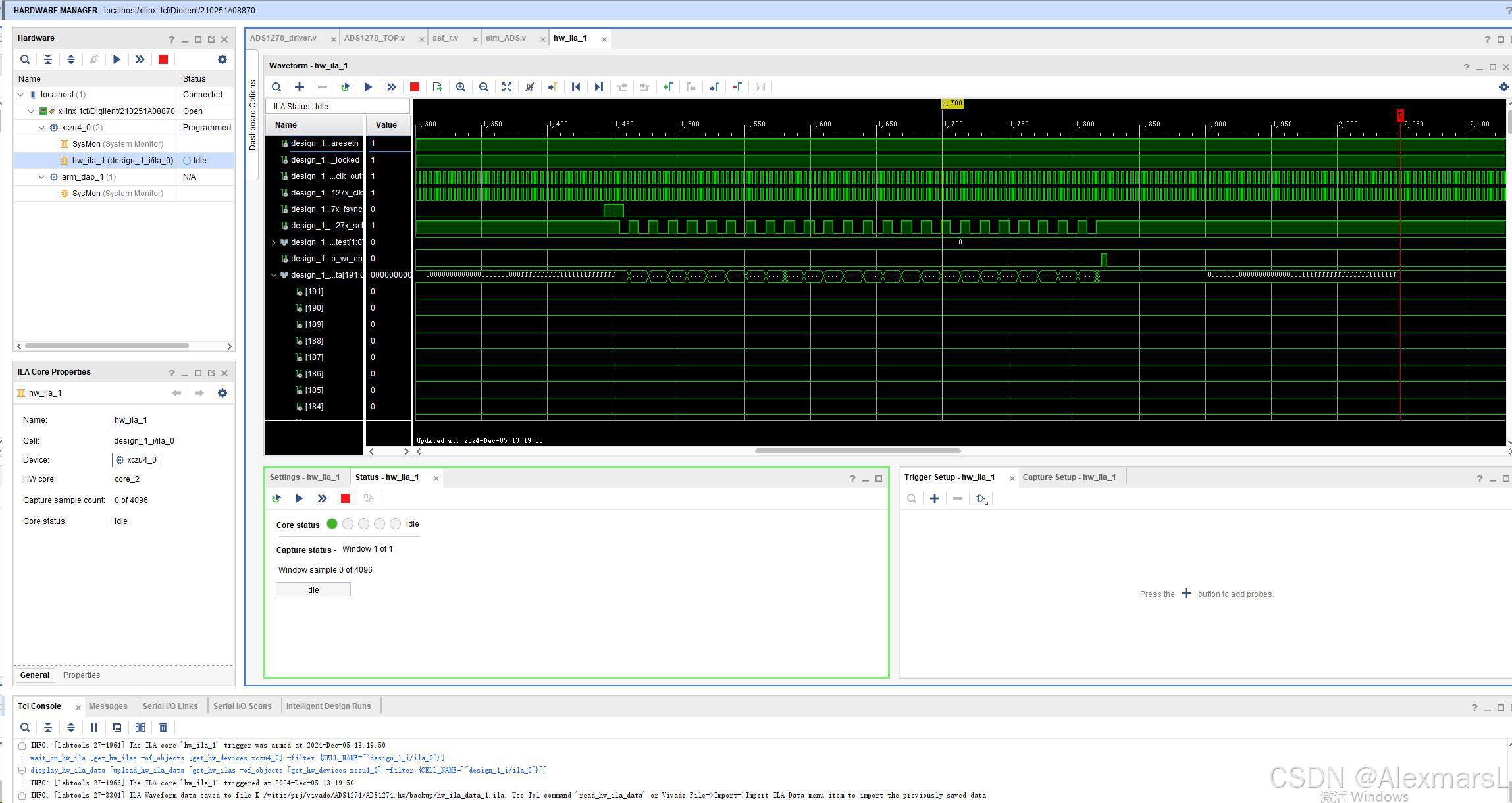

再查看一下抓到的波形,没问题和数据手册时序一直

5.硬件测试

未完待续,等硬件打板回来实测

---------------------------------------------------------------------分割线---------------------------------------------------经过各种debug调试,调试结果如下

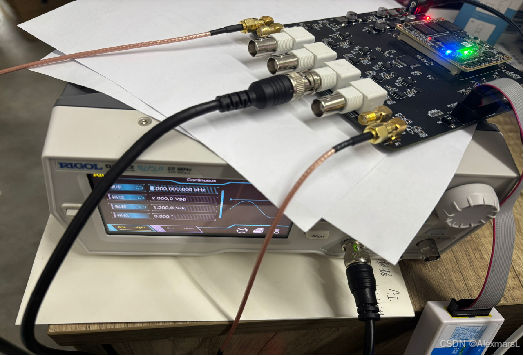

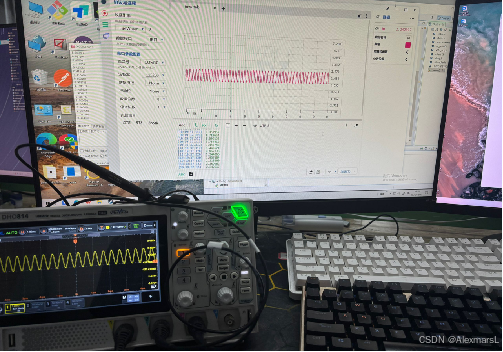

硬件设计的是底板+核心板结构,核心板用的正点原子7020,测试时候用了个函数发生器产生的正弦波给AD采,结果如下

用示波器打了一下,上位机用的伏特加串口示波器,采到的数据从PS端的串口实时输出。

1万+

1万+