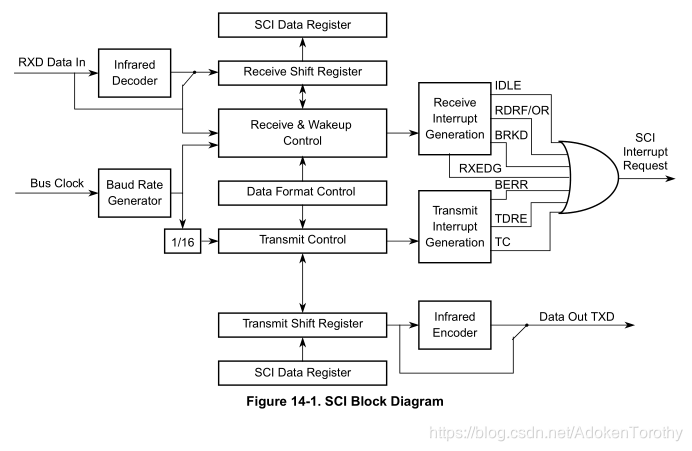

SCI 是全双工异步串行通信接口,主要用于 MCU 与其他计算机或设备之间的通信,几个独立的 MCU也能通过 SCI 实现串行通信,形成网络。 MC9S12XS128里有两个SCI(SCI0和 SCI1) 。设计 SCI 串口通信程序,主要是掌握八个寄存器,设置好初始化。

以下为SCI相关寄存器:

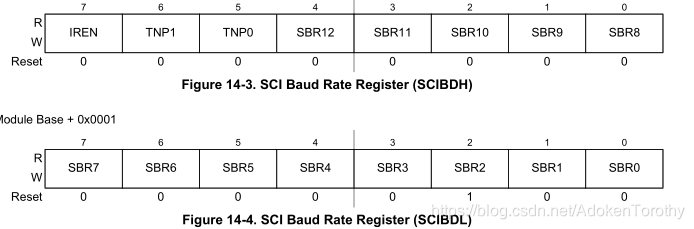

SCIBDH, SCIBDL寄存器

IREN(红外调制模式使能位) = 1 时,使能

= 0 时,禁止

TNP[0:1]:窄脉冲发射位

SBR[0:12]:波特率设置位

IREN = 1 时,SCI baud rate = SCI bus clock / (16 x SBR[12:0])

IREN = 0 时,SCI baud rate = SCI bus clock / (32 x SBR[12:1])

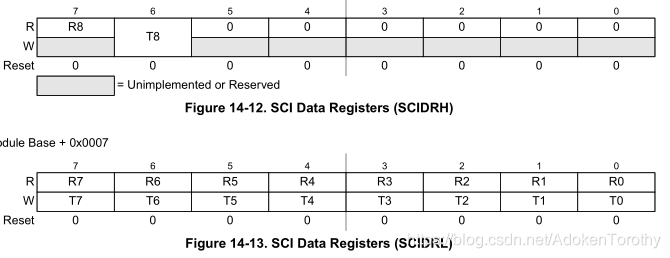

SCIDRH, SCIDRL寄存器

SCI 内部分别设有发送和接收两个数据寄存器,其低位都通过 SCIDRL 访问,读操作返回接收数据寄存器 RDR 的内容,写操作数据置入发送数据寄存器TDR。当 M=1 即运行在 9 位数据模式时,SCIDRL 和 SCIDRH 形成 9 位的 SCI数据字,这时必须先写入 SCIDRH,以便与低位字节(SCIDRL)一起进入发送移 位器。如果 M=0 即 SCI 只用于 7 位或 8 位的数据传送,可以只访问 SCIDRL。 当 PE=1 即奇偶校验允许时,奇偶校验位由硬件负责,无需软件干预。

R8:接收到的位 8,该位写操作无效。当 SCI 设置成 9 位数据运行模式时,该位是从串行数据流中接收到的第 9 位。

T8:发送位 8,任何时候可写。当 SCI 设置成 9 位数据模式时,该位是送到串行 数据流的第 9 位。该位不必为每个数据重新设置,每次发送可重复使用。

R[0…7]T[0…7]:收/发数据位 7-0,读操作返回只读寄存器 RDR 的内容,写操 作写入只写寄存器 TDR。

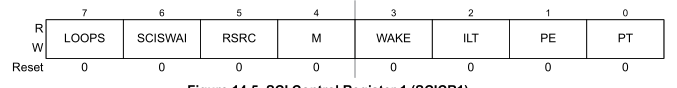

SCICR1寄存器

LOOPS: 在LOOP模式下,RXD引脚与SCI接收部分断开,发射部分输出在内部和接收部分相连接,此时RXD可作为普通IO口,TXD输出SCI信号

= 1 时, LOOP模式使能

= 0 时, 正常模式

SCISWAI:等待模式下 SCI 停止位

= 1 时:在等待模式下禁止 SCI

= 0 时:在等待模式下允许 SCI

RSRC:接收器信号源选择位,当 LOOPS=1 时,RSRC 决定接收器的内部反馈信号路径

= 1 时,接收器的输入连接到 TxD 引脚

= 0 时,接收器的输入在内部连接到发送器输出(并非 TxD 引脚)

M:方式选择位(选择字

本文详细介绍了SCI(Serial Communication Interface)在MCU中的应用,特别是在MC9S12XS128型号中如何配置和使用SCI0和SCI1进行串行通信。内容包括SCI的相关寄存器配置,如SCIBDH、SCIBDL、SCIDRH、SCIDRL等,以及中断接收的相关设置。文中提到SCI的波特率计算、数据传输模式,并提供了SCI中断接收的代码实现。通过USB转串口模块与电脑进行通信,实现了发送特定字符控制指示灯亮灭的功能。

本文详细介绍了SCI(Serial Communication Interface)在MCU中的应用,特别是在MC9S12XS128型号中如何配置和使用SCI0和SCI1进行串行通信。内容包括SCI的相关寄存器配置,如SCIBDH、SCIBDL、SCIDRH、SCIDRL等,以及中断接收的相关设置。文中提到SCI的波特率计算、数据传输模式,并提供了SCI中断接收的代码实现。通过USB转串口模块与电脑进行通信,实现了发送特定字符控制指示灯亮灭的功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1360

1360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?