写在前面:这门课程不是核心课,但是实验过程较为复杂、耗时较长,本次实验我的完成情况较好,可以提供一定的参考价值

一、日志

1.1 3 位数码管实验下载到实验板上的操作说明以及现象描述 :

【操作说明】

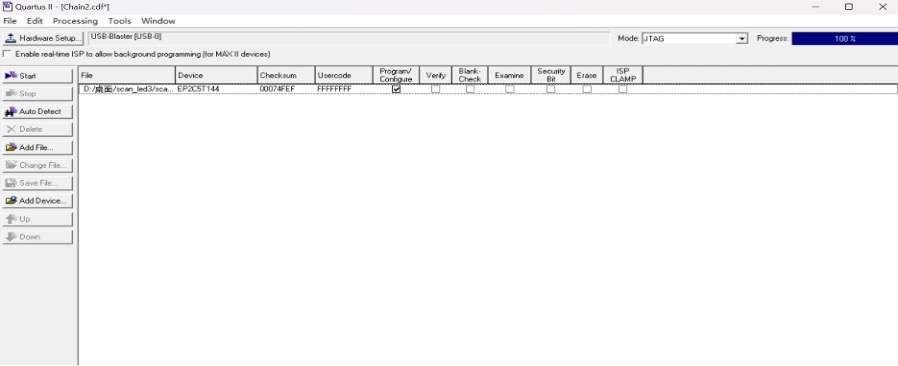

首先在课前提前将Quartus II软件、USB 硬件驱动安装好,然后将下载电缆线与 USB 接口连接。打开 Quartus II,点击Tools,再进入 Programmer 命令,单击【Add File】添加下载好的【scan_led3.sof】,单击【Hardware setup】进入配置窗口,然后在硬件列表中选择【USB_Blaster】,点击 Start,加载 100%后观察实验板。

【现象描述】

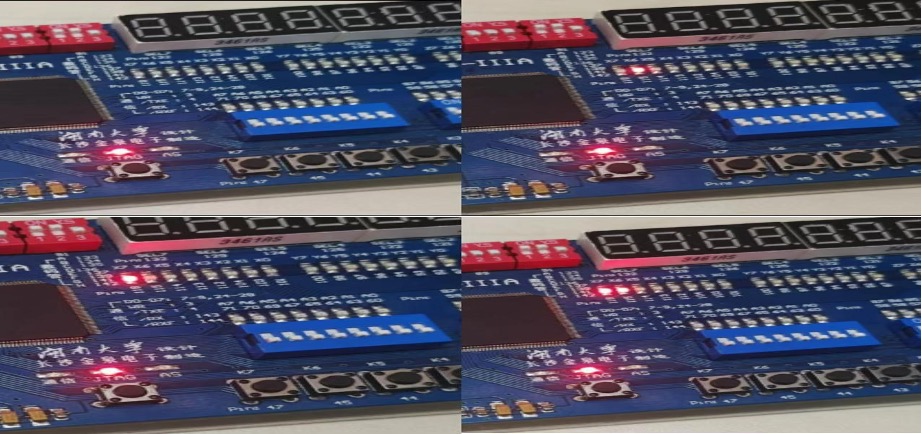

实验板上方的SEL5-7数码管显示字符“0”,并且持续闪烁,熄灭的时间极短。下方的X0和Y7保持闪亮。分别拨动CLK的第一个开关,第二个开关,第三个开关,数码管闪烁频率加快,同时打开第一个和第二个开关,闪烁频率最慢。最下方的A7-A4是上方数码管的控制信号,分别控制的数码管字符为:8、4、2、1。

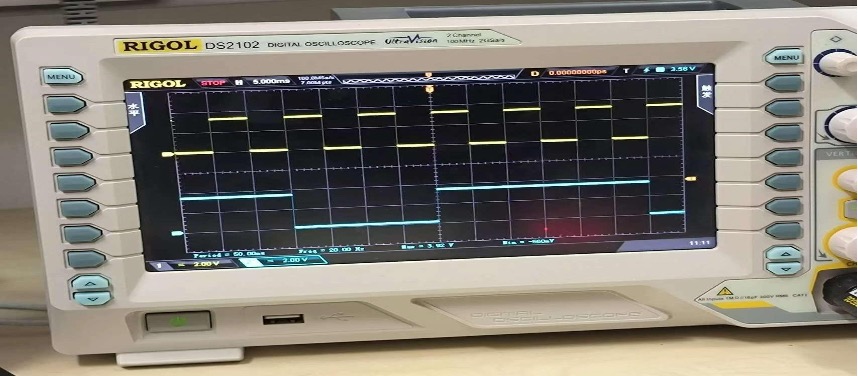

1.2 示波器测量位选信号和时钟信号的截图与文字说明:

本实验使用仪器为:示波器。

黄色信号代表示波器的位选信号,蓝色信号代表示波器的时钟信号,X轴每格刻度具体频率为20Hz。Y轴每格刻度2.00电平。有效电平为3.56V,位选信号的状态都是在时钟信号上升沿发生变化。

二、报告

2.1 实验目的:

目标:

- 完成三位数码管的显示实验,熟悉软件 quartusII 的使用,熟悉 FPGA 开发模式;

- 利用 Quartus II 来实现三位数码管显示电路的逻辑设计,通过仿真波形及硬件实验平台验证设计,掌握硬件实验平台的一系列操作方法,进一步了解三位数码管显示电路的逻辑设计。

- 熟练掌握时钟及位选等信号波形以及多位数码管显示电路由显示字符的段选信号和选通数码管的位选信号控制,深入理解各个信号之间的联系;

- 在 DDA—IIIA 实验平台上完成三位数码管显示实验的观察与测量,进一步加深通过实验板验证电路的方法;资源:

硬件学习板:主芯片为cycloneII ep2c5t144c8,USB下载线,测试仪器:HUAWEI电脑,系统:Windows11,软件工具:Quartus II 版本号:9.0。

2.2 设计:

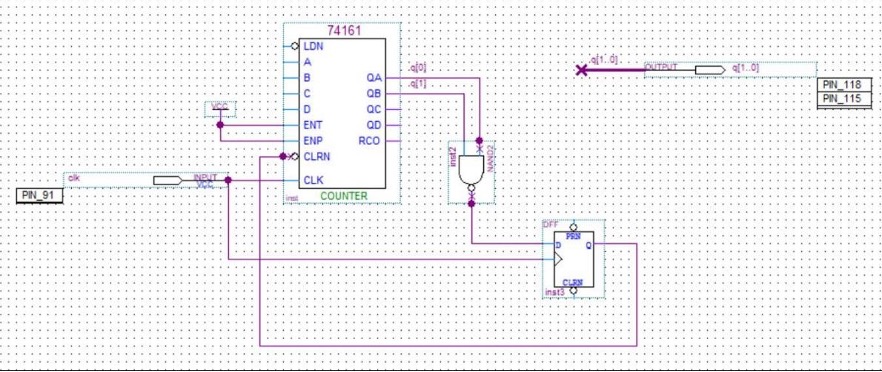

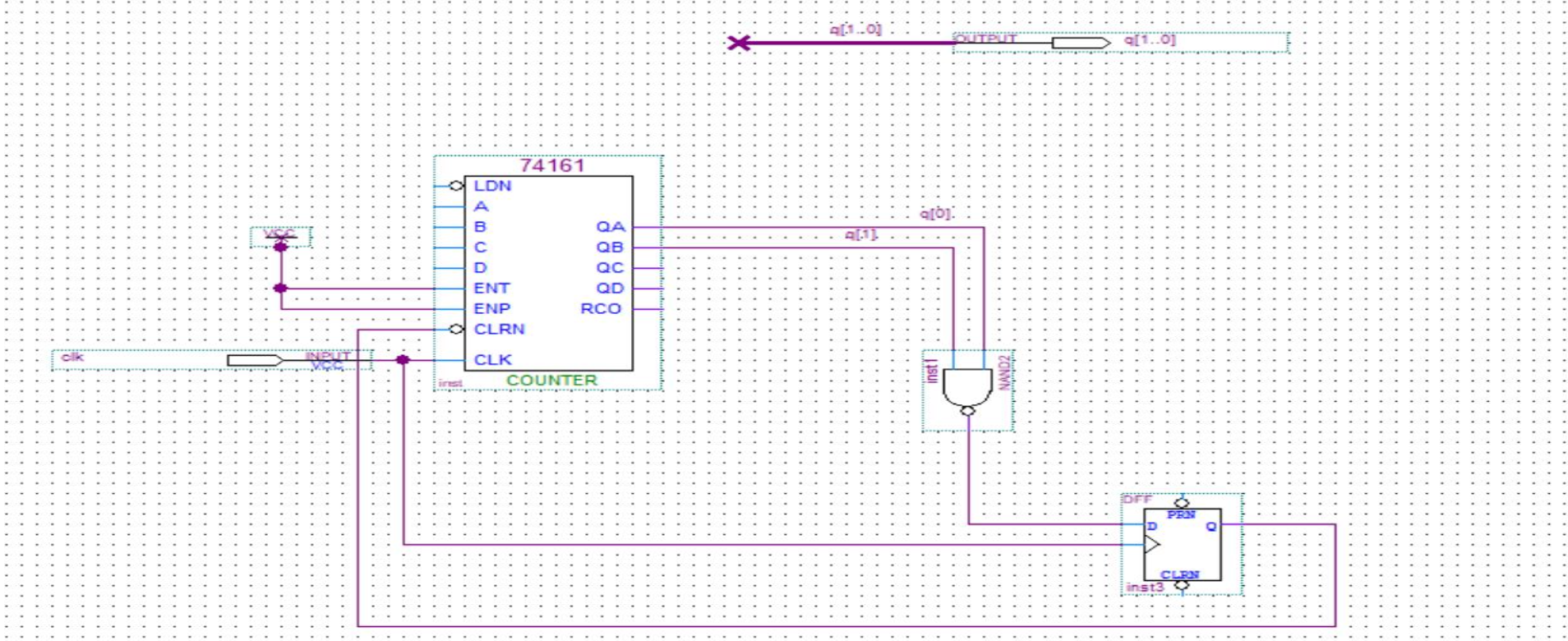

2.2.1模 4 计数器电路图(含管脚分配的)截图与文字说明:

2.2.2 模 4 计数器下载现象描述并举证从验证实验时的现象上如何看出你实现的电路行为正确并下结论:

分析: 1.器件型号,管脚分配情况说明:clk:PIN_91,q[1]:PIN_118,q[0]:PIN_115;

2.调慢时钟输入,在时序仿真的情况下,p[1]和p[0]两个led引脚的发光规律呈现周期性变化,随着时钟上升q[1..0]的输出表现为:(0,0) ->(0,1)->(1,0)->(1,1)->(0,0)往复循环。

结论:上述实验简短总结在下载验证时,若实验结果与所实现的电路行为一致:即设置的两个发光二极管按照分析中给出的周期规律进行 发光,则表明实现的电路行为正确。

2.2.3 比较仿真验证和下载验证 2 种方法:

仿真验证: 分为时序仿真和功能仿真,时序仿真使用布局布线后器件给出的模块和连线的延时信息,虽然较功能仿真具有一定的延时, 但能反映出更加真实的实验状况,而功能仿真则保证在理想条件下的准确性,故更多地使用功能仿真进行试验。整个仿真验证的优点在 于不需要分配引脚,可以简单地改变输入信号。

下载验证: 考虑了实际的模块,需要分配引脚,将电路下载到电路板上才能分析实验的结果,没有仿真验证简易快捷,但下载验证可以 清晰地看到实验结果,并且更为真实。

客观比较分析2种验证方法:二者应该结合着使用,相辅相成,利用仿真的便捷性可以先使用从而快速发现实验的正确与否,再利用下载 验证去分析仿真验证的准确性。

2.3 实践 :

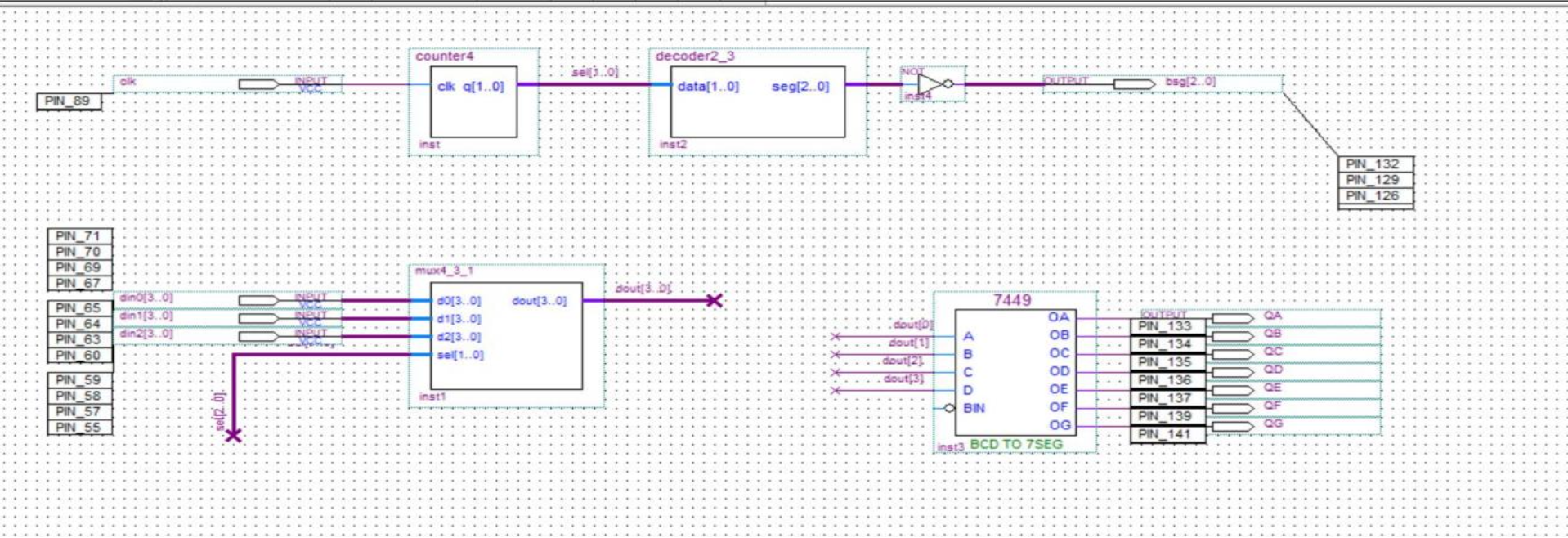

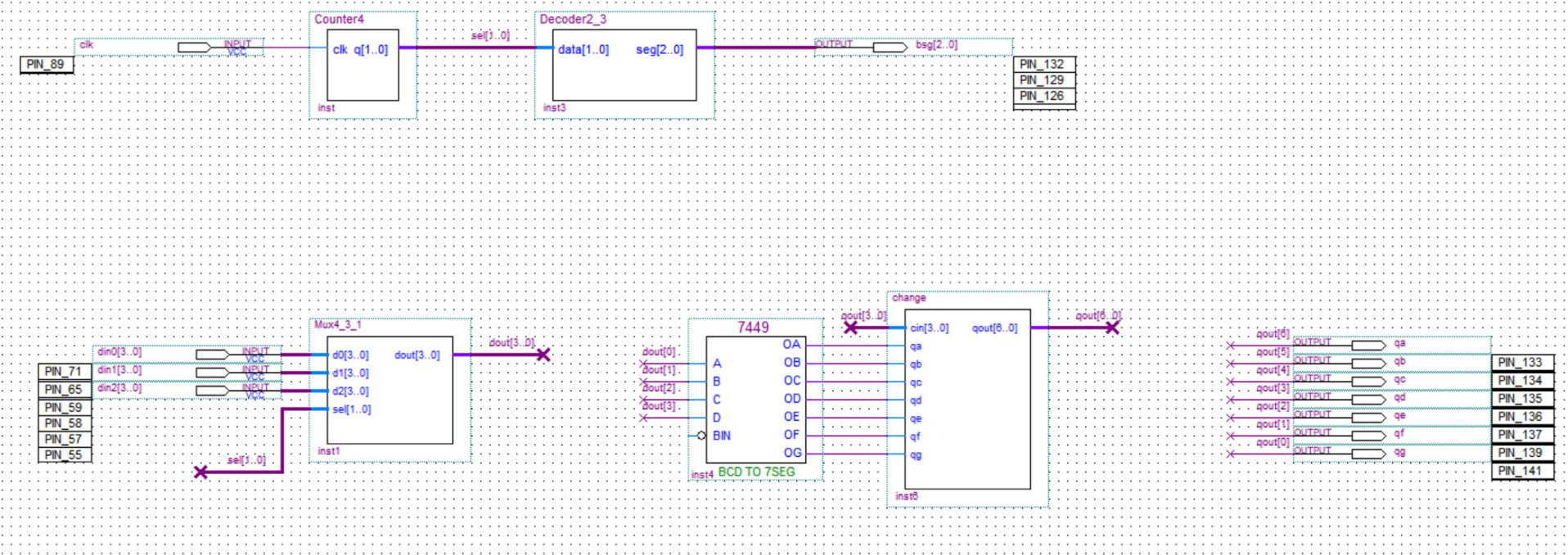

2.3.1 顶层电路截图:

Counter4(模 4 计数器):作为整个电路的主控制模块控制数码管上数据的位选信号以及段选信号的产生,接收时钟信号,产生位选和段选 信号,并将信号传给3选1多路选择器和2-3译码器。

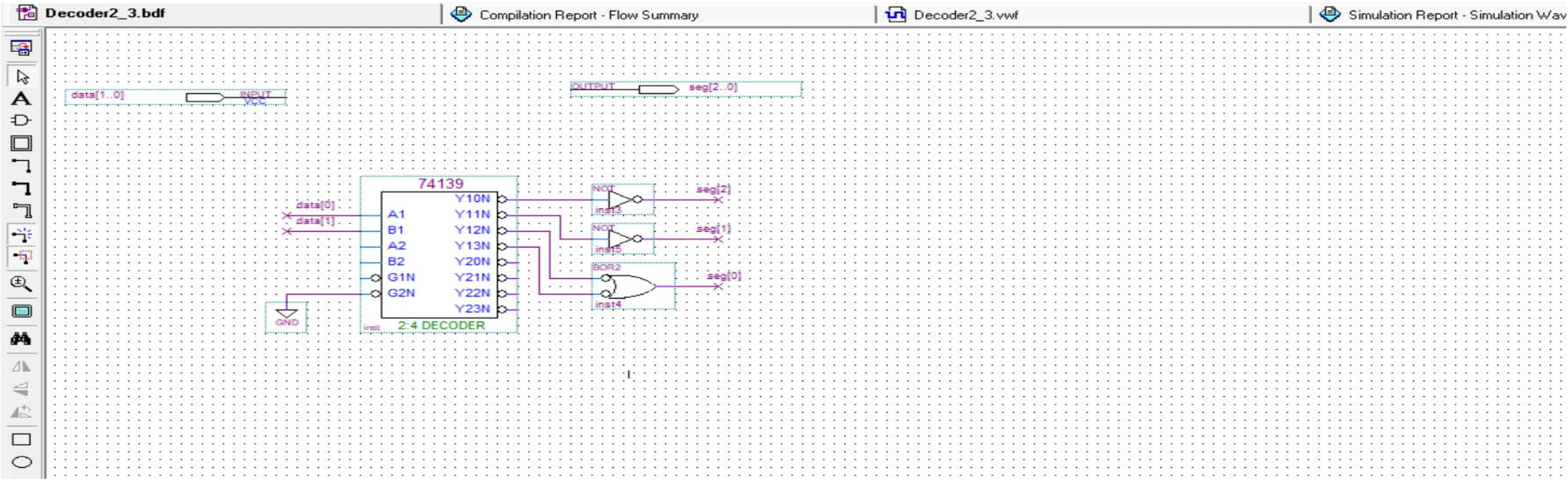

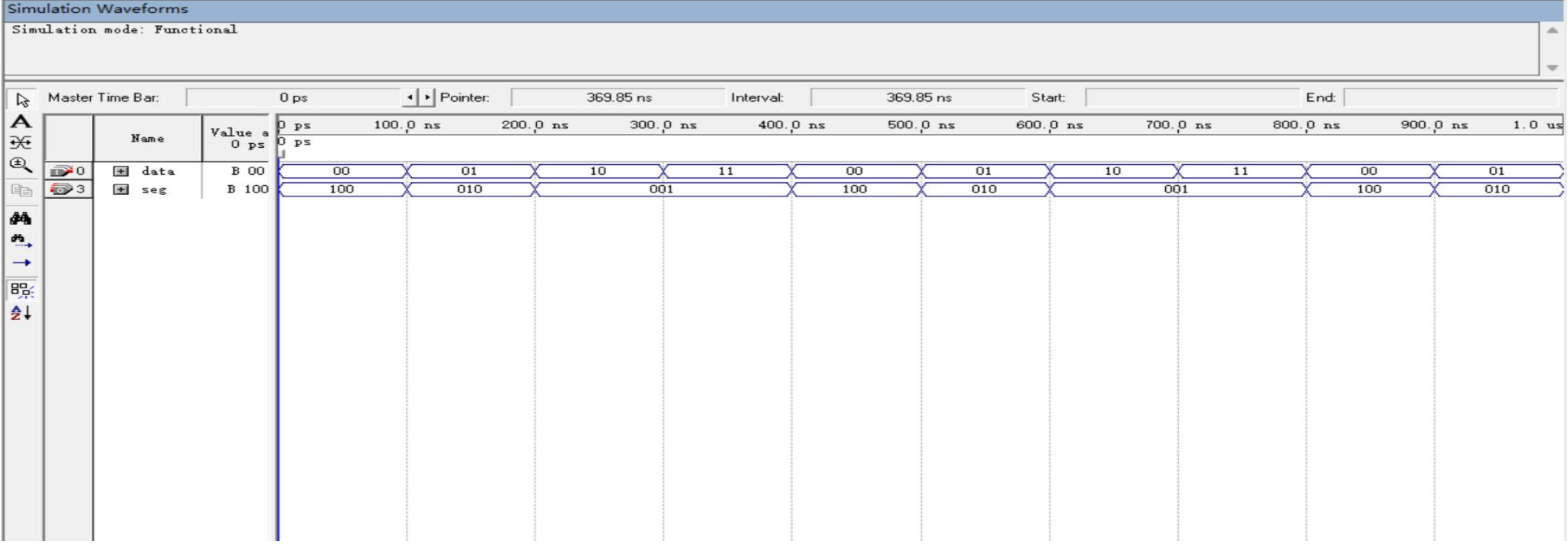

Decoder2-3(2-3 译码器):接受Counter传输过来的信号,产生三位位选信号:个位、十位、百位,控制三位数码管的先后显示;当data为 00时,译出百位,也就是第一个数码管,为01时,译出十位,也就是第二个数码管,11和10时译为个位,也就是第三个数码管。

实现方式:图形法。

波形仿真结果:

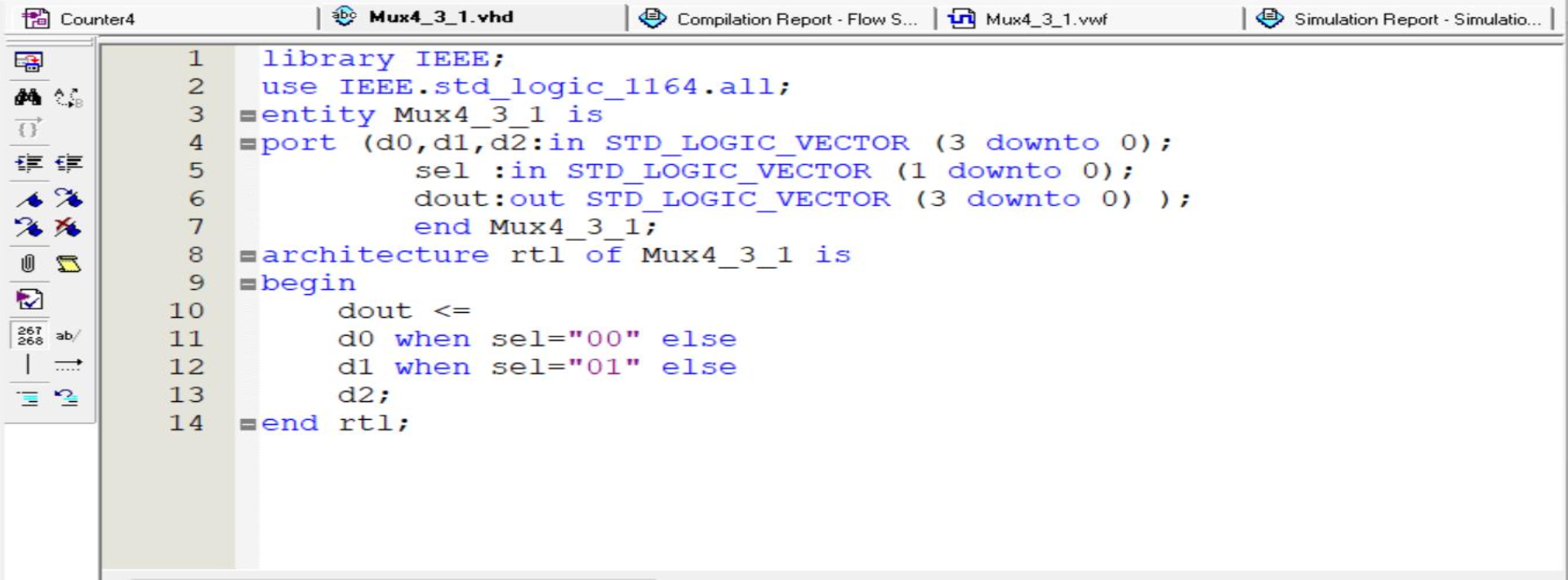

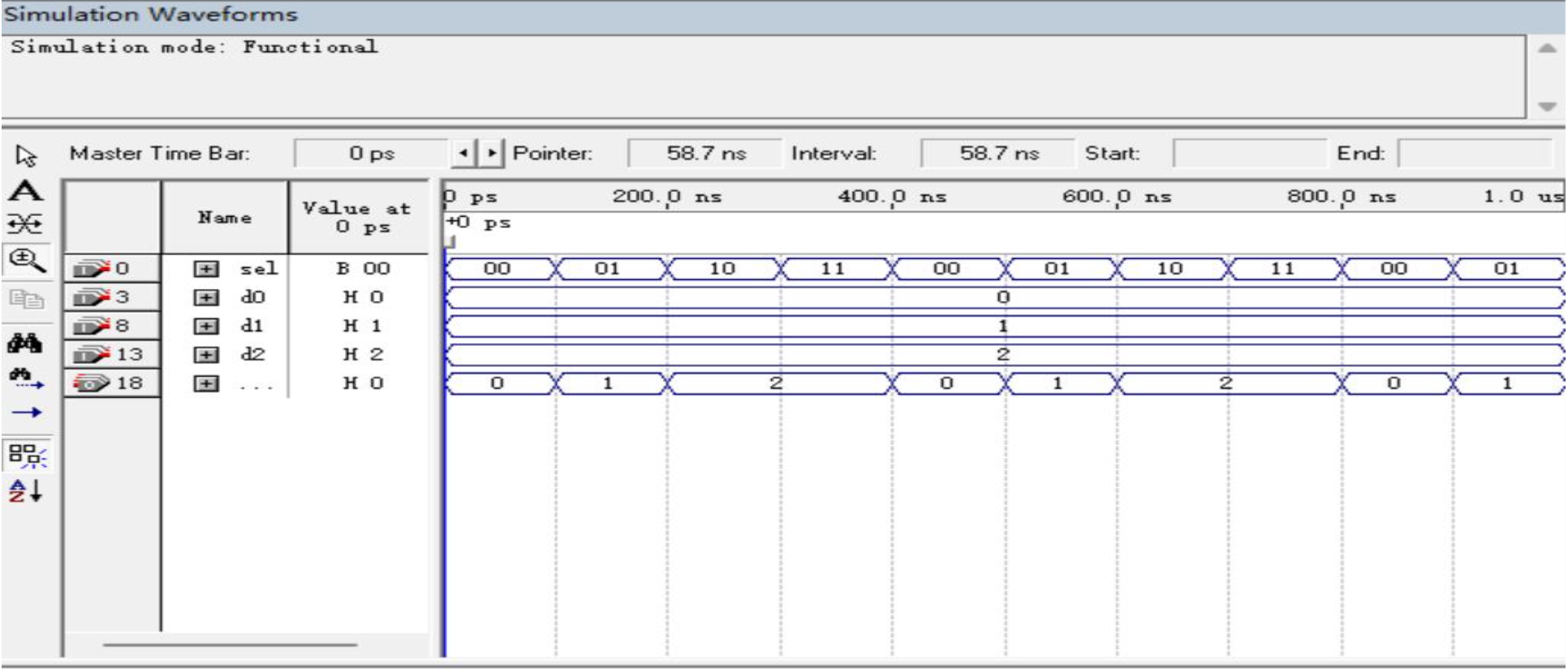

Mux4_3_1(3 选 1 多路复用器):接受Counter4传来的信号,产生段选信号从而显示不同的数字,根据sel信号的输入来决定输出信号,可以 同时输出三路数据和Counter4的信号,从而控制三路四位数据的选择输出。

实现方式:HDL 语言。

波形仿真:

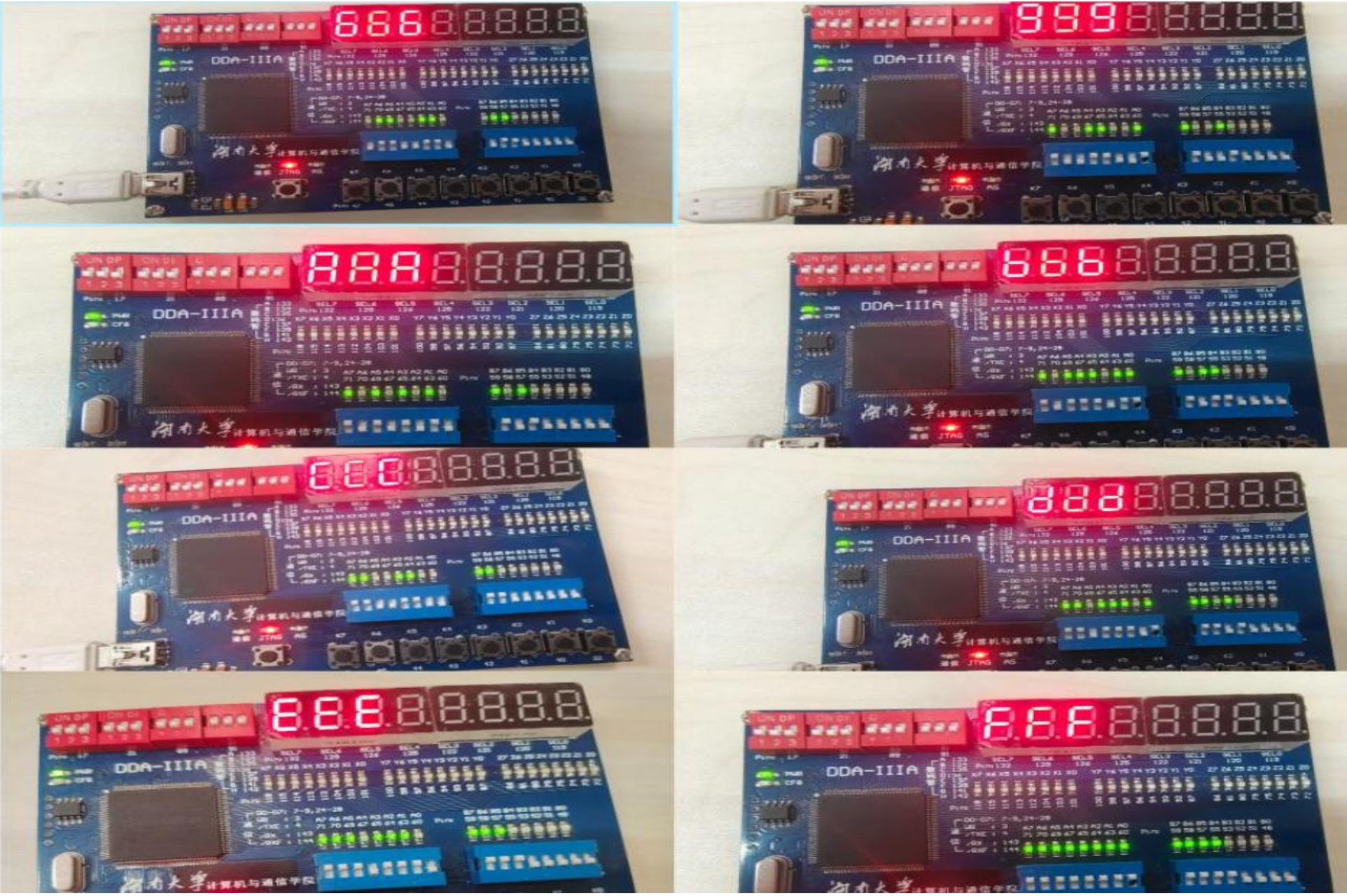

2.3.2 下载实作截图,列表记录输入0-f时,7449译 码符号的显示情况:

2.3.3 顶层电路图中的7449存在“A-F”译码缺陷,请在不删除7449的情况下优化顶层电路图,说明优化的设计思路、实现电路和实验验证:

设计思路:设计出发点:需要改进显示 6,9 以及 a-f 的情况。(6 的情况和 b 的情况重合)具体设计: 简述 思路。

有变化部分:

增加的译码:A~F的段选信号表示:

A (1010) ->1110111

B (1011) ->0011111

C (1100) ->1001110

D (1101) ->0111101

E (1110) ->1001111

F (1111) ->1000111

6 (0110) ->101111(原:0011111) 9 (1001) ->111101(原:1110011) 实验修改部分电路截图:

实际效果:

从电路板的显示来看:6、9以及a-f均正常显示

总结:

学到的知识点:学习到了示波器以及数码管的使用,明白了数码管中各个脚管的连接方式以及电路之间的联系方式,清楚了DDA- III型实验板的构造及底层原理,以及段选信号和位选信号的作用究竟是什么。

掌握的技能:了解了相关软件的安装以及环境的配置、实验板的使用方法以及工作原理,能够熟练使用Quartus II中的各种工具, 掌握模块的封装和再利用。

人文:在刚接触电路板的时候,我们许多人觉得很难理解,觉得学不懂,在老师的热心帮助以及同学们积极互助下最终我们一步 步接受了这些知识,慢慢掌握了使用方法,总之,小组互助是完成实验的良好方法。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?