- 外部中断EXTI

(一)中断系统

- 中断顾名思义就是可以在程序执行中的打断其执行来执行自己的一种程序,在中断打断程序执行时会保护现场,让系统知道选择这个程序执行到哪,当中断的函数执行完后可以返回了进行执行被打断的这个程序,并且能恢复现场,这和操作系统中的上下文切换有异曲同工之妙,通过这种中断的形式,主程序可以不要一种通过轮询的方式取查看某个条件是否达到被执行的要求,只需要在中断发生时切换过去执行就可以,这种方式在很大的的程度上减轻了系统的压力,提高了性能。

- 正在执行的中断也可以被其他中断优先级更高的中断打断,这个就是中断嵌套,当更高优先级的中断执行完成后,执行原来的中断,原来的中断执行完后又返回去执行主程序。

3、Cortex-M3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

一般情况下,芯片厂商会对Cortex-M3的中断进行裁剪。

STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程的中断优先级。

STM32F103系列70个中断(咱们目前使用的芯片)有10个内核中断和60个可编程的外部中断

这70个中断就是F103中包含的中断,其中Reset,NMI和硬件失效这三个中断是不能被设置的,也就是这三个中断的优先级是固定的,而其他的67个中断的优先级是可以设置的,外面可以根据自己的需要进行设置。此处这个中断的优先级是默认的优先级,由于STM32的中断管理系统NVIC使用的是4位优先级,所以在设置优先级过程中难免会有一些重复,当两个任务或者多个任务的NVIC中的抢占优先级和响应优先级都相同时,并且是差不多同时就绪的时,系统就会根据这个默认大的中断优先级进行中断的执行。

4、NVIC嵌套中断向量控制器

NVIC(Nested vectored interrupt controller嵌套向量中断控制器)和处理器核的接口紧密相连,可以实现低延迟的中断处理和高效地处理中断。嵌套向量中断控制器管理着包括内核异常,外部中断等所有中断。由NVIC决定哪个中断的处理程序交给CPU来执行。

中断就绪后不是直接就与内核进行对接的,而是先通过NVIC控制器的处理后再交给内核进行处理的。

NVIC管理的是各个中断的优先级,NVIC通过给每个中断分配优先级,从而确保中断之接有条不紊的进行,不会产生各个中断任务乱七八糟的情况。

NVIC分配的优先级又分为抢占优先级和响应优先级;其中响应优先级可以理解为可以在中断列表中正常排队的优先级,各个中断根据响应优先级的大小依次排队,而抢占优先级可以理解为可以插队的优先级,就是他可以直接在自己就绪后就直接插入去打断别人,执行自己。

优先级值越小,优先级越高。

规则:

如果不设置优先级,则默认优先级为0。

先比较抢占优先级。抢占优先级高的可以打断抢占优先级低的。

若抢占优先级一样,再比较响应优先级。但是响应优先级不会导致中断嵌套。

若抢占优先级一样的同时挂起,则优先处理响应抢占优先级高的。

若挂起的优先级(抢占和响应)都一样,则查找中断向量表,值小的先响应。

- 中断优先级分组

|

分组 |

抢占优先级 |

响应优先级 |

|

0 |

0位 取值范围:0 |

4位 取值范围:0-15 |

|

1 |

1位 取值范围:0-1 |

3位 取值范围:0-7 |

|

2 |

2位 取值范围:0-3 |

2位 取值范围:0-3 |

|

3 |

3位 取值范围:0-7 |

1位 取值范围:0-1 |

|

4 |

4位 取值范围:0-15 |

0位 取值范围:0 |

- 外部中断控制器

1、AFIO通过把PA~PG相同编号的通用IO口连接到16根外部中断/事件线上,从而引出来16根外部中断线,再接入外部中断控制器中给进行配置,当外部中断控制器配置处理完后,再通过NVIC的配置处理就可以角给内核进行中断处理。

2、认识外部中断EXTI,可以直接通过这两个图进行理解,图1中通过AFIO复用后引出来的EXTI0~EXTI15就是图2中外部中断的输入线。

输入的信号首先通过边沿检测电路查看输入信号是否满足上升沿触发选择器或下降沿触发选择器,满足边沿检测后再通过一个或门,检测边沿检测或者软件中断两个有没有满足的,有母子的就会把请求挂起寄存器置1,若中断屏蔽寄存器没有开启屏蔽时,此时请求挂起寄存器和中断屏蔽寄存器就都是1,通过与门就可以输入到NVIC,通过NVIC的配置后就可以到内核处理中断。

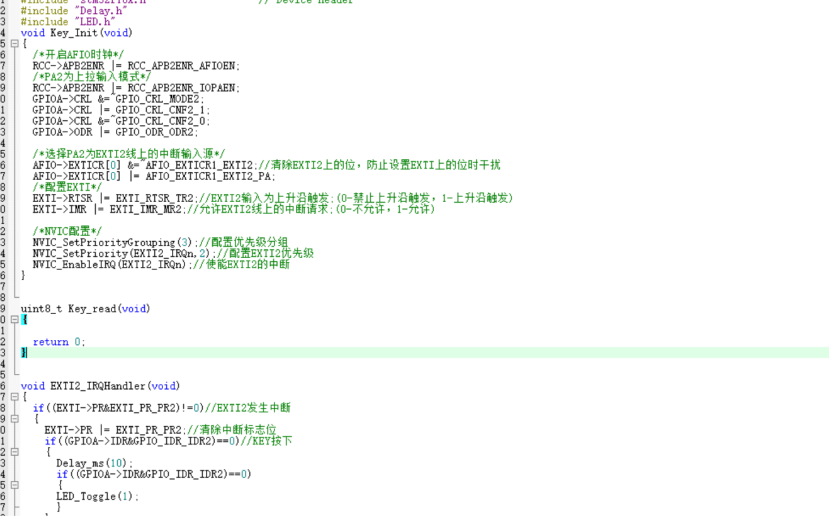

外部中断的配置可以分为以下的几步:

- 开启RCC,GPIO,AFIO时钟

- 配置IO口输入模式

- 通过AFIO把IO口复用到EXTI线上

- 配置EXTI

- 配置NVIC

- 中断处理

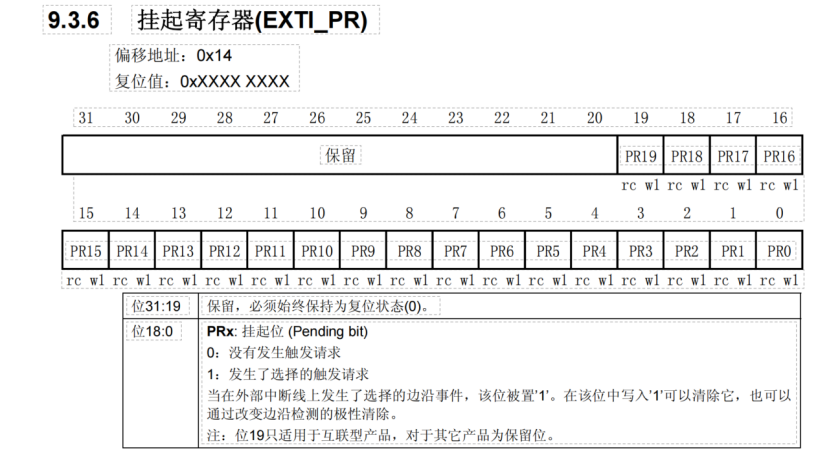

- 相关寄存器

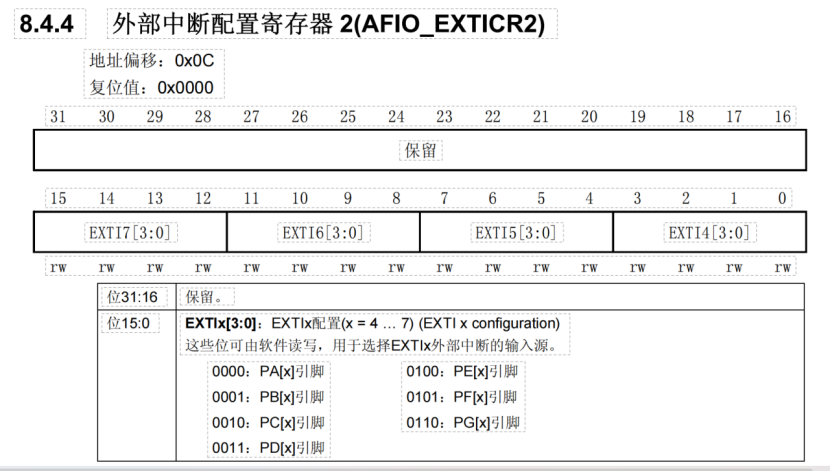

(1)这个寄存器是一个数组类型的AFIO->EXTICR[],其中有四个元素,不同的位的寄存器可以配置不同的EXTI,比如此处的AFIO_EXTICR2就可以配置EXTI4~EXTI7的外部中断。

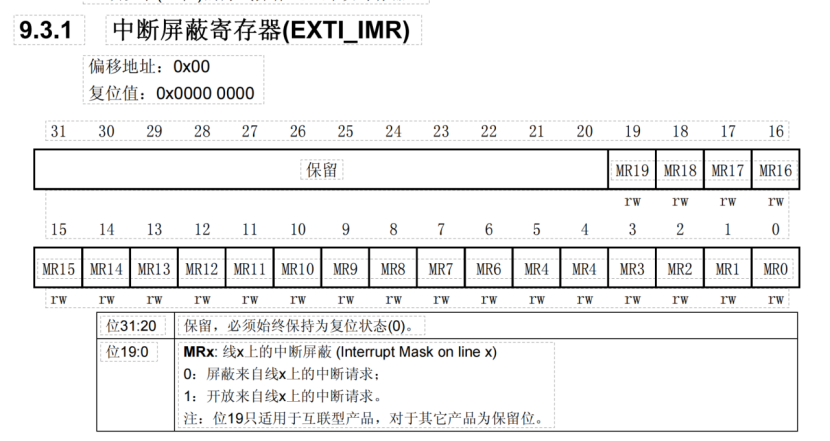

(2)这个寄存器是配置是否响应中断请求的寄存器,当这个寄存器为0,也就是屏蔽了来自线x上的中断请求时,即使x线上有中断请求,有不会发生中断。

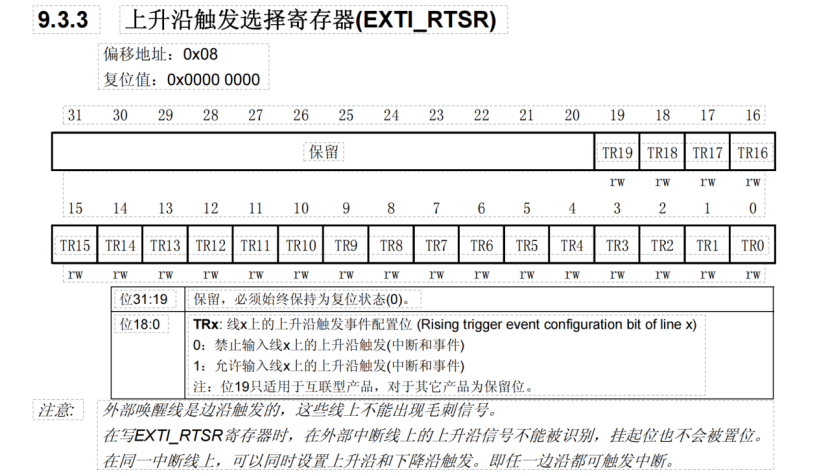

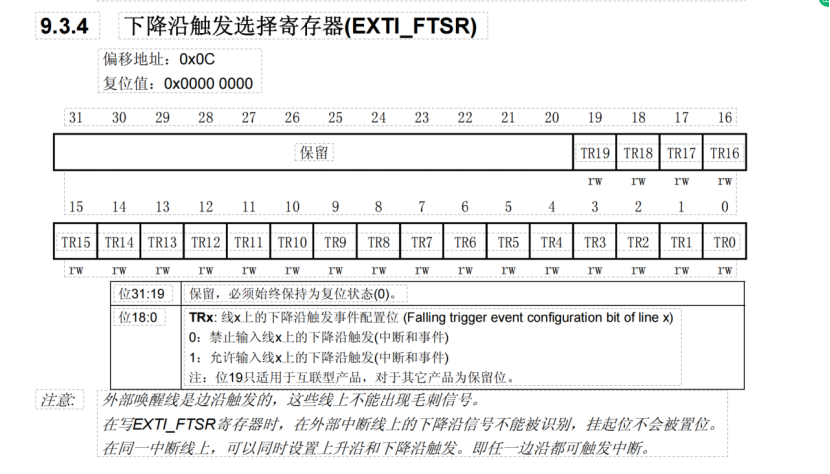

(3)这两个寄存器是配置EXTI线上进来的信号是上升沿有效还是下降沿有效,当然也可以两个边沿都有效。

(4)当边沿检测电路或者软件响应触发中断后,这个位会自动挂起置1,可以通过判断这个位来判断是否有中断请求,从而进行处理,但是这个位不会自动清除,响应我们直接手动清除。

- 外部中断的简单应用

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?