摘 要 :新 型 S iC半 导 体 功 率 器 件 的 开 关 速 度 快 ,对 线 路 中 的 寄 生 参 数 敏 感 度 高 ,在 开 关 过 程 中 会 产 生 较 大 的 电 压 和 电 流 过 冲 ,从 而 影 响 器 件 的 开 关 性 能 和 安 全 工 作 裕 度 。此 处 针 对 S iC器 件 电 压 和 电 流 过 冲 形 成 的 原 因 ,提 出了一种基于 di/dt 优 化 的 有 源 栅 极 驱 动 技 术 。 该 技 术 在 传 统 驱 动 器 的 基 础 上 ,在 栅 极 分 别 增 加 了 可 控 的 恒 流 充 电 和 恒 流 放 电 电 路 ,并 通 过 控 制 开 关 过 程 中 的 充 放 电 时 间 宽 度 来 调 整 出/ d t 的 大 小 ,从 而 减 小 S iC器件的开 关 损 耗 和 降 低 开 关 过 程 中 的 电 压 和 电 流 过 冲 ,实 现 SiC器 件 在 安 全 工 作 区 内 的 稳 定 运 行 。此 处 首 先 分 析 S iC器 件在开关过程中出/ t k 对电压和电流过冲的影响,然后详细介绍了所提栅极驱动技术的原理及其硬件实现方 案 ,最 后 通 过 设 计 实 验 验 证 了 该 技 术 的 可 行 性 。

引 言

随着电力电子技术的飞速发展,髙电压、大电 流的应用场合对功率器件的开关性能提出了更高 的要求。SiC器件作为一种新型的宽禁带半导体 器件,相较于传统的S i器件具有开关速度快、开 关损耗小等优点。但是由于开关速度的提髙,在开 关过程中高山7出和线路中的寄生参数共同作用, 产生的电流和电压过冲与振荡会影响器件的安全 工作裕度,并形成电磁干扰噪声。

传统栅极驱动器(CGD)通过改变门极驱动电压或驱动电阻等方法来调节器件的开关速度叭 该方法对整个开关过程进行调节,无法灵活调节 SiC器件在开通或关断中部分阶段的开关速度。文 献[2]基 于 CGD的设计思路提出了一种有源栅极 驱动器(AGD)的设计方法,在提高器件开关性能 的同时能实现有效的短路保护功能。现有的AGD 方法多应用在IGBT的驱动电路中,可以大致分为 3 类:在开关过程中实时切换驱动电阻、实时切换 驱动电压w以及实时调节连接在器件栅极的受控 电流源。与 IGBT器件相比,SiC器件的开关时间 显著缩短,这提高了 AGD方案在SiC驱动电路中 的实现难度。文献[4]针对小功率SiC器件在开关 过程中形成的电压和电流过冲,提出了一种单管 电流源切换的AGD方案。在此基础上,将 CGD和 AGD的方法相结合,针对高压大电流的SiC模块提出了 一种通过控制di/出来降低开关过程中电 压和电流过冲的驱动器设计。该设计通过减小驱 动电阻的CGD方法加快器件在整个开关周期内 的开关速度,并采用切换电流源的AGD方法调整部分开关过程的速度,从而在减小开关损耗的基 础上控制出/dt,降低开关过程中的电压和电流过 冲。相较于文献[4]提出的单管电流源电路,此处所 采用的镜像电流源具有更加稳定的输出电流,这 有利于改善SiC器件的开关性能。

2 CGD方案中 di/dt对开关过程的影响

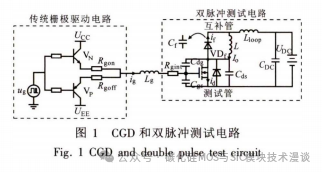

2.1 CGD方案与双脉冲测试电路

CGD的设计方案如图1 左侧部分所示,该方 案采用推挽电路以提供足够的栅极电流。对于 CGD方案,可 以 通 过 改 变 驱 动 电 阻 和 驱 动电压C/cc和或者在待测器件的栅源极或漏 栅极两端并联电容的方法来调节器件的开关速 度,上述方法无法灵活调节开关过程中,会造成额 外的开关损耗。

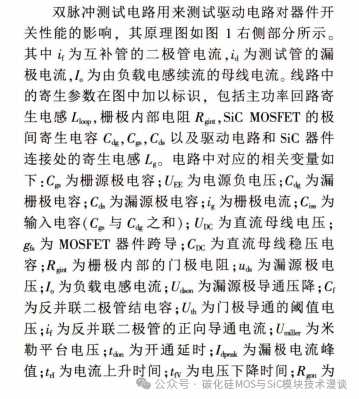

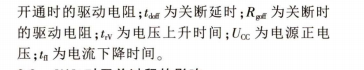

2.2 di/dt对开关过程的影响

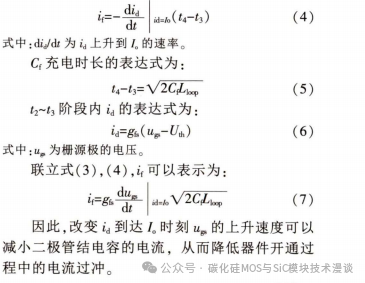

不同于 S i器件的反并联二极管,SiC器件的 反并联二极管的反向恢复时间较短,可近似忽略。 在 t3~i4阶段,反并联二极管VDf 的结电容Cf起到 主要作用,故 在 t3~t4 阶段,可等效为一个恒定上 升斜率的电流源对Cf充电,其充电电流为:

3 基 于 C G D 和 A G D 结合的优化控制方案

3.1 优化控制方案的工作原理

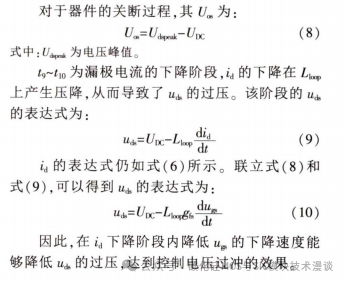

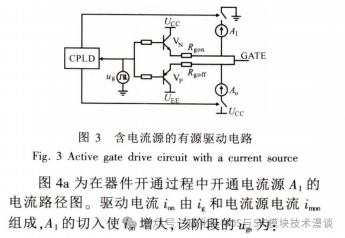

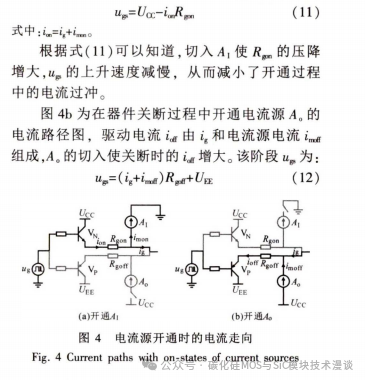

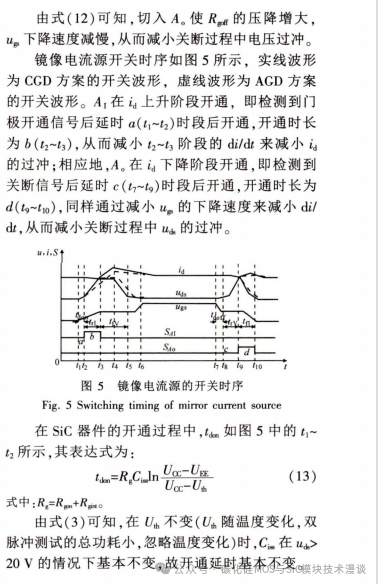

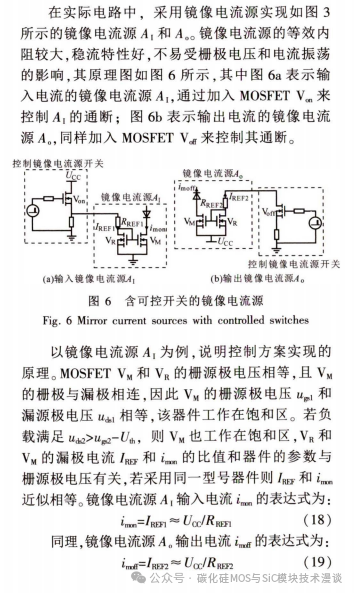

由上述可得,CGD方案改变整个开关过程的 开关速度,而 AGD方案可以在不同开关阶段内对 开关速度进行调整,这可以增加系统控制的自由 度 ,从而实现多种控制目标,如加快开关速度、减 小开关损耗或减小过冲等。所提出的优化控制方 案 将 CGD与 AGD方案相结合,通过减小驱动电 阻的CGD方案来加速整个开关过程,降低开关损 耗,同时采用切换电流源的AGD方案在 t3~t4(id 上升阶段)和 V^ 1()(id下降阶段)减 慢 SiC器件的 开关速度,从而控制开关过程中的出/出,在降低 器件开关损耗的基础上实现减小开关过程中电压 和电流过冲的目标。优化控制方法采用的电路如 图 3 所示。该设计在传统CGD方案的基础上,加 入了两个可控制开断的镜像电流源实现AGD方 案,通过复杂可编程逻辑器件(CPLD)控制器采样 脉宽调制(PWM)信号并计算开关时间来控制电 流源的开关。加入的两个电流源的输出电流方向 不同,其电流方向如图 3 所示。

3 . 2 优化控制方案的实现

由式(18),(19)可知,通过调节参考电阻Kret的大小可以调节镜像电流源电流的大小。

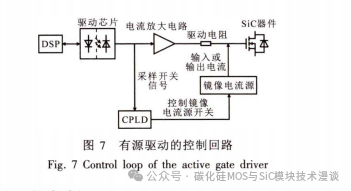

由于SiCMOSFET的开关速度快,加之硬件 延时的存在,实时采样闭环控制的方法很难达到 较好的控制效果。若采用文献[2]的方法检测di/ 出,加上比较器和一系列开关管,会增加延时,无 法实现控制目标。此处采用了一种开环控制的方 式 ,在母线电压电流一定的情况下,采 样 PWM信 号的上升沿和下降沿,根据第 2.2节的方法计算 各个阶段的时间,进行开环控制,使得控制方案更 加灵活。此处采用的AGD方案的控制回路如图7 所示,通 过 CPLD控制器采样驱动芯片次级输出 驱动信号开通和关断的时刻,计算不同母线电压 电流下的开关延时、漏极电流的上升、下降时间来 得到控制电流源的开通和关断的时刻。

4 实验验证

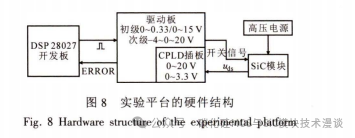

基于上述的优化控制方案搭建实验平台,其 结构如图8 所示,图中的DSP 28027控制器用来 输出控制 SiC M0 SFET开关的 PWM信号和接收 驱动板发出的故障信号。驱动板的初级供电为 0~15 V 电源,次级为-4~0~20 V 的正负电源供电 方式,以提供SiC模块正向和负向的驱动电压。 CPLD控制器采样驱动芯片的次级驱动信号,用以 控制电流源的开关。

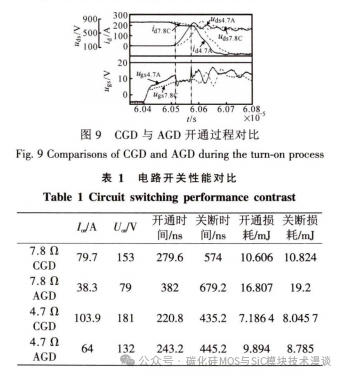

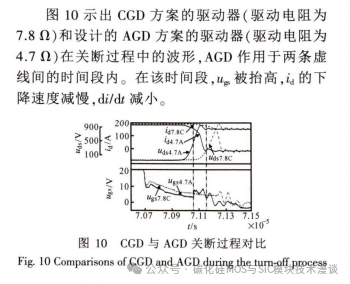

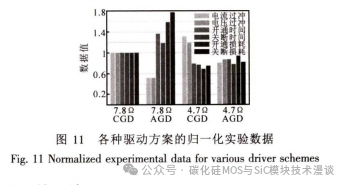

搭建的实验平台中SiC MOSFET模块采用的 是 1200 V/300 A 半桥模块 CAS300M12BM2 , 负载 电感为244 jjlH 的空心电感。前端控制器采用DSP 28027控制器,AGD由 LC4032型 CPLD控制器实 现。为了验证所提出的优化控制方案的可行性,在800V/150A 的母线输入条件下,将 CGD方案的驱 动器(驱动电阻为7.8 Ω)和设计的AGD方案的驱 动器(驱动电阻为 4.7Ω ) 进行对比,图 9 为两种 方案开通过程的波形。其 中 AGD方案作用于两条 虚线间的时间段内。在该时间段,^被 拉 低 ,漏极 电流的上升速度减慢,di/d t减小。表 1 中记录了 两种方案的开关数据结果,由表中数据可得,改进 后的驱动器在开关过程中产生的电压和电流过冲 更小,且开关损耗更小,开关速度更快。

表 1 将驱动电阻为 7.8 的 CGD与 AGD方 案 、驱动电阻为 4.7 Ω的 CGD和设计的驱动电阻 为 4.7Ω 的 AGD方案进行对比,并将表中数据和 驱动电阻为 7.8 Ω的 CGD方案进行归一化处理, 其结果如图 1 1所示。从 表 1 和 图 1 1可知,在驱动电阻为7.8Ω 的基础上,只采用AGD方案可以减 小开关过程中的电压和电流过冲,但是会造成开 关损耗的增加和开关时间的增加;若只采用CGD 方案,将驱动电阻 7.8Ω 减小到 4.7Ω开关损耗 和开关时间减小,但会造成更大的电压和电流过 冲;若采用CGD和 AGD方案相结合,将驱动电阻 从 7.8Ω减小到 4.7Ω , 并采用AGD方案进行控 制,则电压和电流过冲减小,开关损耗减小,开关 时间减小,因此可以证明所提出的将CGD与 AGD 方案相结合的优化控制方案的可行性与优越性。

5 结论

此处通过对 SiC器件在开关过程中高di/dt 引起的电压和电流过冲进行理论分析,设计了控 制开关过程中di/出的栅极驱动器。相比于传统驱 动方案,采用将调整驱动电阻的CGD和切换电流 源的 AGD相结合的方法,减小开关过程中的电压 和电流过冲,同时加快开关速度,减小开关损耗。 为了验证所提出的优化控制方案的有效性,搭建 了双脉冲测试电路进行了实验验证,能达到减小 开关过程的电压和电流过冲、加快开关速度、减小 开关损耗的目标。

参考文献

[ 1 ] 刘 帆 ,朱 德 文 ,吴 钫 ,等 .SiCMOSFET建模及驱动

电路设计[J].电力电子技术,

2〇18 , 52(12 ) : !33- 1 36.

[2] Z W ang,X Shi,L M Tolbert,et al.A di/df Feedback

based Active Gate Driver for Smart Switching and Fast

Overcurrent Protection of IGBT Modules[J].IEEE Trans,

on Power Electronics, 2014,29(7) :3720-3732.

[3] H 0bara,K Wada,K Miyazaki,et al.Active Gate Control

in Half-bridge Inverters Using Programmable Gate Driv

er ICs to Improve Both Surge Voltage and Converter Ef

ficiency [J]. IEEE Trans, on Ind. Appl.,2018,54 ( 5 ):

4603-4611.

[ 4 ] 柯 俊 吉 ,赵 志 斌 ,谢 宗 奎 ,等 .考 虑 寄 生 参 数 影 响 的 碳

化 硅 M0SFET开关暂态分析模型 [J].电工技术学报 ,

2 0 1 8 ,3 3 (8 ):1762-1774.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?