🚀 【考纲要求】指令执行的过程

🚀 中央处理器 5.1节请点击此链接 CPU的结构和功能

在上一小节中,我们学习了CPU要拥有的五个基本功能:数据加工,指令控制,操作控制,时间控制,中断响应;基本的结构:运算器(ALU ACC 通用寄存器 暂存寄存器 移位寄存器 PSW),控制器(CU IR MDR MAR PC)。

这一小结我们要探究指令执行的过程。

二、指令执行的过程

2.1指令周期

指令周期: 是指CPU每次从取指到执行指令完成的全部时间,称为一个指令周期。

🔊 一条指令的执行又可以分为多个操作,如取指阶段和执行指令阶段,而每个阶段完成一个操作的时间称为一个机器周期,所以一个指令周期可能包括多个机器周期;又由于每条指令不同,有的机器指令可能就只有取指操作,所以不同指令的指令周期也是不同的。

🔊 对于不同指令的执行指令操作所需要的时间也是不同的,即机器周期是不同的,例如直接寻址指令只需要一次访存操作,而间接寻址指令需要多次的访存操作,所需要的时间可能会更长,所以不同指令的机器周期也可能是不同的。

🔊 机器周期由若干个时钟周期组成,而指令周期由若干个机器周期组成,时钟周期都是一样的,一个时钟周期完成一个微操作,多个微操作的执行完成一个操作,即若干个时钟周期组成一个机器周期;一系列的操作完成一条指令,即若干个机器周期组成一个指令周期。

由于不同的指令在执行过程中需要多种操作,可能包括以下操作取指令操作,间址阶段,执行阶段,中断阶段。所以对于一条指令的执行,指令周期内可能就需要包含这四个阶段。接下去我们要探究这四个阶段的的数据是怎么流动的。

2.2指令周期的数据流

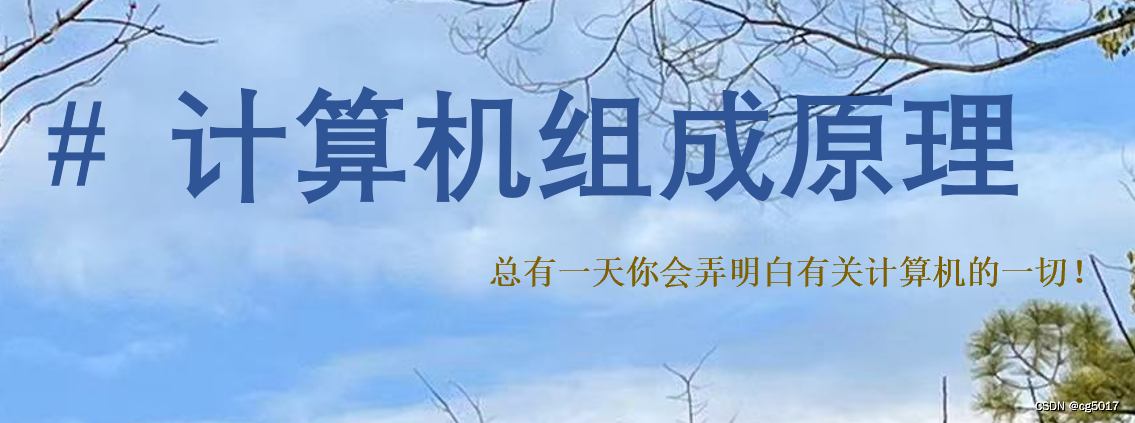

①取址阶段

取址阶段,就是CPU从内存中取出要执行的指令,将其放入IR寄存中。

数据流向过程如下:

- PC指明这次要执行的指令在内存中的地址,将PC的内容送至MAR

- MAR中的内容通过数据总线传至存储器,CU通过总线传送控制命令,给存储器发出读的命令

- 存储器将MAR中指向的内容通过数据总线送至MDR

- 将取得的指令内容再送至IR寄存器保存

- 同时CU控制PC加 “1”

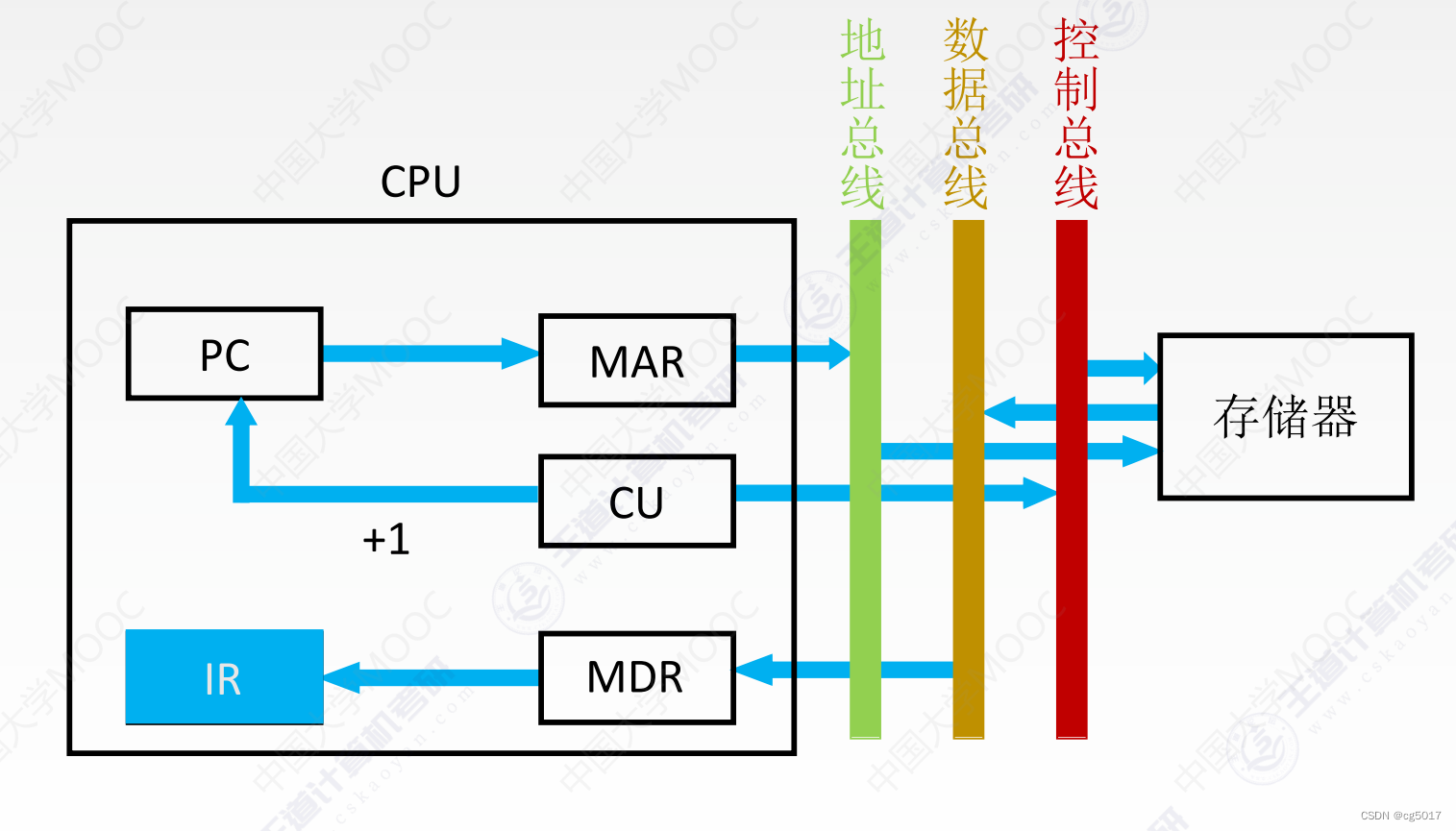

②间址阶段

对于间址寻址的指令,就需要拥有间址阶段供它寻找有效地址。

数据流向过程如下:

- 首先由IR(也可以由MDR给出,因为取指阶段MDR中的内容和IR中的一致)给出此次间址的地址,传入MAR中,MAR通过地址总线传送至存储器

- CU通过控制总线给出读的信号,存储器将MDR中指向的内容通过数据总线传送至MDR

- 再将从主存中取得的有效地址放回IR中,从而得到了正真要操作的有效地址

③执行阶段

执行周期的任务是根据IR中的指令字的操作码和操作数通过ALU操作产生执行结果,不同指令的执行周期操作不同,因此没有统一的数据流向。

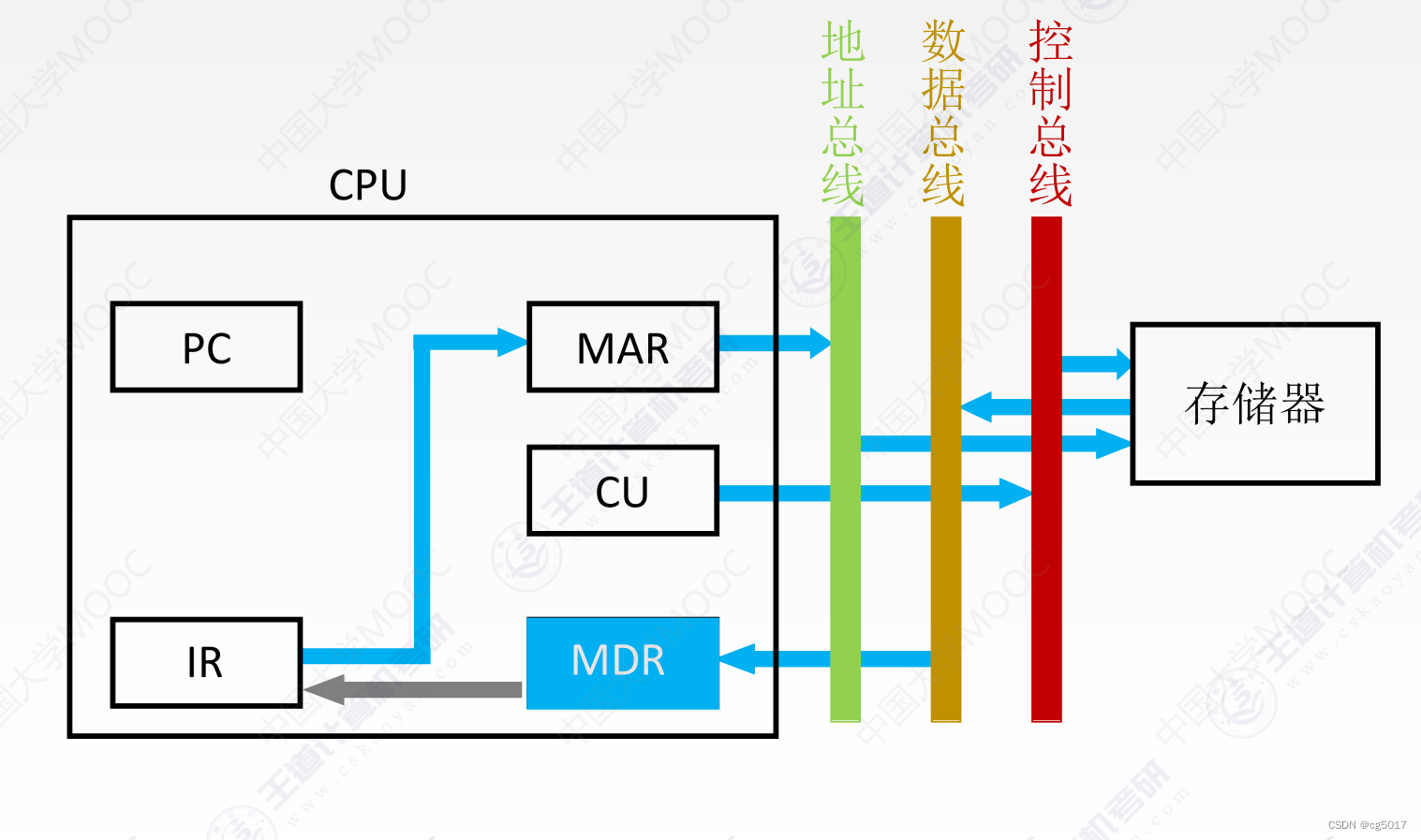

④中断阶段

- CU控制SP-1,即得到栈顶的上的一个地址空间,将其送入MAR,MDR中的内容通过地址总线送入存储器

- CU再将写的命令通过控制总线送入存储器

- PC寄存器中的内容送入MDR,再通过数据总线将PC中的内容保存至堆栈顶部,从而实现了中断断点的保护

- 最后在CU的控制下,将中断服务程序的入口地址送入PC

2.3指令执行方案

由于指令执行所需要的指令周期是不同的,但是我们仍然需要有序的控制着指令的执行,以下是三种不同的方案控制指令的执行。

①单周期处理器

每个指令都用于相同的指令周期,任意一个指令都可以在一个指令周期内完成,每条指令串行执行,这样就必须选用执行速度最慢的那个指令的执行时间作为单周期处理器的执行时间,这样做会大大降低整个系统执行的速度

②多周期处理器

按需分配,该条指令执行需要多少个时钟周期,就分配多少个时钟周期给它,但任然是串行执行的,执行效速度仍然比较慢,因为取址操作中每一个不同的之中周期,其所需要用到的硬件是不同的,这样我们为了更加充分的利用硬件资源,就有了流水线处理器。

③流水线处理器

每个时钟周期分配给一个指令执行,在机器周期这个层面就会产生一种多条指令并行执行的现象。

本文详细阐述了CPU指令执行过程,包括指令周期、机器周期划分,以及不同类型的处理器(单周期、多周期和流水线)在执行过程中的数据流和策略。重点介绍了取址、间址、执行和中断阶段的数据流动情况。

本文详细阐述了CPU指令执行过程,包括指令周期、机器周期划分,以及不同类型的处理器(单周期、多周期和流水线)在执行过程中的数据流和策略。重点介绍了取址、间址、执行和中断阶段的数据流动情况。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?