在上一节,我讲了一部分的ModelSim的使用方法。本节,我们继续来学习ModelSim的基本使用方法。

如果你还没有学习上一节知识,那么,请你先去学习一下上一节的内容。

上一节内容的链接如下。

接下来,我们来正式讲解本节的内容。

一. Wave界面的左侧的信号列表操作

首先呢,让我们来点击下图所示的红色框线中的具有【全局观察】功能的按钮,

图1

然后呢,界面右边的波形图,将恢复全局观察的状态。

(一)将信号名完全显示出来

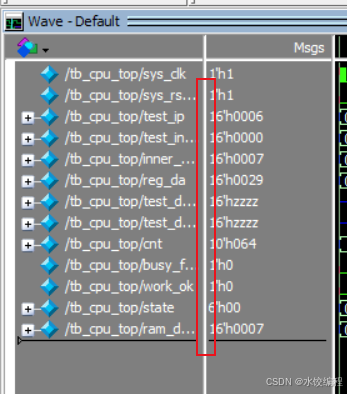

接下来,我们来看一看界面的左侧的上方的部分,如下图所示。

图2

在图2里面,它是分为了两列。左边的一列里面,有着许多的三维模样的蓝色菱形小方块。每一个零星小方块位于一行。菱形小方块的右边,还有不同的字母。

在这里,每一个零星小方块,代表着的,是一个变量,或者说,它代表着一个信号。每一个信号,都是在test bench文件里面所声明的一个变量。无论它是reg型变量也好,还是wire型变量也好,都是变量,并且也都会显示在本列的信号列表里面。

在第二列的上面,有Msgs字样,下面,是一堆数值。这些个数值,是对应的左边的信号的信号终值。

我们再来看信号列表里面的情况,有的信号的信号名的右边,有三个点,这代表着说,本信号名很长,本列现有的长度不足以将信号名全部显示出来。所以右边有三个点。如果某一个信号的名字的右边不含有三个点,则代表本信号名完整地显示出来了。

对于信号名不能完整显示的情况,我们一般地,会希望将其全部显示。因为,我们有时候,会需要根据信号名,来查看这一信号的波形演变情况。

怎么做呢?

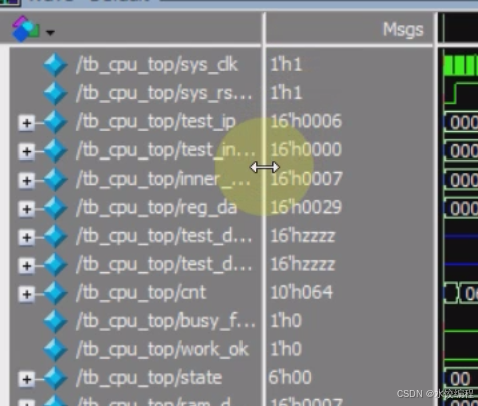

图3

在图3里面,我用红色框线标出了一个区域,这个区域的中间,是一个白色高亮显示的竖线。这条竖线,我们可以拖动它,以此来改变信号名一列的列宽。

方法是,我们首先将鼠标指针停在这个白色竖线上,如果你停留的位置正确,则鼠标指针变为两个箭头相离的形状,如下图所示。

图4

注意,在你那里,你是看不到黄色的圈圈的。这个图,我不是通过截图来截取到的,而是通过录屏软件,录制到的。我在录屏软件里面,设置了让鼠标指针周围显示黄色圈圈的效果。你那里,能够看到的,是两个箭头相背离的指针形状。

当鼠标指针变为相离的形状的时候,按下鼠标左键不松手,向右拖动鼠标指针,则信号名列表一列的列宽将会增长。待到我们觉得列宽合适的时候,在松开鼠标左键,就可以了。此时,信号名列表一列的列宽就变为我们新设置的列宽了。

结果如下图所示。

图5

在图5

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2707

2707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?