目录

一、实验目的

(1)理解累加器的概念和作用。

(2)连接运算器、存储器和累加器,熟悉计算机的数据通路。

(3)掌握使用微命令执行各种操作的方法。

二、实验电路

本实验使用的主要元器件:4位算术逻辑运算单元74LS181,8位数据锁存器74LS273,8位正沿触发寄存器 74LS374、三态输出的总线收发器 74LS245,2K×8 静态随机存储器6116,时序产生器,与非门、与门、开关、指示灯等。

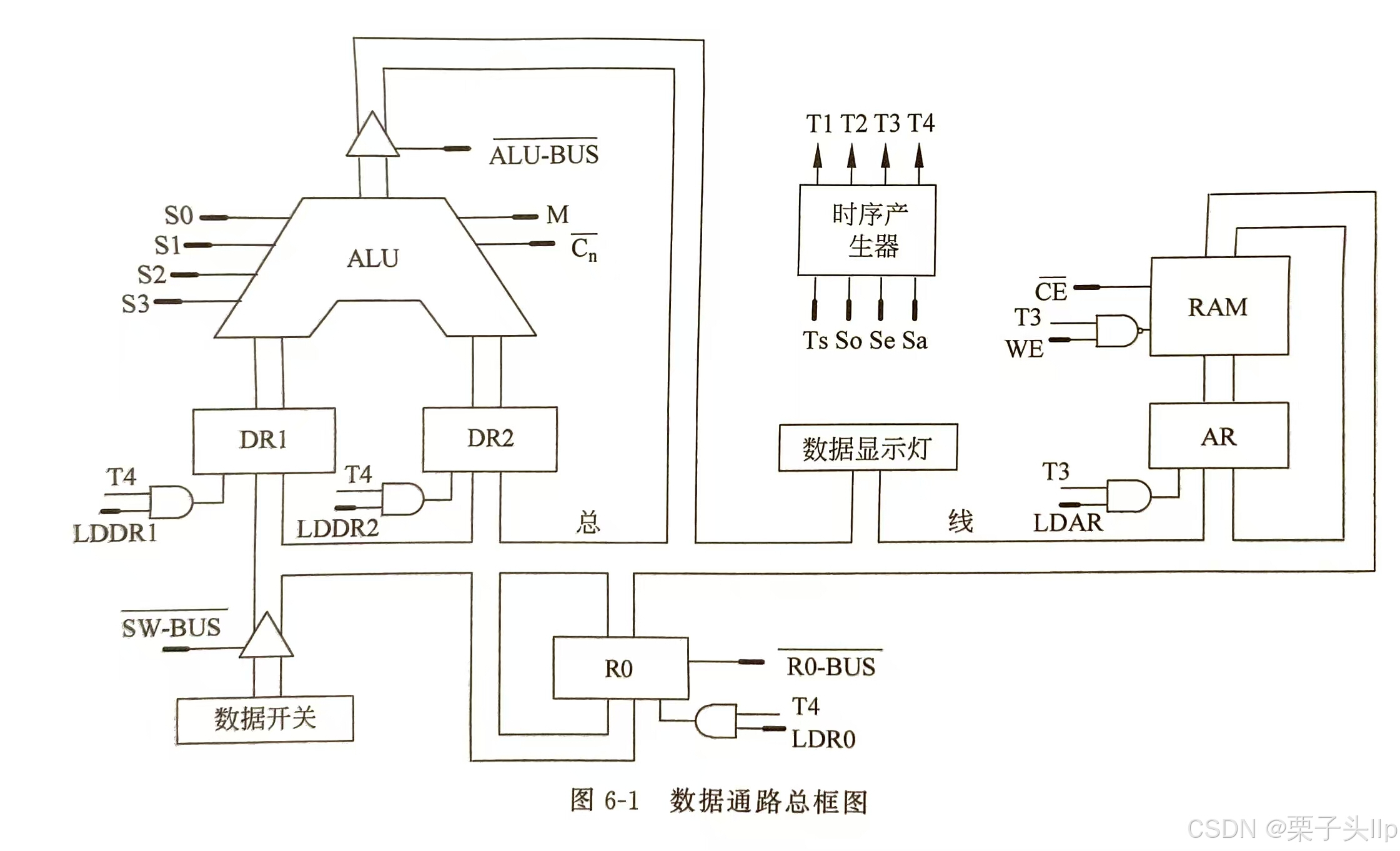

本实验数据通路总框图如图6-1所示,其中ALU由两片74LS181构成,DR1、DR2和AR 均为一片 74LS273,RAM为一片6116芯片,R0寄存器为一片74LS374芯片,△表示三态门74LS245,时序产生器为虚拟实验系统提供的虚拟组件。

主要控制信号如下:

(1)M:选择ALU的运算模式(M=0,算术运算;M=1,逻辑运算)。

(2)S3、S2、S1、S0:选择ALU的运算类型。如M=0时,设为1001表示加法运算。

(3)¬Cn:向ALU最低位输人的进位信号,¬Cn=0时有进位输入,¬C=1时无进位输入。

(4)LDDR1:DR1的数据加载信号,与T4脉冲配合将总线上的数据传入DR1中。LDDR1 和T4通过与门进行与运算后连接到 74LS273 芯片的 CP 引脚,当LDDR1=1时,在T4的上升沿将数据锁存到DR1。

(5)LDDR2:DR2 的数据加载信号,与 T4 脉冲配合将总线上的数据传人 DR2中。LDDR2和T4 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDDR2=1时,在T4的上升沿将数据锁存到DR2。

(6)¬MR:74LS273芯片的清零信号,低电平有效。本实验恒置为1。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5945

5945

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?