在数字电路中,上拉电阻和下拉电阻是两种常用的被动元件,用于将信号引脚稳定在确定的逻辑电平(高或低),避免因引脚悬空导致的不确定状态。

一、上拉电阻

定义:

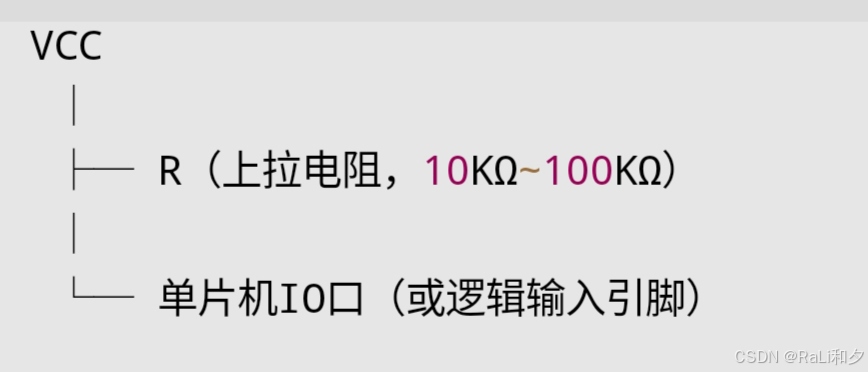

上拉电阻是连接在信号引脚与电源(通常为VCC)之间的电阻,将引脚默认电平拉高到逻辑高电平(如3.3V或5V)。

上拉电阻连接电路图:

作用:

1. 稳定未驱动的引脚:当引脚未被外部电路驱动时(如GPIO未配置为输出),上拉电阻使其保持高电平,避免因噪声干扰导致误触发。

2. 增强驱动能力:某些芯片的输出引脚驱动能力较弱,上拉电阻可提供额外电流,确保信号可靠传输。

3. 总线通信:在I²C、SPI等总线中,上拉电阻用于将总线保持在高电平(空闲状态),并允许多设备通过下拉总线实现“线与”功能。

典型应用场景:

微控制器的GPIO引脚(如按键输入电路中,按键未按下时,引脚通过上拉电阻保持高电平)。

传感器输出信号的稳定(如接近开关的数字输出)。

总线通信的终端匹配(如I²C总线的4.7kΩ上拉电阻)。

阻值选择:

通常为1kΩ~100kΩ,需平衡功耗和响应速度。例如:

高速电路选较小阻值(如1kΩ),减少RC延迟;

低功耗场景选较大阻值(如100kΩ),降低静态电流。

二、下拉电阻

定义:

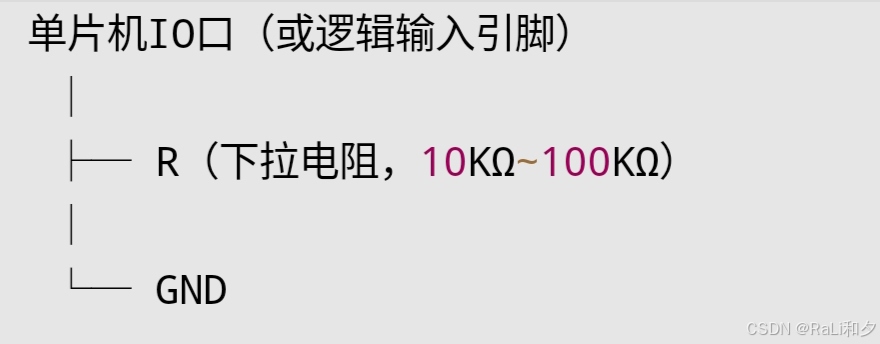

下拉电阻是连接在信号引脚与地(GND)之间的电阻,将引脚默认电平拉低到逻辑低电平(0V)。

下拉电阻连接电路图:

作用:

1. 稳定未驱动的引脚:与上拉电阻类似,但目标电平为低电平。

2. 消除浮空干扰:某些情况下,引脚浮空易受噪声影响,下拉电阻使其稳定在低电平。

3. 电平转换:在需要低电平有效信号的电路中(如复位信号),下拉电阻确保默认状态为有效。

典型应用场景:

复位电路中的复位引脚(上电时通过下拉电阻保持低电平,待系统稳定后释放)。

传感器输出的低电平有效信号(如某些类型的光电传感器)。

逻辑门的输入端(如CMOS电路中,未连接的引脚需下拉以避免不确定状态)。

阻值选择:

与上拉电阻类似,通常为1kΩ~100kΩ,需根据具体电路需求调整。

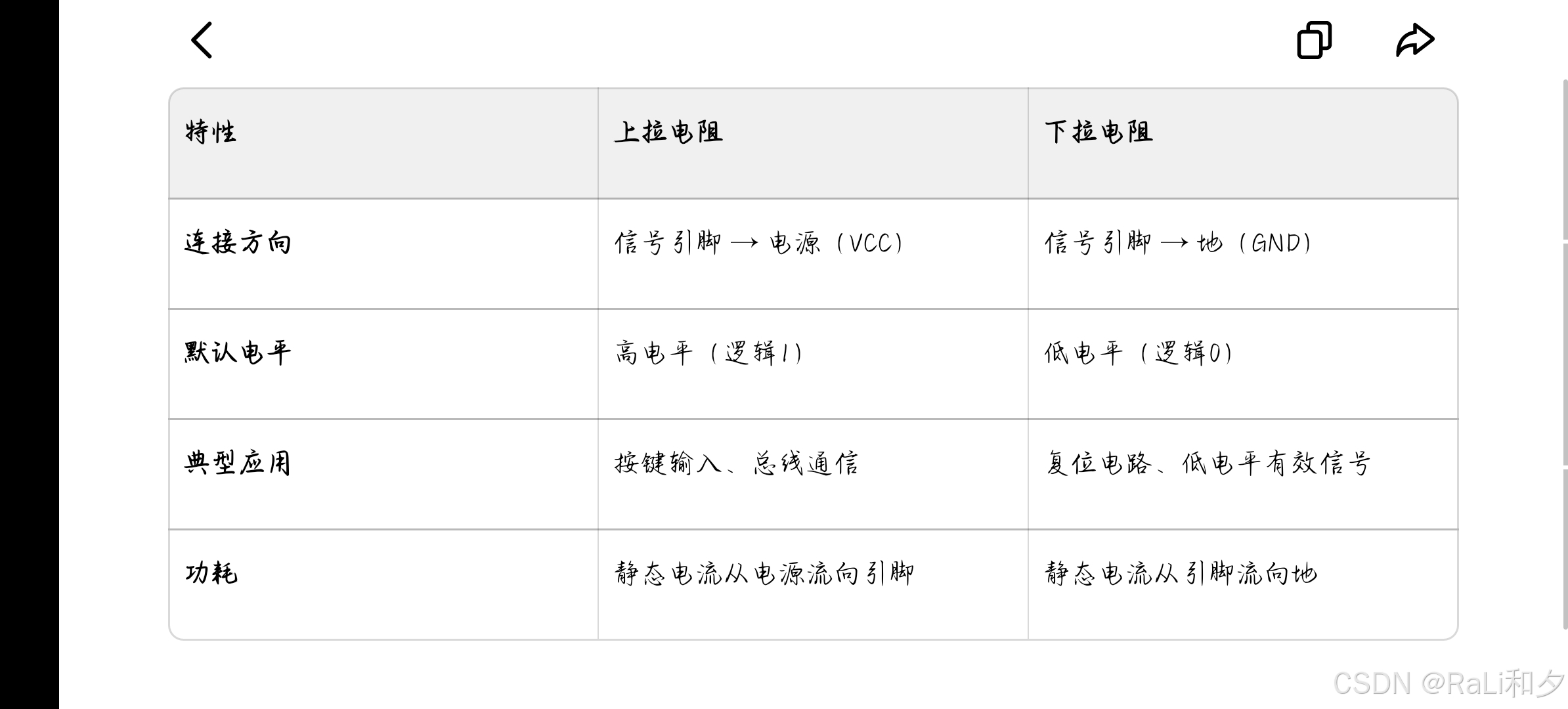

三、上拉与下拉的对比

四、设计注意事项

1. 内部 vs 外部电阻:

许多微控制器内置上拉/下拉电阻(如STM32的GPIO配置选项),优先使用内部电阻可简化电路设计。

2. 驱动能力匹配:

若外部电路需驱动上拉/下拉电阻,需确保驱动引脚能提供足够电流,避免电平被拉偏。

3. RC时间常数:

电阻与引脚寄生电容会形成RC电路,影响信号的上升/下降沿,需根据频率选择合适阻值

4. 低功耗设计:

大阻值电阻可降低静态功耗,但可能导致信号响应变慢。

总结

- 上拉电阻:默认拉高,常用于保持高电平或增强驱动能力;

- 下拉电阻:默认拉低,常用于稳定低电平或消除浮空干扰。

合理使用上拉/下拉电阻能显著提高数字电路的可靠性和抗干扰能力。

3632

3632

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?