1.Overview

CAN 通信符合 ISO 11898-1:2015。连接物理层需要额外的收发器硬件。

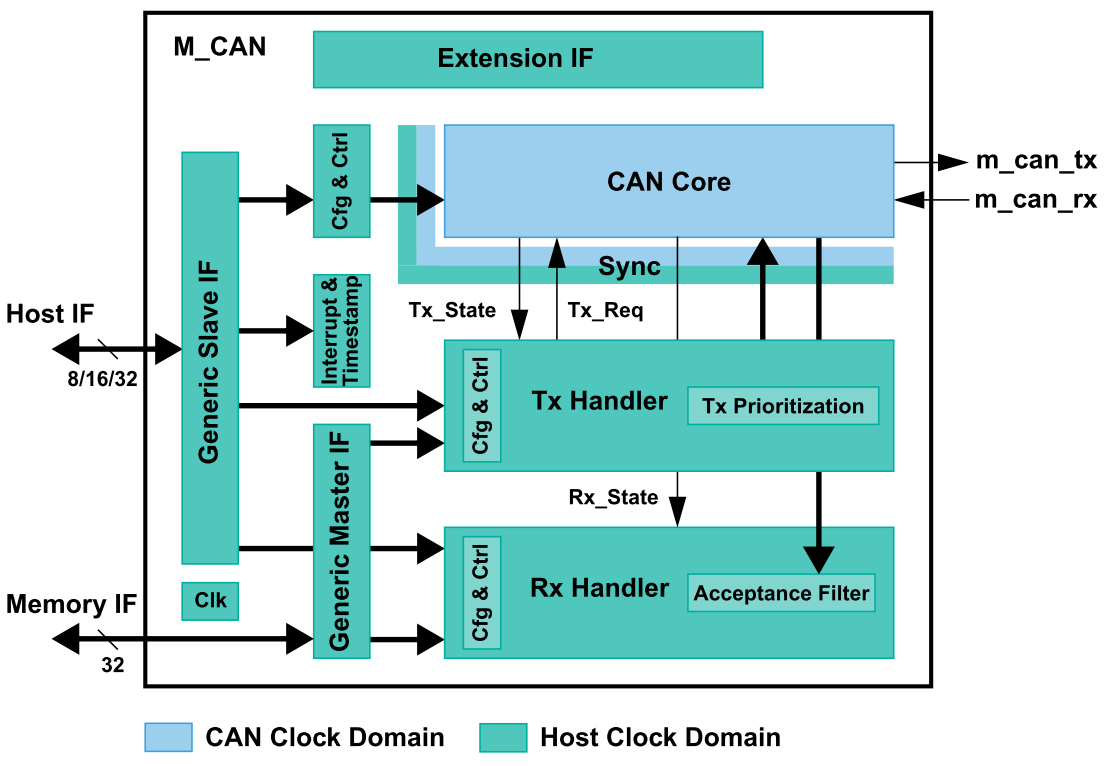

M_CAN 模块是一种新型的 CAN 通信控制器 IP 模块,可作为独立设备或集成到 ASIC 中。该模块在 RTL 层级使用 VHDL 描述,便于集成。M_CAN 通信符合 ISO 11898-1:2015。连接物理层需要额外的收发器硬件。

Message RAM 位于模块外部,可以是单端口或双端口。它通过 Generic Master Interface 连接到 M_CAN。根据 ASIC 集成方式,多个 M_CAN 控制器可共享同一个 Message RAM。

所有 Message 处理功能均由 Rx Handler 和 Tx Handler 实现:

-

Rx Handler: 管理接收 Message 过滤、将接收到的 Message 从 CAN Core 传输到 Message RAM,并提供接收状态信息。

-

Tx Handler: 负责将待发送 Message 从 Message RAM 传输到 CAN Core,并提供发送状态信息。

Acceptance Filter 由最多 128 个可组合的 Filter Elements 实现,每个均可配置为 Range Filter, Bit Mask Filter 或 Dedicated ID Filter。

M_CAN 通过其 8/16/32 位 Generic Slave Interface 连接各种 host CPU。M_CAN 的时钟域概念允许高精度 CAN 时钟与 host 时钟分离 (host 时钟可由 FM-PLL 产生)。

M_CAN 可通过其 8/16/32 位 Generic Slave Interface 连接到各种 host CPU。M_CAN 的时钟域概念允许高精度 CAN 时钟与 host 时钟分离,host 时钟可由 FM-PLL 产生。

1.1.Features

-

支持符合 ISO 11898-1:2015 的 Classical CAN 和 CAN FD。

-

支持最长 64 字节数据字段,实现大数据更快传输。

-

Support as CAN FD Light Commander: Standardization published in CiA 604-1: CAN FD light Protocol for responder nodes。

-

CiA (CAN in Automation) 正在进行标准化。

-

多个 M_CAN 模块可访问一个共享 Message RAM。

-

智能 Message 处理降低 CPU 负载。

-

可通过 8/16/32 位通用 CPU 接口连接客户特定 host CPU。

-

最高支持 8 Mbit/s 比特率 (取决于应用和收发器)。

-

使用 17/21 位 CRC (CAN FD) 或 15 位 CRC (CAN) 实现安全通信。

-

满足功能安全要求。

-

根据 ISO 26262-11:2018 Clause 4, M_CAN 开发为 SEooC (Safety Element out of Context)。

-

可提供 Safety Manual 和 FMEDA。

-

M_TTCAN 支持符合 ISO 11898-4 的 TTCAN (Time-Triggered CAN),适用于实时应用。

1.2.Block Diagram

-

CAN Core CAN 协议控制器和 Rx/Tx 移位寄存器。处理所有 ISO 11898-1:2015 协议功能。支持 11 位和 29 位标识符。

-

Sync 将信号从 host 时钟域同步到 CAN 时钟域,反之亦然。

-

Clk 使复位信号与 host 时钟域和 CAN 时钟域同步。

-

Cfg & Ctrl CAN Core 相关的配置和控制位。

-

Interrupt & Timestamp 中断控制和 16 位 CAN 位时间计数器(用于生成接收和发送时间戳)。可用外部生成的 16 位矢量替代集成计数器进行时间戳生成。

-

Tx Handler 控制从外部 Message RAM 到 CAN Core 的 Message 传输。最多可配置 32 个 Tx Buffers。Tx Buffers 可作为 dedicated Tx Buffers、Tx FIFO、Tx Queue 或其组合使用。Tx Event FIFO 存储 Tx 时间戳及对应 Message ID。支持发送取消。

-

Rx Handler 控制将接收到的 Message 从 CAN Core 传输到外部 Message RAM。支持两个大小可调的 Rx FIFO 和多达 64 个 dedicated Rx Buffers(用于存储所有验收通过的 Message)。与 Rx FIFO 不同,dedicated Rx Buffers 仅存储特定标识符的 Message。每条 Message 均附带 Rx 时间戳。可定义最多 128 个 11 位 ID 或 64 个 29 位 ID 的分隔符。

-

Generic Slave Interface 将 M_CAN 连接到客户指定的 host CPU。支持连接 8/16/32 位总线及多种互连结构。

-

Generic Master Interface 连接 M_CAN 访问外部 32 位 Message RAM。Message RAM 最大容量为 16K • 32 bit。单个 M_CAN 最多使用 4.25K • 32 bit。

-

Extension Interface 中断寄存器 IR 中的所有标记及选定的内部状态和控制信号均路由至此接口。用于将 M_CAN 连接到外部中断单元或其他外部组件。信号连接可选。

-

Dual Clock Sources 为改善 EMC,host 时钟域

m_can_hclk可使用扩频时钟。因 CAN Core 的高精度要求,m_can_cclk必须使用无调制的单独时钟。模块内实现同步机制确保时钟域间数据搬迁安全。 注意:M_CAN 稳定运行需 host 时钟频率 >= CAN 时钟频率,并考虑扩频时钟调制深度。 -

Dual Interrupt Lines 提供两条中断线

m_can_int0和m_can_int1。默认所有中断路由至m_can_int0。通过编程ILE.EINT0和ILE.EINT1可单独启用或禁用中断线。

2.Programmer’s Model

2.1Hardware Reset Description

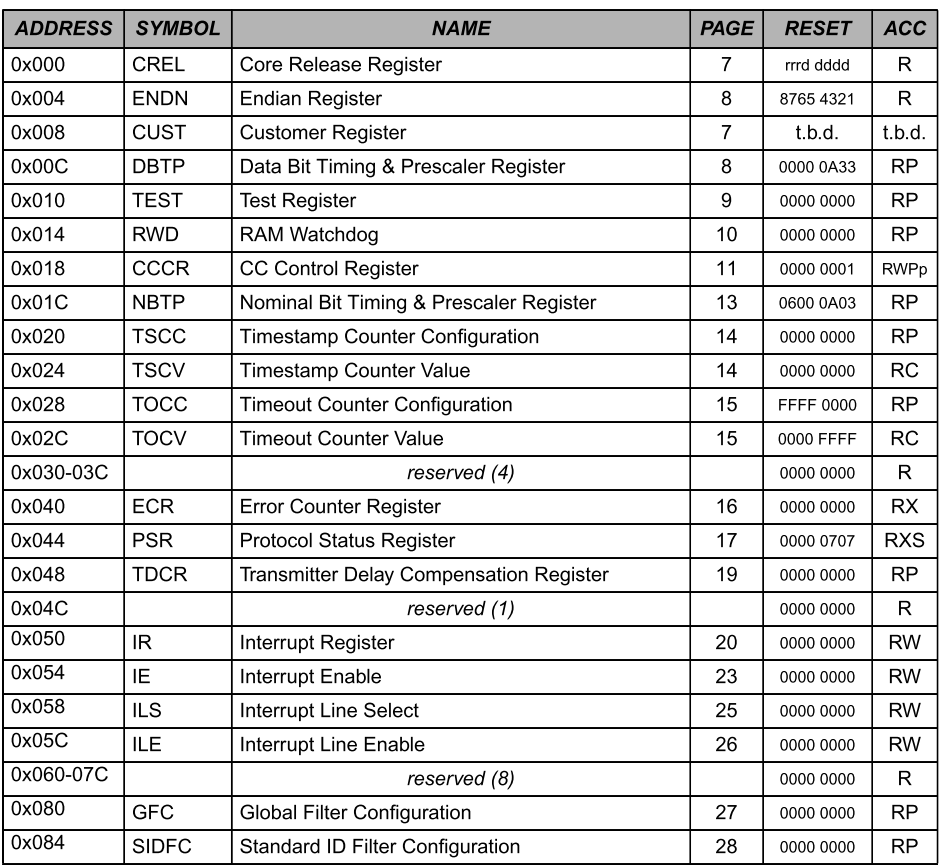

硬件复位后,M_CAN 的寄存器保持下表所列的复位值。此外,总线关闭状态被复位,输出 m_can_tx 被设置为隐性(高电平)。CC 控制寄存器中的值为 0x0001(CCCR.INIT='1')时使能软件初始化。在 CPU 将 CCCR.INIT 复位为 “0 ”之前,M_CAN 不会影响 CAN 总线。

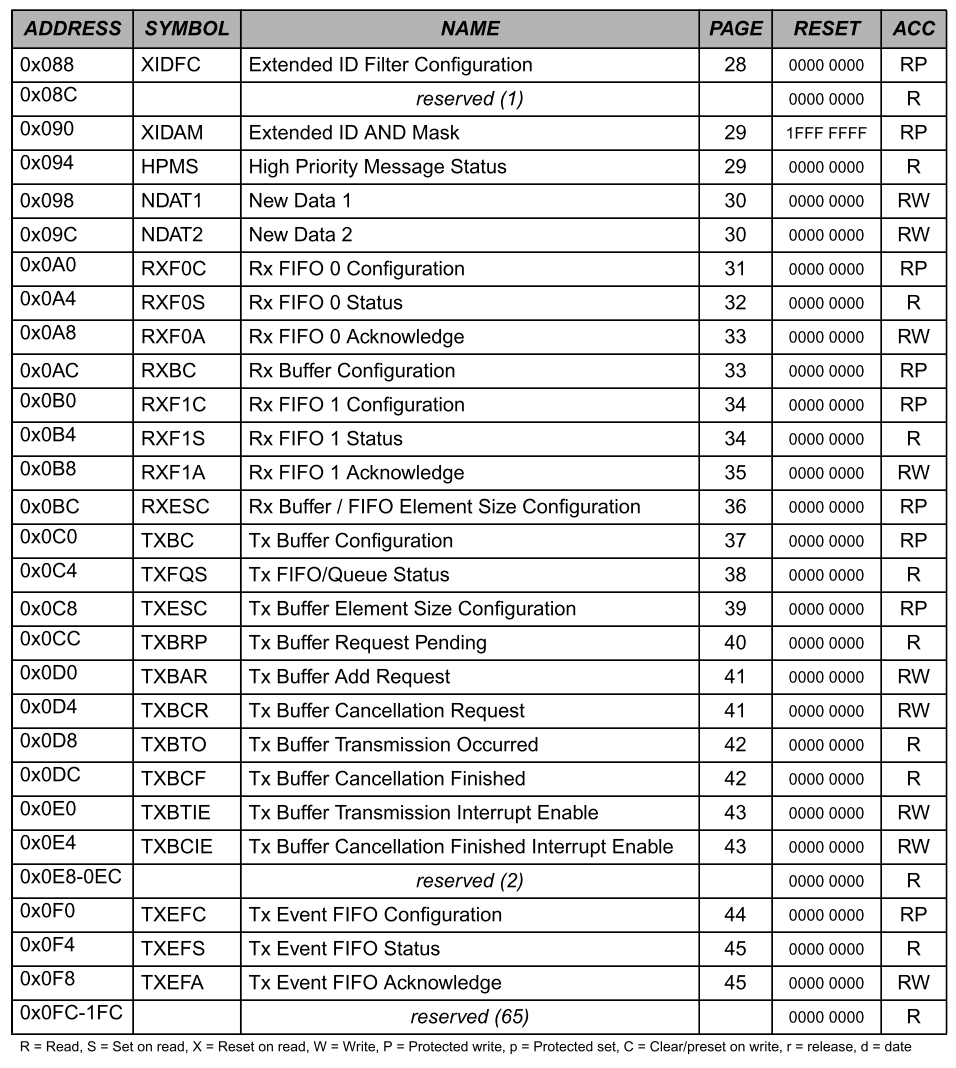

2.2.Register Map

M_CAN 模块被分配 512 bytes 的地址空间。所有寄存器都为 32-bit 寄存器。host CPU 可以通过 Generic Slave Interface 使用 8 bit (byte access)、16 bit (half-word access) 或 32 bit (word access) 的数据宽度访问 M_CAN。 只有当 CCCR.CCE='1'AND CCCR.INIT='1' 时,host CPU 才能对标有 “P=Protected Write”的寄存器/bit 进行写入访问。由于时钟域交叉,从写入命令寄存器到更新相关状态寄存器位会有延迟。

2.3.Message RAM

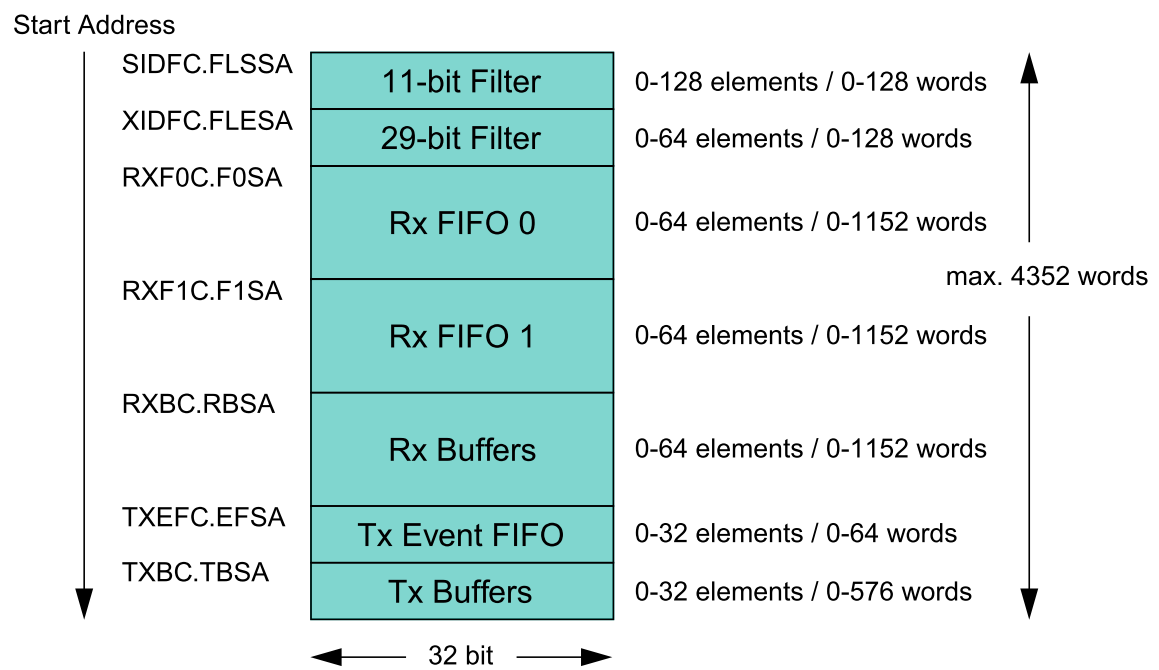

为了存储 Rx/Tx Messages 和 filter configuration,必须在 M_CAN 模块上连接一个单端口或双端口的 Message RAM。

2.3.1.Message RAM Configuration

Message RAM 的宽度为 32 bits。如果使用奇偶校验或 ECC,则必须在每个 word 上添加相应的 bits 。M_CAN 模块可配置为在 Message RAM 中分配多达 4352 个 words。无需对下图中列出的每个部分进行配置,对各部分的顺序也没有任何限制。

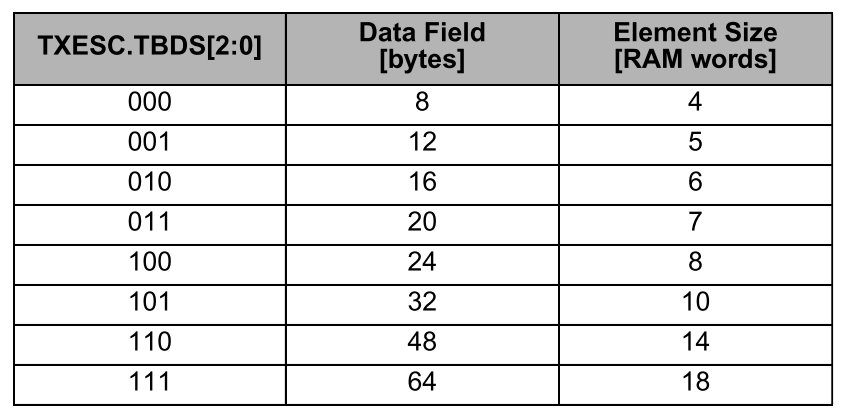

在 CAN FD 模式下运行时,所需的 Message RAM 大小主要取决于通过 RXESC.F0DS、RXESC.F1DS、RXESC.RBDS 和 TXESC.TBDS 为 Rx FIFO 0、Rx FIFO 1、Rx buffer 和 Tx buffer 配置的元素的大小。

当 M_CAN 寻址 Message RAM 时,它寻址的是 32-bit words,而不是单 bytes。可设置的起始地址为 32-bit word 地址,即只对第 15 位至第 2 位进行计算,忽略两个最小有效位。

注意:M_CAN 不会检查 Message RAM 的错误配置。特别是不同部分的起始地址和每个部分的元素数量的配置必须谨慎,以避免错误或数据丢失。

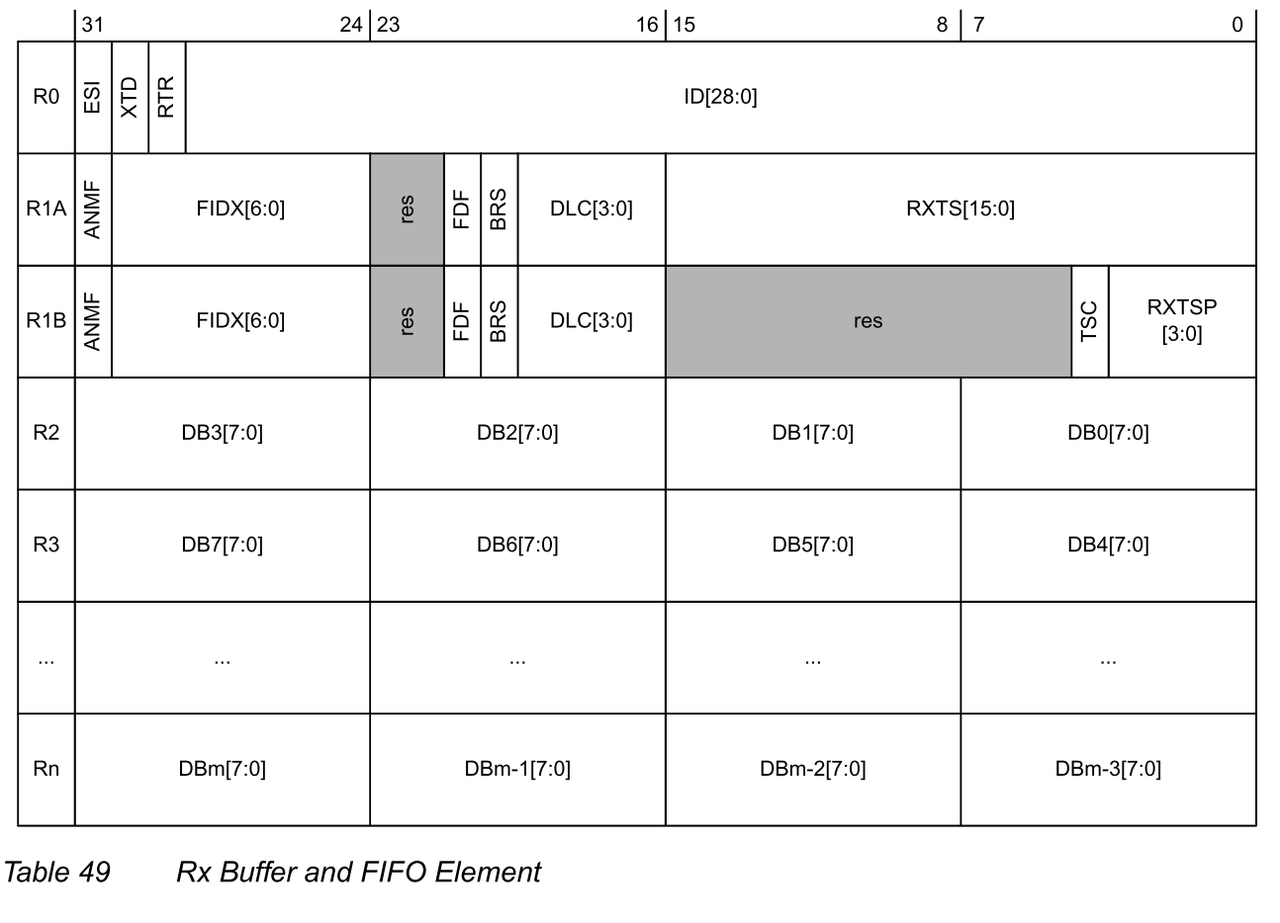

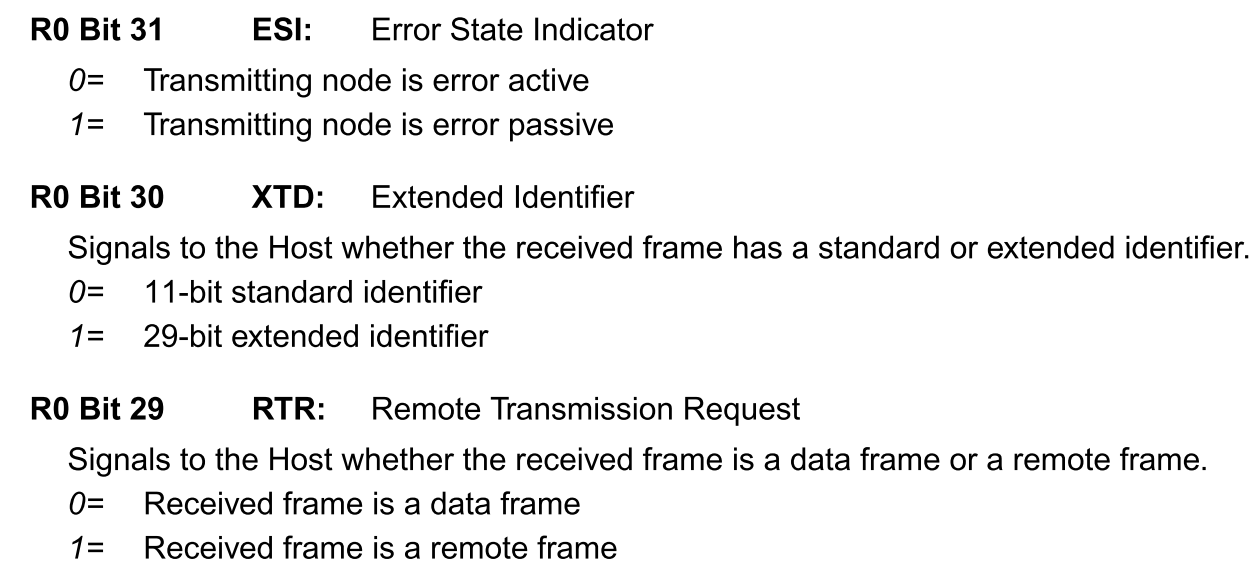

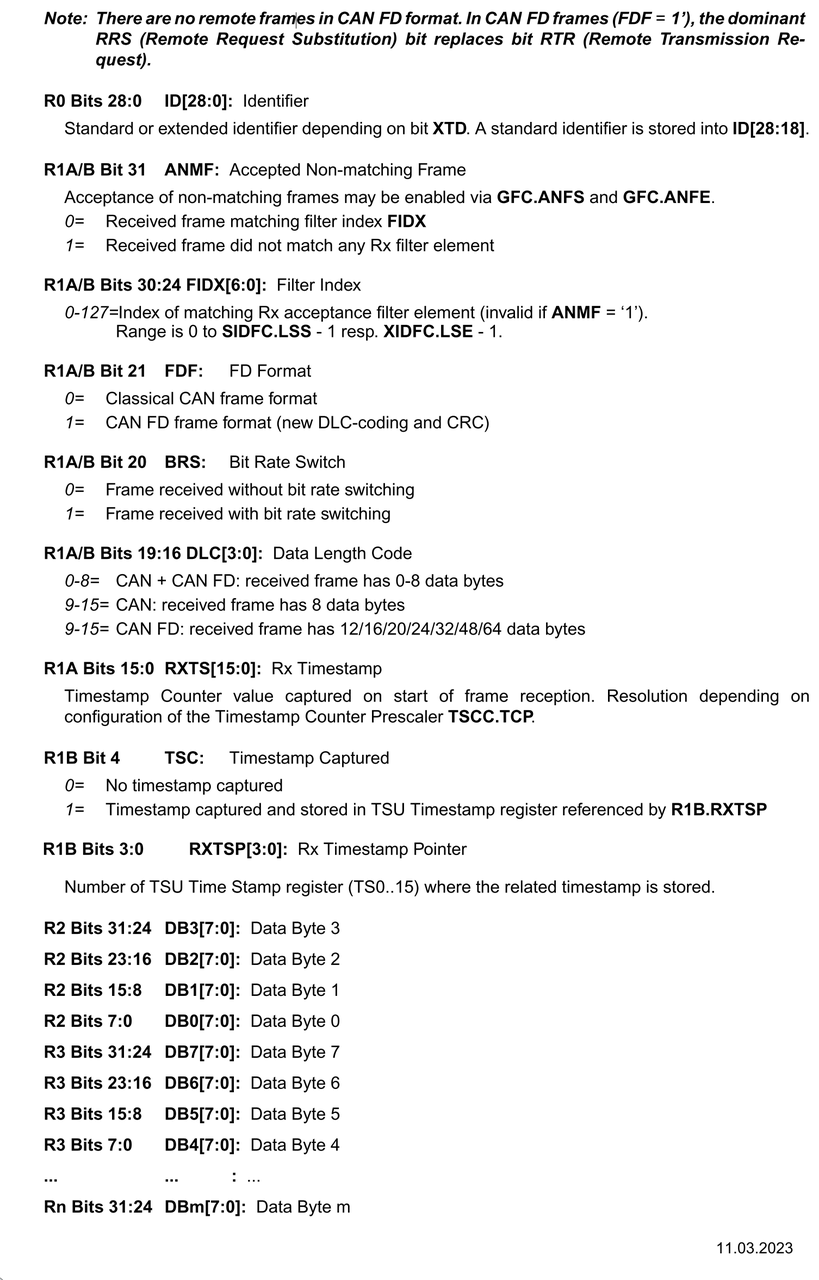

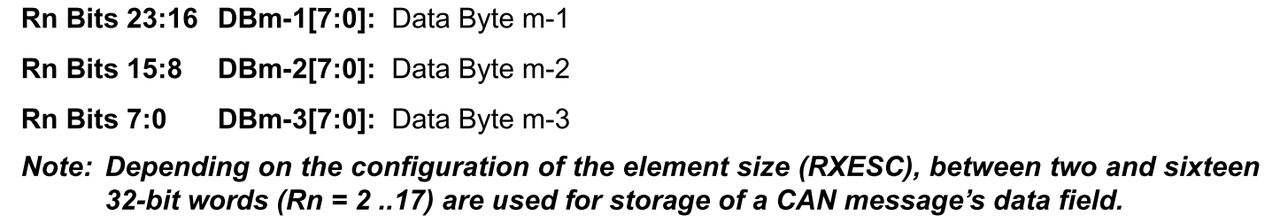

2.3.2.Rx Buffer and FIFO Element

Message RAM 中最多可配置 64 个 Rx Buffer 和两个 Rx FIFO。每个 Rx FIFO 部分最多可配置存储 64 条接收到 Message。Rx Buffer/FIFO Buffer element 的结构如下表所示。可通过寄存器 RXESC 配置 element size,以存储最多 64 bytes 数据字段的 CAN FD Message 。

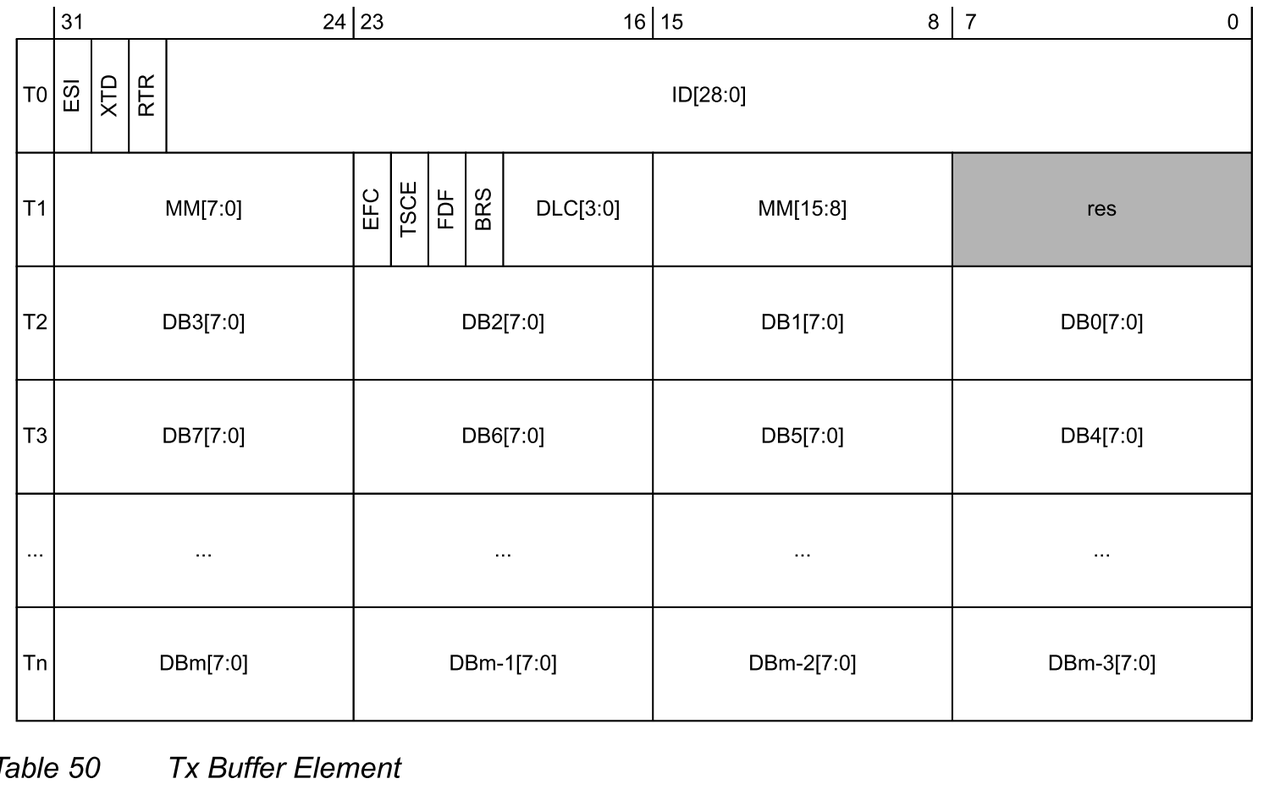

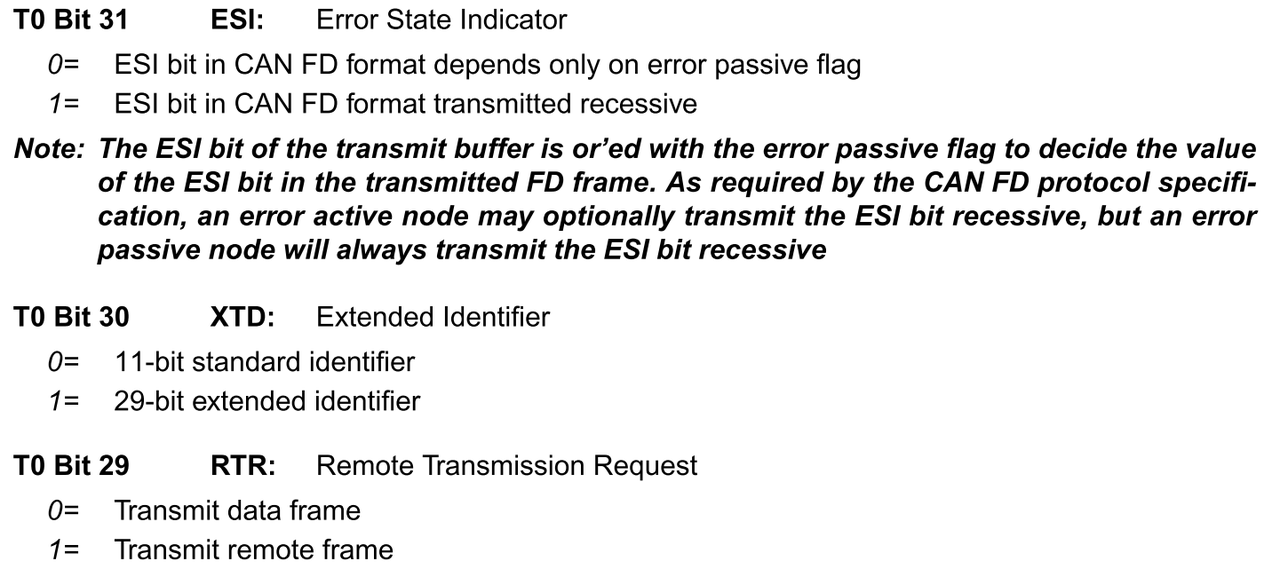

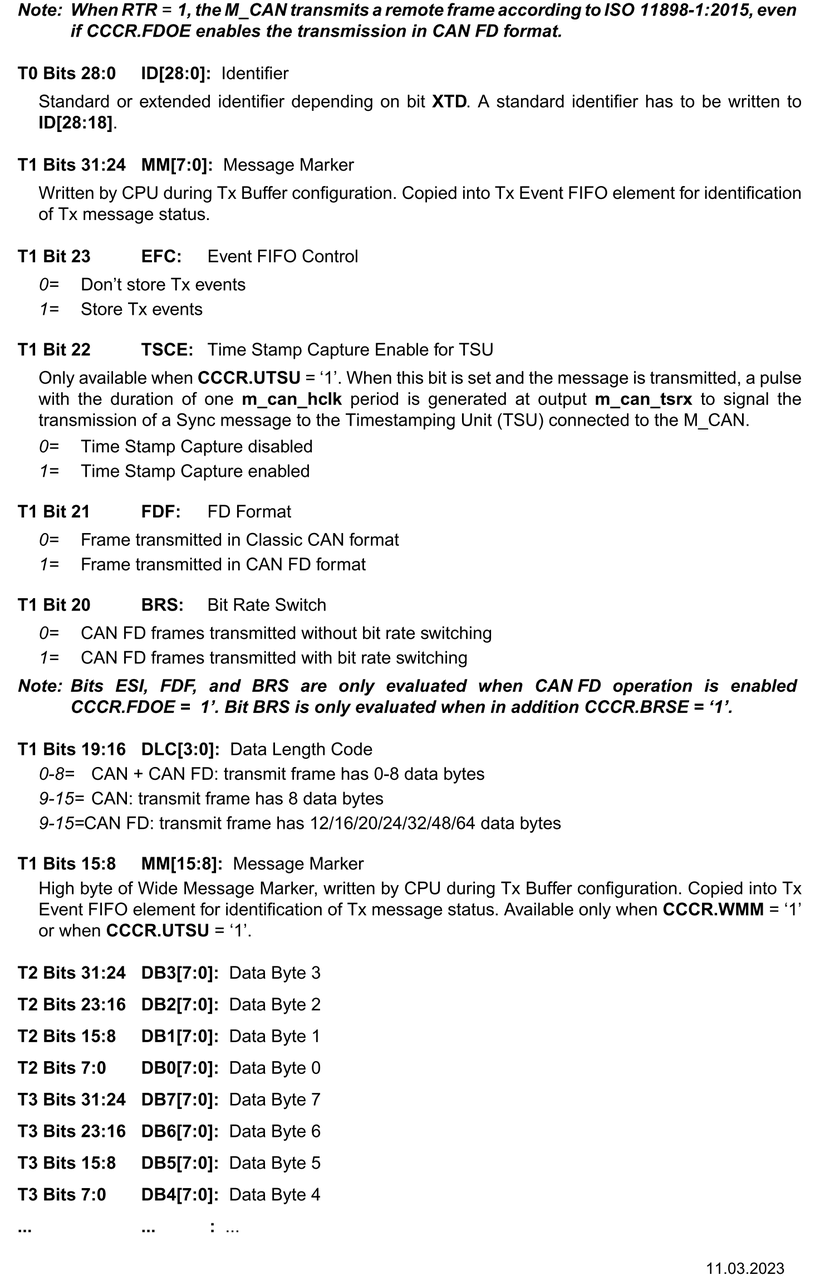

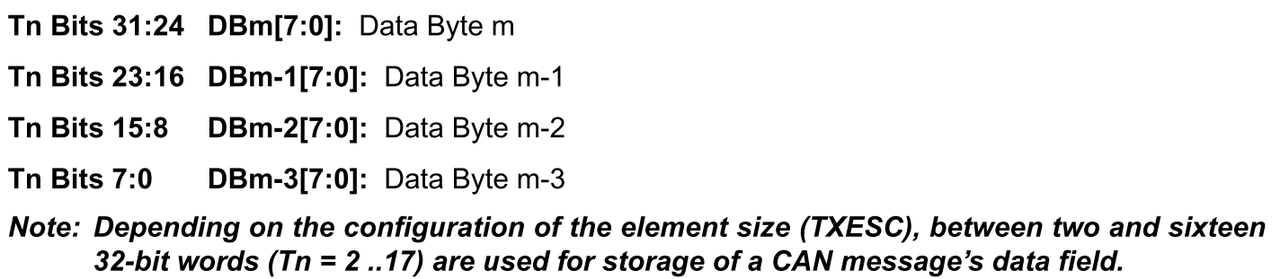

2.3.3.Tx Buffer Element

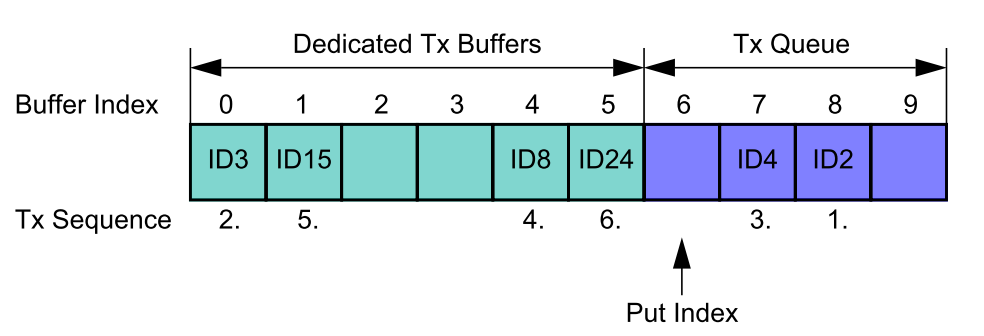

Tx Buffers 部分可配置为 dedicated Tx Buffers 和 Tx FIFO / Tx Queue。如果 dedicated Tx Buffers 和 Tx FIFO / Tx Queue 共用 Tx Buffers 部分,则 dedicated Tx Buffers 从 Tx Buffers 部分的开头开始,然后是分配给 Tx FIFO 或 Tx Queue 的 Buffers。Tx Handler 通过 Tx Buffers 配置的 TXBC.TFQS 和 TXBC.NDTB 来区分 dedicated Tx Buffers 和 Tx FIFO / Tx Queue。可通过寄存器 TXESC 配置 element size,以存储最多 64 bytes 数据字段的 CAN FD Messages。

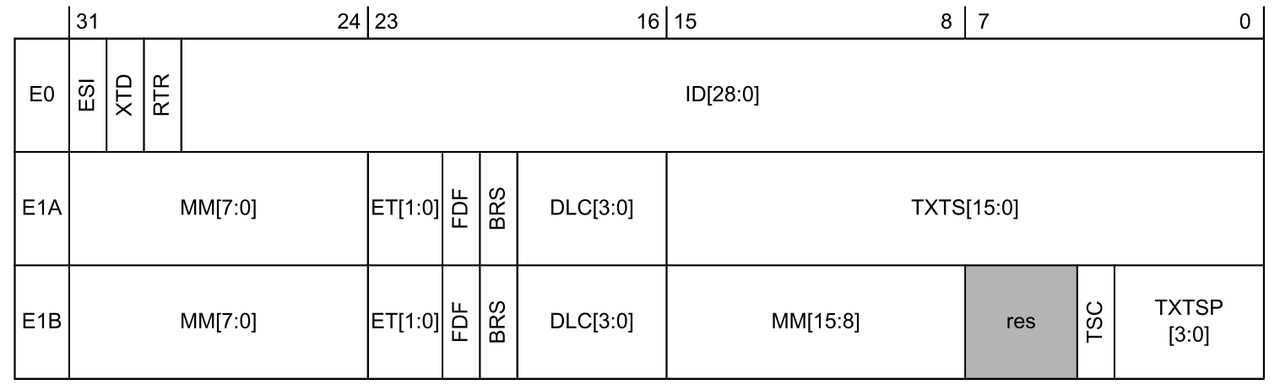

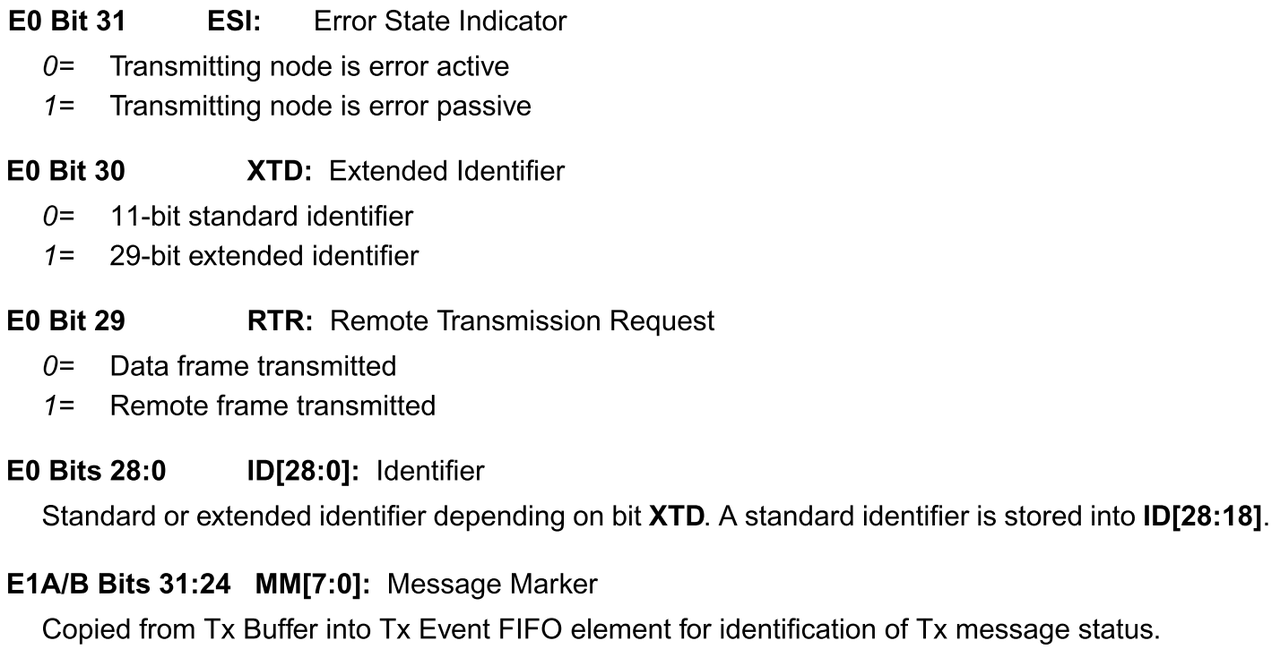

2.3.4.Tx Event FIFO Element

每个 element 都存储有关已传输 Messages 的信息。通过读取 Tx Event FIFO,host CPU 可以按照 Messages 传输的顺序获得这些信息。有关 Tx Event FIFO 的状态信息可从寄存器 TXEFS 中获取。

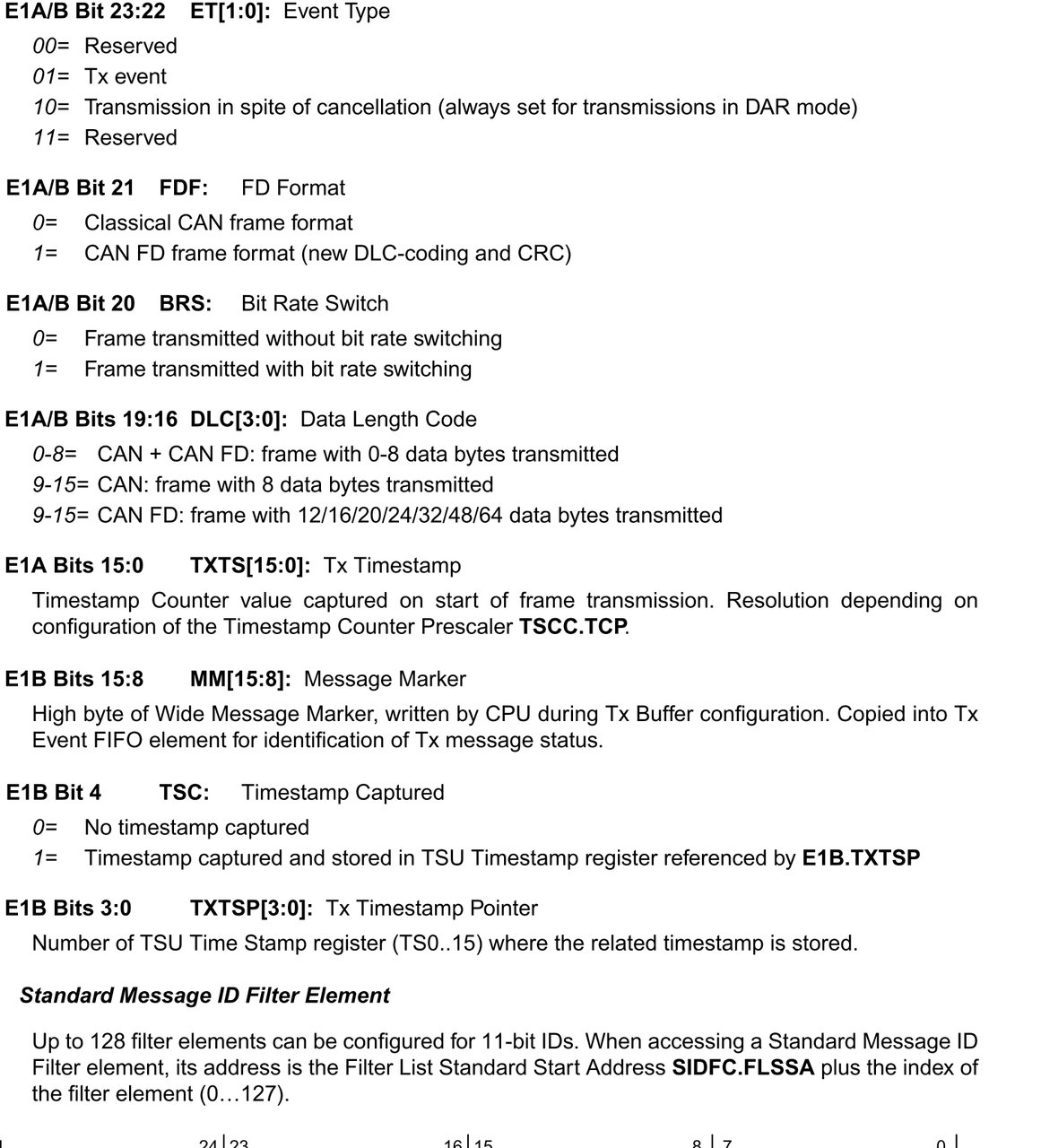

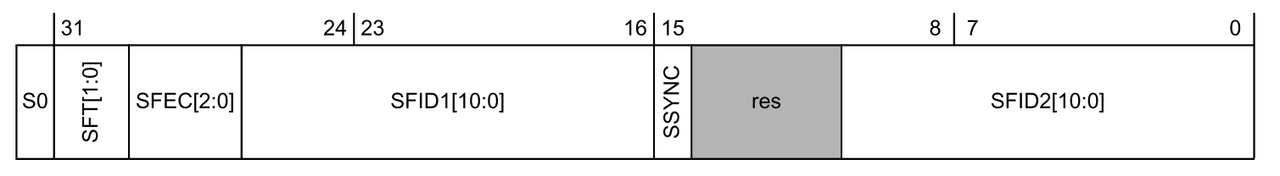

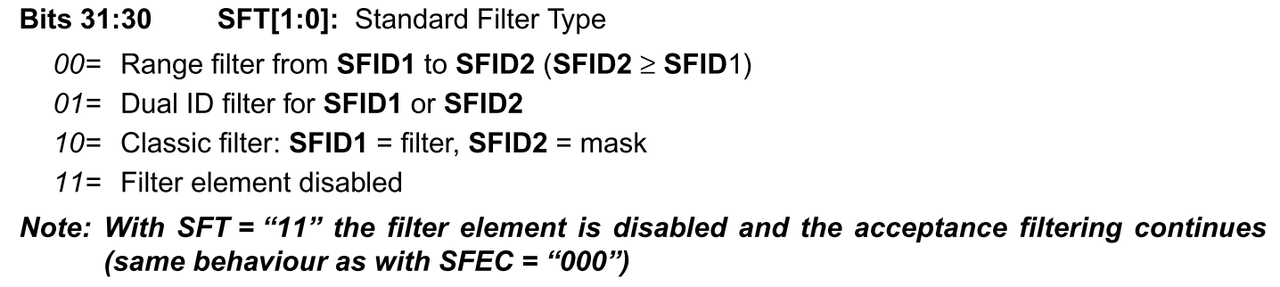

2.3.5.Standard Message ID Filter Element

最多可为 11-bit ID 配置 128 个 filter elements。访问 Standard Message ID Filter element 时,其地址是 Filter List Standard Start Address (SIDFC.FLSSA) 加上 filter element 的 Index(0...127)。

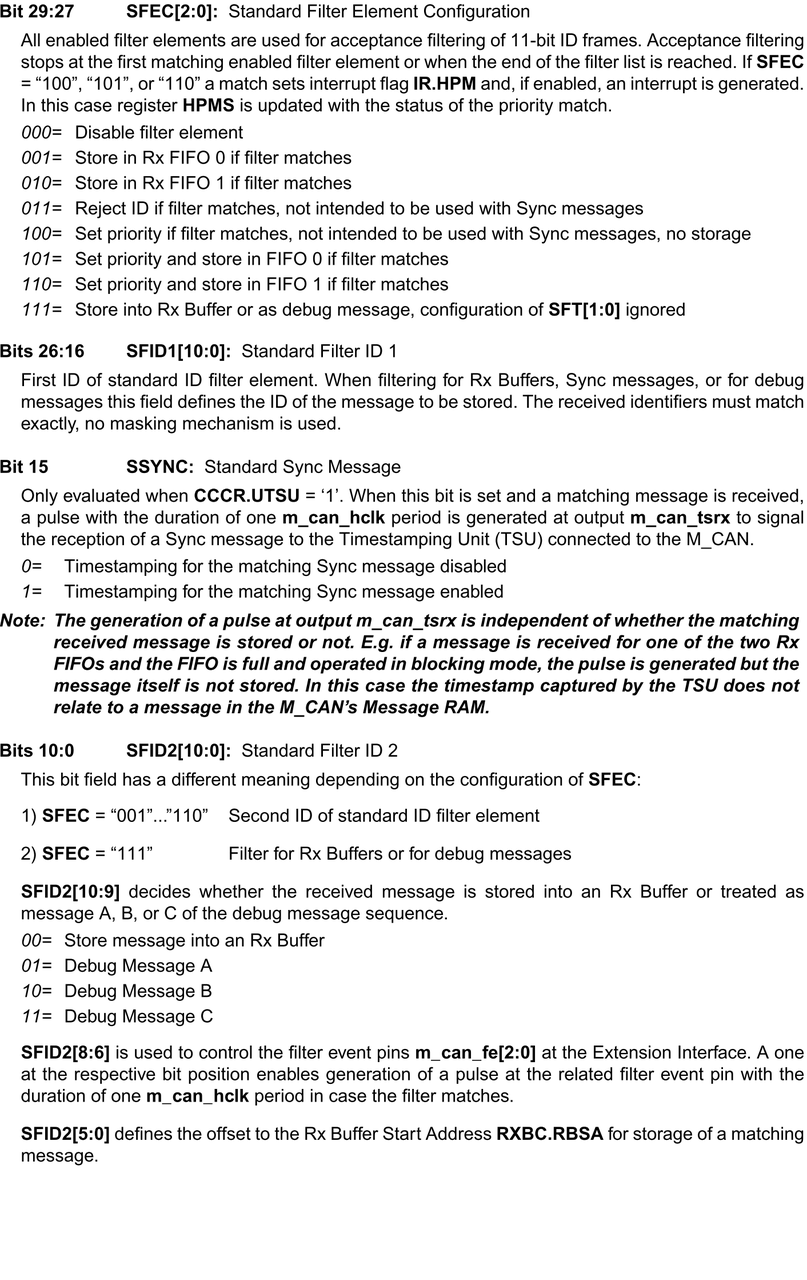

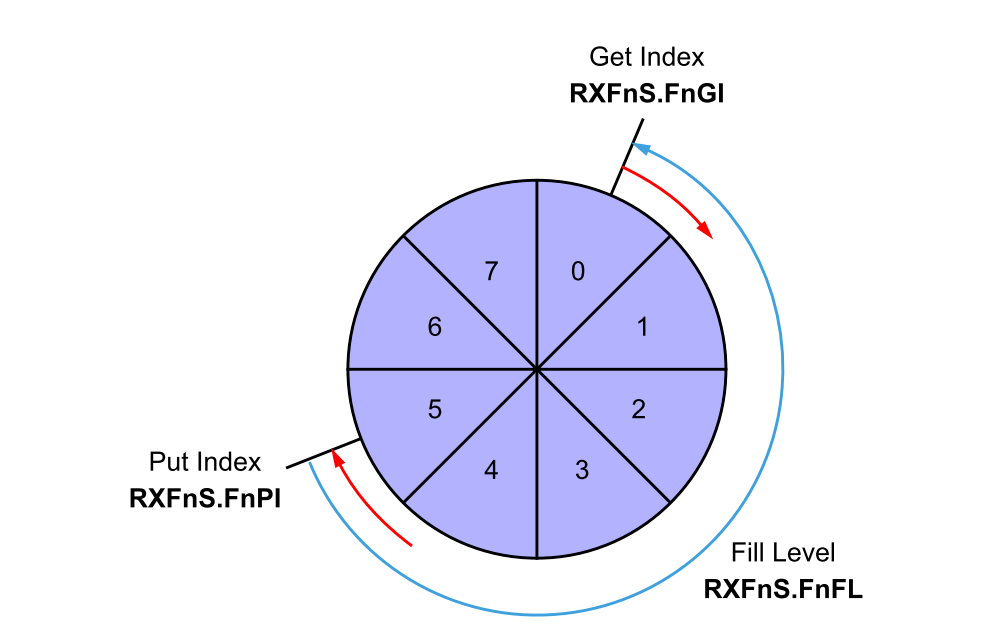

2.3.6.Extended Message ID Filter Element

最多可为 29-bit ID 配置 64 个 filter elements。访问 Extended Message ID Filter element 时,其地址是 Filter List Extended Start Address (XIDFC.FLESA) 加上 filter element 的 Index(0...63)。

3.Functional Description

3.1.Operating Modes

3.1.1.Software Initialization

当检测到 Message RAM 中存在未纠正的位错误时,或通过软件或硬件复位置位 CCCR.INIT,或通过 Bus_Off,启动软件初始化。当 CCCR.INIT 被设置时,CAN 总线的 Message 传输停止,CAN 总线输出 m_can_tx 的状态为隐性(高电平)。错误管理逻辑 EML 的计数器保持不变。设置 CCCR.INIT 不会更改任何配置寄存器。复位 CCCR.INIT 完成软件初始化。之后,比特流处理器 BSP 将自身与 CAN 总线上的数据传输同步,等待出现连续 11 个隐性比特序列 (≡ Bus_Idle),然后才能参与总线活动并开始消息传输。

只有当 CCCR.INIT 和 CCCR.CCE 两位都被设置时(受保护写入),才能访问 M_CAN 配置寄存器。

只有在 CCCR.INIT = '1' 时才能设置/重置 CCCR.CCE。复位 CCCR.INIT 时,CCCR.CCE 将自动复位。

设置 CCCR.CCE 时,将重置以下寄存器

-

HPMS - High Priority Message Status

-

RXF0S - Rx FIFO 0 Status

-

RXF1S - Rx FIFO 1 Status

-

TXFQS - Tx FIFO/Queue Status

-

TXBRP - Tx Buffer Request Pending

-

TXBTO - Tx Buffer Transmission Occurred

-

TXBCF - Tx Buffer Cancellation Finished

-

TXEFS - Tx Event FIFO Status

3.2.Rx Handling

Rx Handler 控制 acceptance filtering、将接收到的消息传输到 Rx Buffers 或两个 Rx FIFO 之一,以及 Rx FIFO 的 Put and Get Indices。

3.2.1.Acceptance Filtering

M_CAN 提供了配置两组 acceptance filters 的可能性,一组用于标准标识符,一组用于扩展标识符。这些 filters 可以分配给 Rx Buffer 或 Rx FIFO 0,1。对于 acceptance filters,每个筛选器列表从 element #0 开始执行,直到第一个匹配 element 出现。Acceptance filters 停止在第一个匹配 element。剩下的 filter elements 不会为此 Message 进行匹配。

主要特点是:

-

每个 filter element 可以配置为

-

范围筛选器

-

一个或两个 dedicated IDs 的筛选器

-

经典位掩码滤波器

-

每个 filter element 都可配置为接受或拒绝筛选

-

每个 filter element 都可以单独启用/禁用

-

筛选器按顺序检查,执行以出现第一个匹配的 filter element 停止

相关配置寄存器是:

-

全局滤波器配置 GFC

-

标准 ID 滤波器配置 SIDFC

-

扩展 ID 滤波器配置 XIDFC

-

扩展 ID 和掩码 XIDAM

根据 filter element(SFEC/EFEC)的配置,匹配会触发以下操作之一:

-

将接收到的帧存储在 FIFO 0 或 FIFO 1 中

-

将接收到的帧存储在 Rx buffer 中

-

将接收到的帧存储在 Rx Buffers 中,并在滤波器事件引脚上产生脉冲

-

拒绝接收到的帧

-

设置高优先级消息中断标志 IR。 HPM

-

设置高优先级消息中断标签 IR。 HPM 并将接收到的帧存储在 FIFO 0 或 FIFO 1 中

接收到完整标识符后开始 Acceptance filtering。Acceptance filtering 完成后,如果找到匹配的 Rx Buffer 或 Rx FIFO,则 Message Handler 开始将接收到的 Message 数据以 32 bit 为单位写入匹配的 Rx Buffer 或 Rx FIFO。如果 CAN protocol controller 检测到错误情况(例如 CRC 错误),则丢弃此消息,并对受影响的 Rx Buffer 或 Rx FIFO 产生以下影响:

Rx buffer

未设置匹配 Rx buffer 的新数据标志,但 Rx Buffer(部分)被接收到的数据覆盖。

Rx FIFO

匹配 Rx FIFO 的 Put index 不更新,但相关 Rx FIFO element(部分)被接收到的数据覆盖。

3.2.1.1.Range Filter

该筛选器匹配其 Message ID 在 SF1ID/SF2ID 或者 EF1ID/EF2ID 所定义的范围内所有接收到的帧。

范围筛选与扩展帧一起使用时有两种可能性:

-

EFT = “00”: 在应用范围筛选器之前,先将接收到的帧的 Message ID 与扩展 ID 与掩码 (XIDAM) 进行 AND 运算

-

EFT = “11”: 扩展 ID 和掩码 (XIDAM) 不用于范围筛选

3.2.1.2.Filter for specific IDs

一个 filter element 可配置为筛选一个或两个特定的 Message ID。要对一个特定的 Message ID 进行筛选,筛选元素必须配置为 SF1ID = SF2ID 或者 EF1ID = EF2ID。

3.2.1.3.Classic Bit Mask Filter

经典位掩码筛选旨在通过屏蔽接收到的 Message ID 的单个位来筛选 Message ID 组。在传统的位掩码筛选中,SF1ID/EF1ID 用作 Message ID 筛选器,而 SF2ID/EF2ID 用作筛选掩码。

如果所有屏蔽位都为 1,则只有当接收到的 Message ID 与 Message ID 筛选器相同时才会发生匹配。如果所有屏蔽位都为 0,则所有 Message ID 都匹配。

现有 Message 0x1B1、0x1F0、0x1B7 配置为 Basic 类型

因为 BasicCan 类型的邮箱接收的是一段 ID 范围的 Message ,以上三条 Message 取段范围为 0x1B0 -- 0x1F7

则:

0x1B0: 0001 1011 0000

0x1F7: 0001 1111 0111

求掩码的关键,1 关心,0 不关心【关心就是这一位必须是 0 或者 1;不关心就是 0,1 随便】

step 1

1:0001,每位都需要关心(因为需要确定 ID 的第一位是 1),所以掩码:0111

step 2

B - F :1011 -- 1111 ,就需要关心 1011 -- 1111 红色位不变,黑色位 0,1 随便,所以掩码:1011

step 3

0 -- 7 :0000 -- 0111,关心 0000 -- 0111,所以掩码:1000;

step 4

最终掩码为:0111 1011 1000 filter mask: 1976

根据 Id , Filter mask 和 Filter code 的关系 :ID & Filter mask = Filter Code

Filter Code : 433

需要注意的是 CAN ID 的:

标准标识符(11 位) :前 11 位用于标识消息的 ID,最高位为 0。这种类型的 ID 支持最多 2048 个不同的 ID

扩展标识符(29 位) :前 29 位用于标识消息的 ID,最高位为 1,这种类型的 ID 支持最多 536870912 个不同的 ID

所以在上面 step1 中,因为是标准标识符,所以最高位一直是 0,

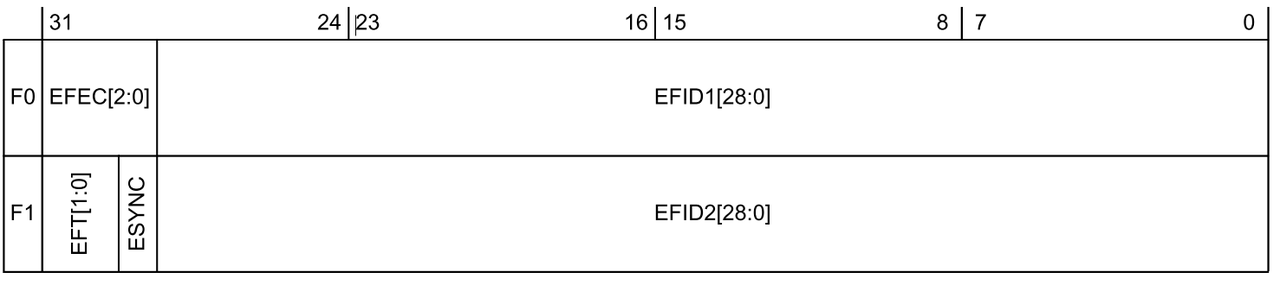

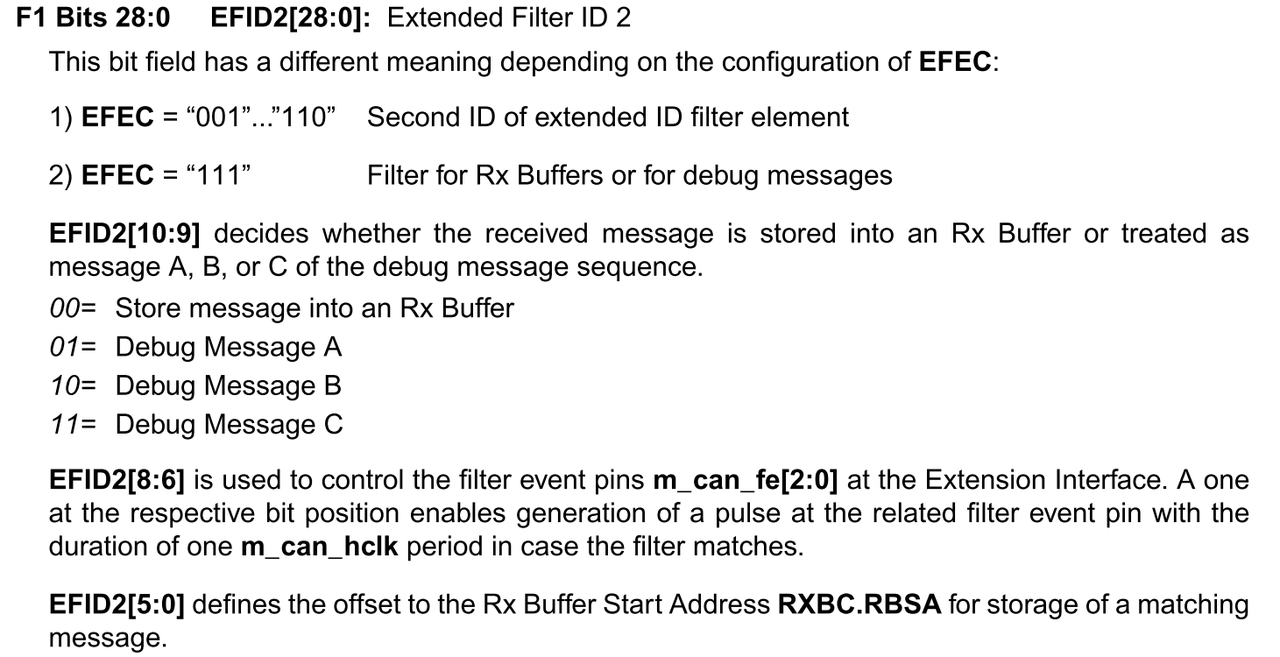

3.2.1.4.Standard Message ID Filtering

下图显示了标准 Message ID(11 位标识符)转换的流程。

由全局筛选器配置 GFC 和标准 ID 筛选器配置 SIDFC 控制,将接收到的帧的 Message ID、远程传输请求位 (RTR) 和标识符扩展位 (IDE) 与配置的 filter elements 列表进行比较。

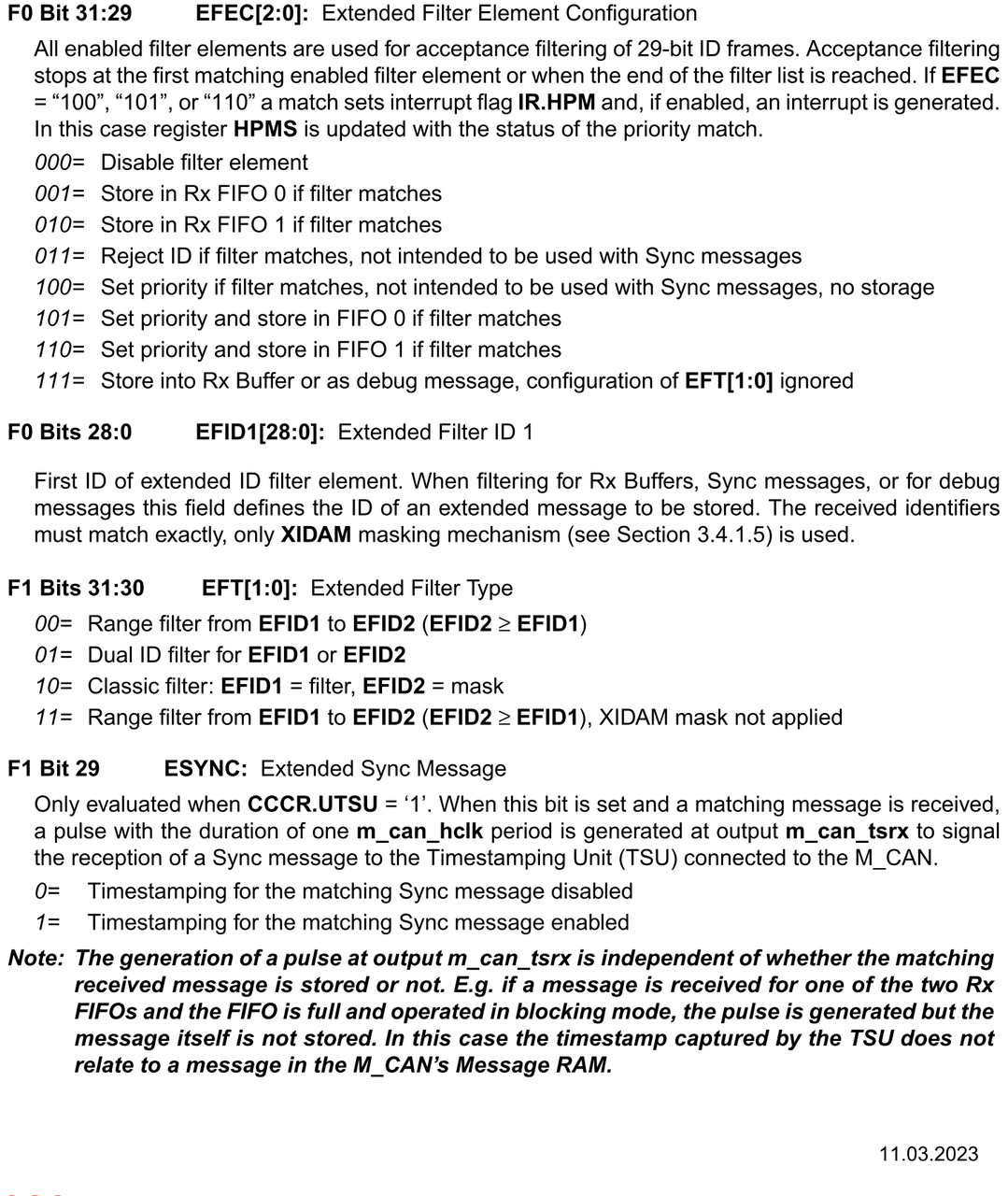

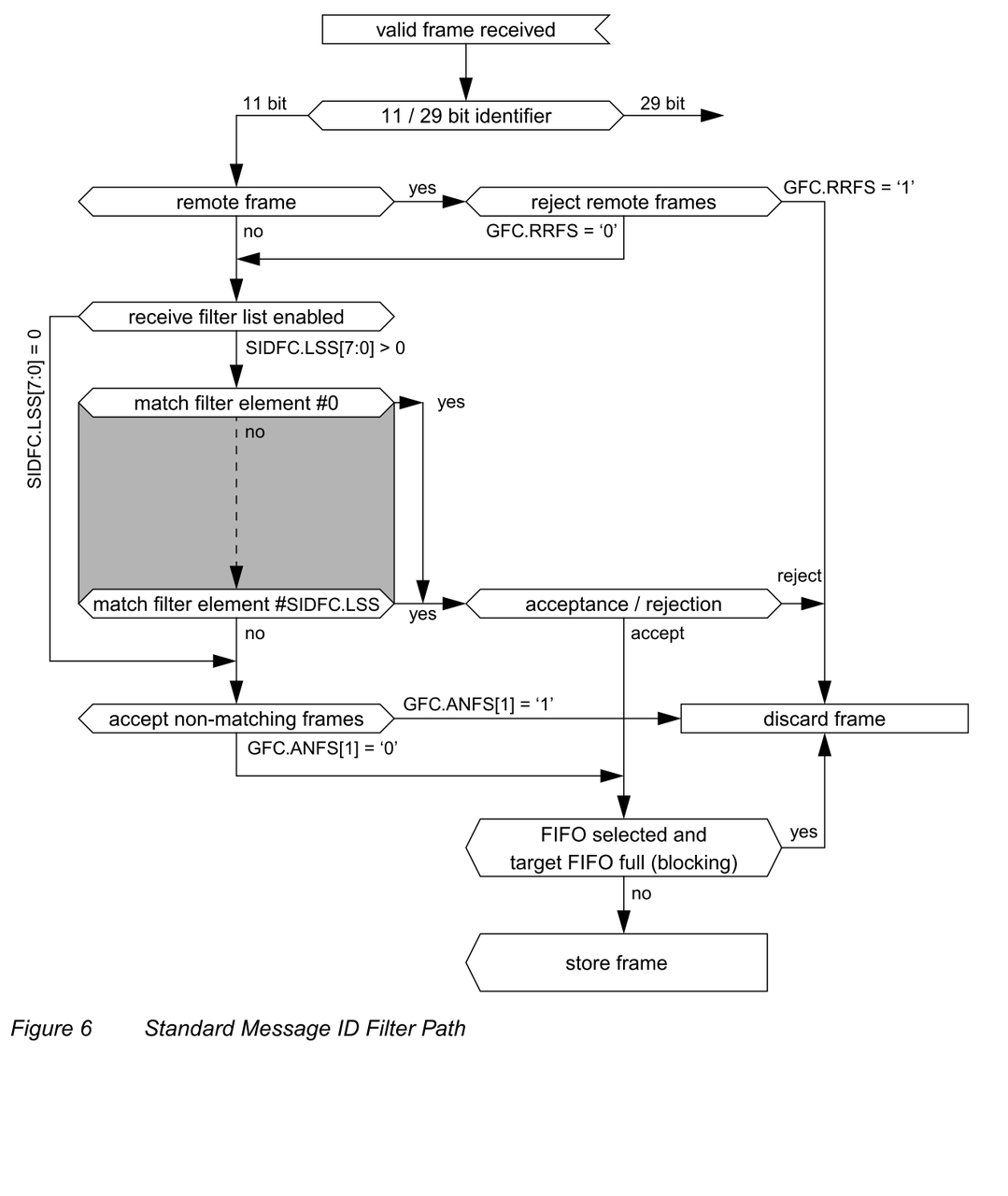

3.2.1.5.Extended Message ID Filtering

下图显示了扩展 Message ID(29 位标识符)转换的流程。

由全局筛选器配置 GFC 和扩展 ID 筛选器配置 XIDFC 控制,将接收到的帧的 Message ID、远程传输请求位 (RTR) 和标识符扩展位 (IDE) 与配置的 filter elements 列表进行比较。

扩展 ID 与掩码 XIDAM 在执行筛选器列表之前与接收到的标识符进行 AND。

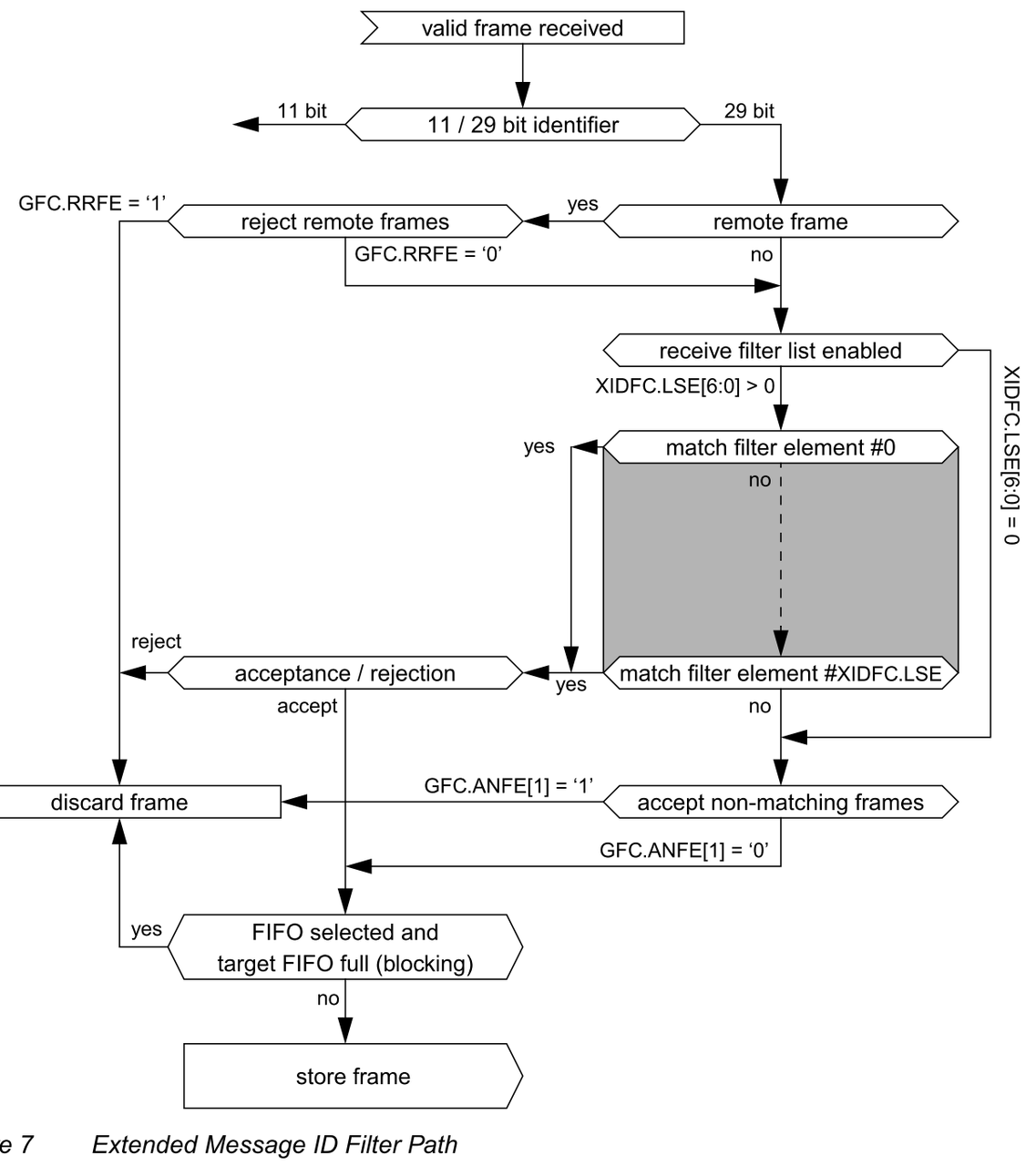

3.2.2.Rx FIFOs

Rx FIFO 0 和 Rx FIFO 1 最多可分别配置为 64 个 element。两个 Rx FIFO 的配置通过寄存器 RXF0C 和 RXF1C 完成。

通过 acceptance filtering 的接收 Message 将按照匹配 filter element 的设置传输到 Rx FIFO。

为了避免 Rx FIFO 溢出,可以使用 RxFIFO 水印。当 Rx FIFO 填充级别达到 RXFnC。 FnWM 配置的 RxFIFO 水印时,设置中断标志 IR.RFnW。

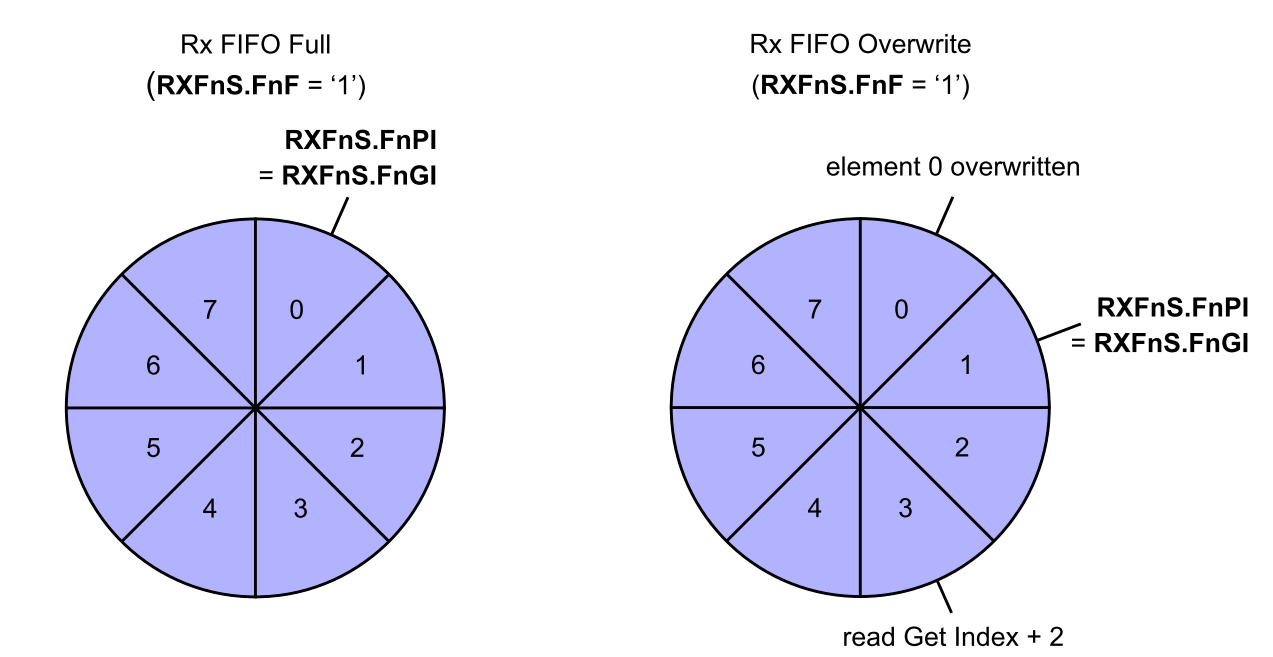

当 Rx FIFO Put Index 达到 Rx FIFO Get Index 时,RXFnS.FnF 将发出 Rx FIFO 满的信号。此外,还将设置中断 flag IR.RFnF。

从 Rx FIFO 读取数据时,必须将 Rx FIFO Get Index(RXFnS.FnGI )× FIFO Element Size 与相应的 Rx FIFO 起始地址( RXFnC.FnSA )相加。

3.2.2.1.Rx FIFO Blocking Mode

Rx FIFO 阻塞模式由 RXFnC.FnOM = '0' 配置。这是 Rx FIFO 的默认运行模式。

当达到 Rx FIFO 满的条件(RXFnS.FnPI = RXFnS.FnGI)时,将不再向相应的 Rx FIFO 写入 Message ,直到至少读出一条 Message 且 Rx FIFO Get Index 递增。RxFnS.FnF = '1' 表示 Rx FIFO 已满。此外,还将设置中断 flag IR.RFnF。

如果在相应的 Rx FIFO 已满的情况下接收到 Message ,则会丢弃该 Message ,并通过 RXFnS.RFnL = '1' 发出 Message 丢失信号。此外,还将设置中断 flag IR.RFnL。

3.2.2.2.Rx FIFO Overwrite Mode

Rx FIFO 覆盖模式由 RXFnC.FnOM = '1' 配置。

当 RxFIFO 满(RXFnS.FnPI = RXFnS.FnGI)时,RXFnS.FnF = '1',FIFO 接收的下一条 Message 将覆盖 FIFO 最旧的 Message 。Put and get index 均递增 1。

当 Rx FIFO 以覆盖模式运行,并发出 Rx FIFO 满的信号时,至少应从 get index + 1 开始读取 Rx FIFO 元素。

这样做的原因是,当 CPU 正在从 Message RAM 读取数据(put index)时,可能会发生接收到的 Message 被写入 Message RAM(get index)的情况。在这种情况下,可能会从相应的 Rx FIFO 单元读取不一致的数据。从 Rx FIFO 读取数据时,为获取索引添加偏移量可避免这一问题。偏移量取决于 CPU 访问 Rx FIFO 的速度。下图显示,读取 Rx FIFO 时,获取索引的偏移量为 2。在这种情况下,存储在元素 1 和 2 中的两条 Message 将丢失。

从 Rx FIFO 读取数据后,必须将最后读取的元素编号写入 Rx FIFO 确认索引 RXFnA.FnA。这将使 get index 递增到该元素编号。如果该 Rx FIFO 元素的 put index 尚未递增,Rx FIFO 满状态将被重置(RXFnS.FnF = '0')。

3.2.3.Dedicated Rx Buffers

M_CAN 支持多达 64 个 Dedicated Rx Buffers。Dedicated Rx Buffers 部分的起始地址通过 RXBC.RBSA 设置。

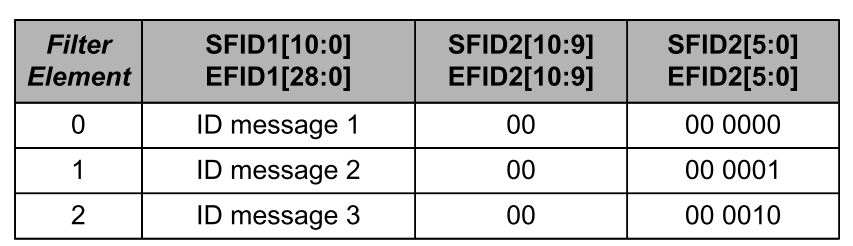

必须为每个 Rx Buffer 配置一个 SFEC / EFEC = “111” 和 SFID2 / EFID2[10:9] = “00” 的 Standard or Extended Message ID Filter Element。

接收到的 Message 被 filter element 接受后, Message 被存储到 filter element 引用的 Message RAM 中的 Rx buffer 中。格式与 Rx FIFO element 相同。此外,此外,中断寄存器中的 flag IR.DRX (存储在 Dedicated Rx Buffer 中的 Message)已被设置。

将匹配的接收 Message 的最后一个字节写入 Message RAM 后,寄存器 NDAT1,2 中相应的 New Data flag 将被设置。只要 New Data flag 被设置,就会锁定相应的 Rx Buffer,防止接收到的匹配帧被覆盖。New Data flag 必须由 CPU 通过在相应位上写入 “1 ”来重置。

当一个 Rx Buffer 的 New Data flag 被设置时,引用该特定 Rx Buffer 的 Message ID Filter Element 将不匹配其他任何 Message, Message acceptance filtering 继续进行。后续的 Message ID Filter Element 可能会导致接收到的 Message 被存储到另一个 Rx Buffer 或 Rx FIFO 中,也可能会拒绝该信息,具体取决于过滤的配置。

3.2.3.1.Rx Buffer Handling

-

重置中断标志 IR。 DRX

-

读取新数据寄存器

-

读取 Message RAM 中的 Message

-

重置已处理 Message 的 New Data flag

3.3.Tx Handling

Tx Handler 处理 dedicated Tx Buffers、Tx FIFO 和 Tx Queue 的传输请求。它控制向 CAN Core、Put 和 Get Indices 以及 Tx Event FIFO 传输发送 Message 。最多可为 Message 传输设置 32 个 Tx buffer。传输的 CAN 模式(Classic CAN or CAN FD)可为每个 Tx buffer 单独配置。

当 Tx Buffer Request Pending 寄存器 TXBRP 更新时,Tx Handler 开始对 Message RAM 进行 Tx 扫描,检查优先级最高的待处理 Tx 请求(具有最小 Message ID 的 Tx Buffer)。TXBRP 在传输完成后更新,或在 host 通过写入 TXBAR 请求传输后更新,或在 host 通过写入 TXBCR 取消待处理传输后更新。

当有新的扫描结果时,就会更新临时缓冲区,该缓冲区中保存着两个发送优先级最高的 Message 的前四个 RAM 字。Tx 扫描和预加载所需的时间取决于 host 时钟频率、配置的 Tx buffer 数量以及连接到 Message RAM 的 M_CAN 数量。

由于 Message RAM 的 Tx 扫描需要一些时间,因此可能出现以下情况:

在正在进行的传输/接收完成之前预加载的临时缓冲区:预加载的 Tx Message 的传输在第一时间开始

在当前发送/接收完成之前未完成临时缓冲区的预加载:Tx Message 不能在第一时间启动。在这种情况下,另一个节点可以开始传输,而不必对 M_CAN 的传输消息进行仲裁。如果另一个 Message 具有较低的优先级,这可能被视为外部优先级反转。

3.3.1.Transmit Pause

发送暂停功能适用于 CAN 系统,在该系统中,CAN Message 标识符被(永久)指定为指定值,且不能轻易更改。这些 Message 标识符的 CAN 仲裁优先级可能高于其他已定义的 Message ,而在具体应用中,它们的相对仲裁优先级应该是相反的。这可能会导致这样一种情况,即一个 ECU 发送大量 CAN Message ,导致另一个 ECU 的 CAN Message 延迟,因为其他 Message 的 CAN 仲裁优先级较低。

例如,如果 CAN ECU-1 启用了发送暂停功能,并且其应用软件要求它发送四条 Message ,那么在第一条 Message 发送成功后,它将等待两个 CAN bit 的总线空闲时间,然后才允许开始发送下一条 Message 。如果其他 ECU 有待处理的 Message ,这些 Message 将在空闲时间内启动,而不需要与 ECU-1 的下一个 Message 进行仲裁。收到 Message 后,一旦收到的 Message 释放 CAN 总线,ECU-1 就可以开始下一次传输。

发送暂停功能由 bit CCCR.TXP 控制。如果设置了该 bit,M_CAN 在每次成功发送 Message 后,都会暂停两个 CAN bit 时间,然后再开始下一次发送。这样,即使网络中其他 CAN 节点的 Message 标识符优先级较低,它们也能传输 Message 。默认为禁用传输暂停(CCCR.TXP = '0')。

这一功能可避免来自单个节点的突发传输,并可防止 “babbling idiot ”情况,即应用程序错误地请求过多传输。

3.3.2.Dedicated Tx Buffers

Dedicated Tx Buffers 用于在 host CPU 的完全控制下传输 Message 。每个 Dedicated Tx Buffer 都有一个特定的 Message ID。如果多个 Tx buffer 配置了相同的 Message ID,则先传输 buffer 编号最小的 Tx buffer。这些 Tx buffer 应按升序请求,buffer 编号最低者优先。另外,也可以通过对 TXBAR 的单次写入访问,同时请求使用相同 Message ID 配置的所有 Tx buffer。

如果数据部分已更新,则通过 TXBAR。 ARn 的添加请求请求传输。所请求的 Message 在内部与来自可选 Tx FIFO 或 Tx Queue 的 Message 进行仲裁,在外部与 CAN 总线上的 Message 进行仲裁,并根据其 Message ID 发送出去。

一个 Dedicated Tx Buffer 在 Message RAM 中分配 Element 的大小为 32-bit words。因此, Dedicated Tx Buffer 在 Message RAM 中的起始地址是通过将 transmit buffer index(0...31)× Element Size 加到 Tx Buffer Start Address (TXBC.TBSA) 来计算。

3.3.3.Tx FIFO

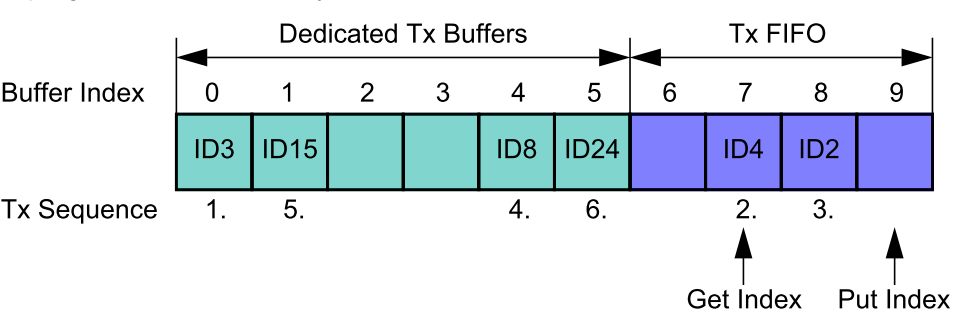

通过将 TXBC.TFQM 设置为 “0 ”来配置 Tx FIFO 操作。存储在 Tx FIFO 中的 Message 从 Get Index TXFQS.TFGI 所引用的 Message 开始传输。每次传输后, Get Index 循环递增,直到 Tx FIFO 为空。Tx FIFO 可以按照 Message 写入 Tx FIFO 的顺序,从不同的 Tx buffer 传输具有相同 Message ID 的 Message 。M_CAN 计算 Tx FIFO Free Level TXFQS.TFFL 时,将其作为 Get and Put Index 之间的差值。它表示可用(空闲)Tx FIFO 元素的数量。

新发送的 Message 必须从 Put Index TXFQS.TFQPI 引用的 Tx Buffer 开始写入 Tx FIFO。添加请求会将 Put Index 递增到下一个空闲的 Tx FIFO 元素。当 Put Index 达到 Get Index 时,将发出 Tx FIFO 满(TXFQS.TFQF = '1')信号。在这种情况下,不应再向 Tx FIFO 写入 Message ,直到下一条 Message 传送完毕且 Get Index(获取索引)递增。

当单个 Message 被添加到 Tx FIFO 时,通过向与 Tx FIFO 的 Put Index 所引用的 Tx Buffer 相关的 TXBAR 位写入 “1 ”来请求传输。

当多条(n)信息被添加到 Tx FIFO 时,它们将被写入从 Put Index 开始的连续 n 个 Tx buffer。然后通过 TXBAR 请求传输,同时,Put Index 按 n 循环递增。请求的 Tx buffer 数量不应超过 Tx FIFO 空闲级别显示的空闲 Tx buffer 数量。

当取消 Get Index 所引用的 Tx buffer 的传输请求时,Get Index 将递增到下一个有待处理传输请求的 Tx buffer,并重新计算 Tx FIFO Free Level。当传输取消应用于任何其他 Tx buffer 时,Get Index 和 FIFO Free Level 保持不变。

一个 Tx FIFO element 在 Message RAM 中分配 Element 的大小为 32-bit words。因此, Tx FIFO element 在 Message RAM 中的起始地址是通过将 Tx FIFO/Queue Put Index TXFQS.TFQPI (0…31) × Element Size 加到 Tx Buffer Start Address (TXBC.TBSA) 来计算。

3.3.4.Tx Queue

通过将 TXBC.TFQM 设置为 “1 ”来配置 Tx Queue 操作。存储在 Tx Queue 中的 Message 将从 Message ID 最低(优先级最高)的 Message 开始传输。如果用相同的 Message ID 配置了多个 Queue Buffer,则传输顺序取决于存储要传输的 Message 的 buffer 编号。由于这些 Message 编号取决于 Put Index 的当前状态,因此无法预测传输顺序。

新 Message 必须写入由 Put Index TXFQS.TFQPI 引用的 Tx buffer。Put Index 始终指向 Tx Queue 中 buffer 编号最小的空闲 buffer。如果如果 Tx Queue 已满(TXFQS.TFQF = '1'),则 Put Index 无效,在至少一个请求的 Message 被发送或一个待处理的传输请求被取消之前,不得向 Tx Queue 写入其他 Message 。

应用程序可使用寄存器 TXBRP 代替 Put Index,并可将消息放置到任何 Tx buffer 中,而无需等待传输请求。

一个 Tx Queue element 在 Message RAM 中分配 Element 的大小为 32-bit words。因此, Tx Queue element 在 Message RAM 中的起始地址是通过将 Tx FIFO/Queue Put Index TXFQS.TFQPI (0…31) × Element Size 加到 Tx Buffer Start Address (TXBC.TBSA) 来计算。

3.3.5.Mixed Dedicated Tx Buffers / Tx FIFO

在这种情况下,Message RAM 中的 Tx Buffer 部分被细分为一组 Dedicated Tx Buffer 和 一个 Tx FIFO。Dedicated Tx Buffer 的数量由 TXBC.NDTB 确定。分配给 Tx FIFO 的 Tx Buffer 数量由 TXBC.TFQS 确定。如果 TXBC.TFQS 设置为零,则只使用 Dedicated Tx Buffer。

发送优先级:

- 扫描 Dedicated Tx Buffer 和最旧待处理 Tx FIFO Buffer(由 TXFS.TFGI 引用)

-Message ID 最小的 Buffer 优先级最高,下一个发送

3.3.6.Mixed Dedicated Tx Buffers / Tx Queue

在这种情况下,Message RAM 中的 Tx Buffer 部分被细分为一组 Dedicated Tx Buffer 和一个 Tx Queue。Dedicated Tx Buffer 的数量由 TXBC.NDTB 确定。Tx Queue Buffer 的数量由 TXBC.TFQS 确定。如果 TXBC.TFQS 设置为零,则只使用 Dedicated Tx 缓冲区。

发送优先级:

-

扫描所有已激活传输请求的 Tx buffer

-

Message ID 最小的 Tx buffer 优先级最高,下一个被发送

3.3.7.Transmit Cancellation

M_CAN 支持发送取消功能。该功能特别适用于网关应用和基于 AUTOSAR 的应用。要取消来自 Dedicated Tx Buffer 或 Tx Queue Buffer 的传输请求,Host 必须在寄存器 TXBCR 的相应位(=number of Tx Buffer)上写入 “1”。传输取消不适用于 Tx FIFO 操作。

将寄存器 TXBCF 的相应位设置为 “1”,即表示取消成功。

如果在 Tx buffer 传输过程中请求取消传输,只要传输仍在进行,相应的 TXBRP 位就会保持置位。如果传输成功,则相应的 TXBTO 和 TXBCF 位被置位。如果传输不成功,则不重复传输,只设置相应的 TXBCF 位。

如果一个待发送的 Message 在开始发送前被取消,那么即使该节点还有另一个 Message 待发送,也会有一个短暂的不发送时间。这可能会使另一个节点发送优先级低于本节点第二个 Message 的 Message 。

3.3.8.Tx Event Handling

为了支持 Tx Event Handling,M_CAN 实现了一个 Tx Event FIFO。M_CAN 在 CAN 总线上传输 Message 后,Message ID 和时间戳将存储在 Tx Event FIFO element 中。要将 Tx Event 链接到 Tx Event FIFO element,需要将传输的 Tx Buffer 中的 Message Marker 复制到 Tx Event FIFO element 中。

Tx Event FIFO 最多可配置为 32 个 element 。

Tx Event FIFO 的目的是将发送状态信息的处理与发送 Message 的处理分离开来,即 Tx Buffer 只保存要发送的 Message ,而发送状态则单独存储在 Tx Event FIFO 中。这样做的好处是,尤其是在运行动态管理的发送队列时,Tx Buffer 可以在发送成功后立即用于处理新的 Message。在覆盖 Tx Buffer 之前,无需保存 Tx Buffer 中的发送状态信息。

当 IR.TEFF 发出 Tx Event FIFO 满的信号时,不会再向 Tx Event FIFO 写入任何 element ,直到至少读出一个 element 且 Tx Event FIFO Get Index 递增。如果在 Tx Event FIFO 已满时发生 Tx Event,该 Event 将被丢弃并设置中断 flag IR.TEFL。

为了避免 Tx Event FIFO 溢出,可以使用 Tx Event FIFO 水印。当 Tx Event FIFO 的满载水平达到 TXEFC.EFWM 配置的 Tx Event FIFO 水印时,将设置中断信号 IR.TEFW。

从 Tx Event FIFO 读取数据时,必须将两次 Tx Event FIFO Get Index(TXEFS.EFGI) 与 Tx Event FIFO 起始地址 TXEFC.EFSA 相加。

3.3.9.FIFO Acknowledge Handling

Rx FIFO 0、Rx FIFO 1 和 Tx Event FIFO 的 Get Indices 通过写入相应的 FIFO Acknowledge Index 来控制。写入 FIFO Acknowledge Index 将把 FIFO Get Index 设置为 FIFO Acknowledge Index + 1,从而更新 FIFO Fill Level。有两种使用情况:

当从 FIFO 只读取了一个 element 时(即 Get Index 所指向的 element )时,该 Get Index 将被写入 FIFO Acknowledge Index 。

从 FIFO 中读取一系列 element 后,只需在读取序列结束时写入一次 FIFO Acknowledge Index(值:最后读取 element 的 Index ),即可更新 FIFO 的 Get Index。

由于 CPU 可以自由访问 M_CAN 的 Message RAM,因此在以任意顺序(不考虑 Get Index)读取 FIFO element 时必须特别小心。当从两个 Rx FIFO 中的一个读取高优先级 Message 时,这一点可能很有用。在这种情况下,不应写入 FIFO 的 Get Index,因为这会将 Get Index 设置到错误的位置,并改变 FIFO 的填充级别。在这种情况下,一些较早的 FIFO element 将丢失。

565

565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?