一.本章概述

本章讨论存储器容量的性能指标:MAR和MDR;CPU的性能指标:时钟周期T,主频f,CPI,CPU执行时间和IPS。

二、存储器性能指标

MAR:位数反映存储单元数量

MDR:位数反应存储单元大小

2.1 对于存储单元,1.2已经详细讲过,在此只回忆一下。

内存比作一栋楼,存储单元就是这栋楼里的房间,存储地址就是门牌号。每个存储单元中存放着一串二进制数,如01001000。那么这串数字叫存储字,这串数字的长度叫存储字长(这里是8位)。

2.2 这部分是新知识。通过2.1知道了存储字长,它是保存在存储单元中的二进制数的长度,也就是位数。现在引入机器字长和指令字长,机器字长是重点。

机器字长:CPU内部与整数运算相关的寄存器中保存的字长,反映了计算机能直接处理的二进制数据的位数。例如通用寄存器(ACC,MQ,X)这些都是参与了整数运算的寄存器,这些寄存器中保存的二进制数(如01001000)的位数(8位)。

指令字长:机器指令中二进制代码位数。例如IR(存放当前指令的寄存器)中存放的二进制数的位数。

早期的计算机中,机器字长,指令字长和存储字长是相等的,不过随着计算机的发展,三者是可变的(32位,64位),但必须是字节(8bit)的整数倍。

三、CPU性能指标

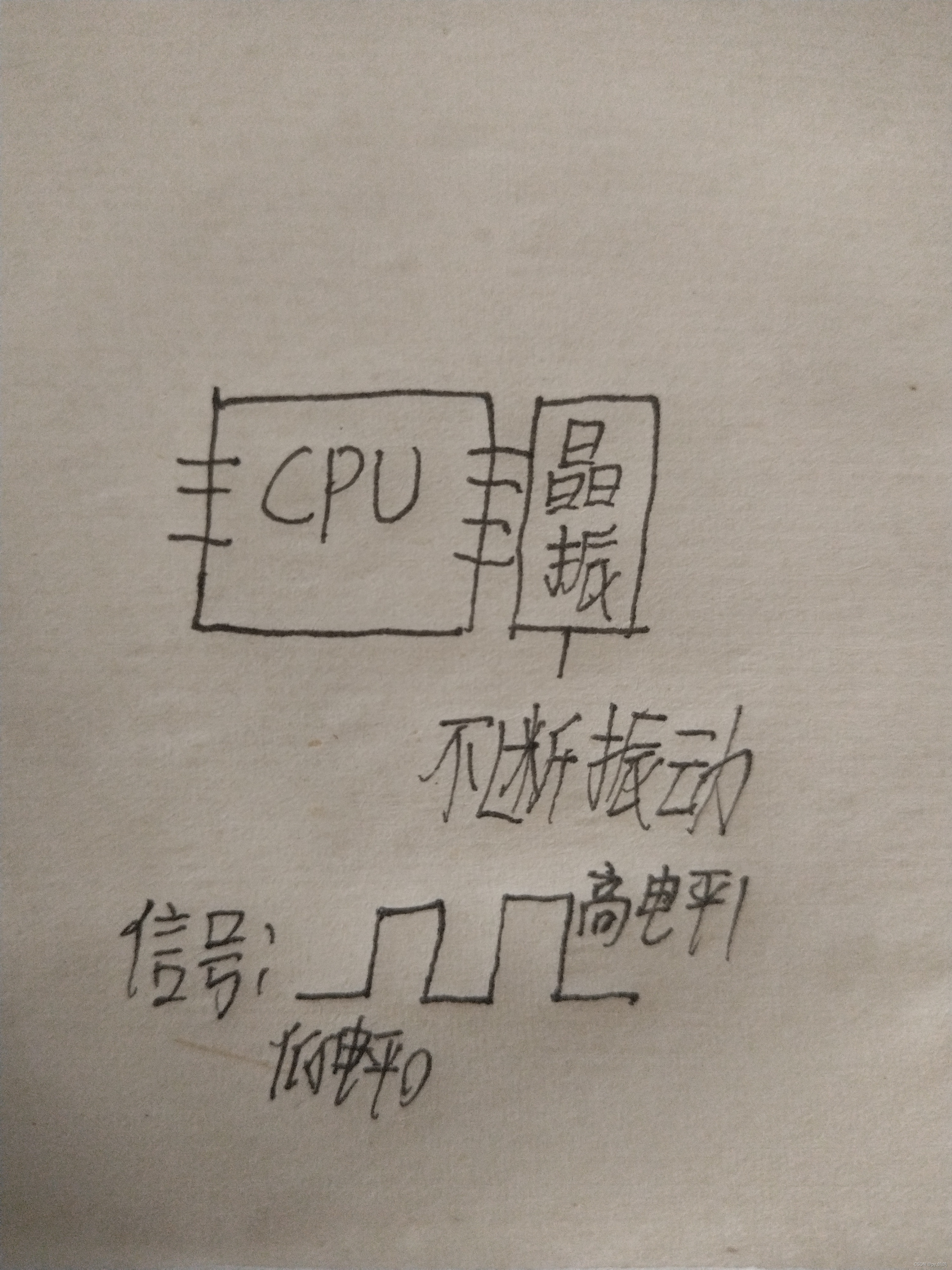

3.1 背景:CPU由一些电子元件组成,将组装好的CPU接上一个电子元件晶振,晶振会不断震动,像心脏一样。通过震动产生信号,信号分为低电平和高电平。

3.2 性能指标

脉冲:脉冲信号是一种周期性的信号,其特点是信号在某一时刻从某一基准值跃变到另一个基准值,然后又返回原基准值。(例如这里从低电平到高电平,再回到低电平)

时钟周期T:脉冲信号之间的时间间隔(一次脉冲所花费的时间,设一次脉冲花费0.01秒,那么T就是0.01s)

主频f:CPU使用的时钟脉冲频率,换种说法就是单位时间内所产生的脉冲个数,单位是赫兹。(和T的假设一样,设一次脉冲花费0.01秒,那么1秒就能产生100次脉冲,那么主频就是100赫兹)

T与f的关系:根据上述描述,设一次脉冲花费0.01秒,那么T就是0.01s,主频就是100赫兹。所以f=1/T。

指令:当指令执行的时候都要花费这些脉冲,为了讨论指令和脉冲的关系引入以下定义。

CPI:每条指令的时钟周期数。根据英文来记:CPI=Cycle per instruction。(也就是一条指令花费的脉冲数)CPI=时钟周期数/一条指令。(3.3有解释)

IPS:每秒执行的指令数。根据英文来记:IPS=Instruction per second。IPS=f/CPI。(3.3有解释)

CPU的执行时间:时钟周期数×时钟周期,因为CPI=时钟周期数/一条指令,所以CPU的执行时间=CPI×所有指令数×时钟周期。

MFLOPS:每秒执行了几百万次浮点运算。

3.3 深入理解

假设总共有5条指令,每一条指令会花费2个脉冲,也就是2个时钟周期数,也就是CPI=2。

再假设时钟周期T为0.01秒,也就是一个脉冲所花费的时间为0.01秒。

那么一条指令的CPU的执行时间就是2×0.01=0.02秒。

总共5条指令,所以CPU的执行时间就是0.02×5=0.1秒。

总结:2*0.01*5=CPI*时钟周期*指令数

再看IPS(每秒执行的指令数),因为一条指令会花费2个脉冲,一个脉冲所用的时间为0.01秒,所以完成一条指令用0.02秒。那么1秒就能完成1/0.02=50条指令,所以IPS=50

总结:IPS=1/(0.01*2)。也就是1/(时钟周期*CPI),因为主频f=1/时钟周期,所以IPS=f/CPI。

四、例题

1.关于CPU主频,CPI,MIPS,MFLOPS,下列说法正确的是

A.CPU主频是指CPU系统执行指令的频率,CPI是执行一条指令平均使用的频率

B.CPI是执行一条指令平均使用CPU时钟的个数,MIPS描述一条CPU指令平均使用的CPU时钟数

C.MIPS是描述CPU执行指令的频率,MFLOPS是计算机系统的浮点数指令

D.CPU主频指CPU使用的时钟脉冲频率,CPI是执行一条指令平均使用的CPU时钟数

答案:D

解析:A.CPU主频指CPU使用的时钟脉冲频率。是由CPU上的晶振产生的。CPI通过英文可知是每条指令的时钟周期数,也就是每条指令使用的脉冲数。而频率指的是1s内有多少个时钟周期,也就是每秒产生的脉冲数。所以A的两句话都不对。

B.CPI通过英文可知是每条指令的时钟周期数,也就是每条指令使用的脉冲数,也是时钟的个数。前半句话正确。MIPS:指每秒执行了几百万条指令。我们知道IPS(Instruction per second)是每秒执行的指令数,那么MIPS就是 Million Instruction per second。而CPU时钟数是时钟周期(一个脉冲花费的时间)。所以后半句错误。

C.MIPS:指每秒执行了几百万条指令,也就是CPU执行指令的频率,前半句话正确。后半句MFLOPS是计算机系统的浮点数指令。指令肯定不对,这是性能指标。

2.存储字长是指:

A.存放在一个存储单元中的二进制代码组合

B.存放在一个存储单元中的二进制代码位数

C.存储单元个数

D.机器指令位数

答案:B

解析:A.存放在一个存储单元中的二进制代码组合是存储字。

C.存储单元个数:存储地址能反映存储单元个数

D.机器指令位数:指令字长

3.在计算机M1和M2上分别运行功能完全相同的高级语言程序,且平均CPI相等,则

A.M1和M2执行速度相同

B.M1和M2中主频高的执行速度快

C.M1和M2中主频高的执行速度慢

D.无法确定谁速度快

答案:D

解析:计算机M1和M2上分别运行功能完全相同的高级语言程序。计算机通过编译产生指令,即使高级语言程序的功能相同,出现的指令数也可能不同。因为CPU执行速度=CPI*时钟周期*指令数,通过主频可以控制时钟周期,但指令数无法控制。所以无法确定。

4.假设A的主频为800MHZ,指令P在A上运行了12秒,现设计B,希望P在B上运行时间为8秒,但B所需的时钟周期数为A的1.5倍,则B的主频至少为()

A.800MHZ B.1.2GHZ C.1.5GHZ D.1.8GHZ

答案:D

解析:假设A的时钟周期数为x,则B的时钟周期数为1.5x.设B的主频为y

CPU的执行时间=时钟周期数*时钟周期;时钟周期=1/主频;

所以A:12秒=x*1/800MHZ; B:8秒=1.5x/y

A/B,得出y=1800MHZ=1.8GHZ

5.设编译器对高级语言的某条语句编译生成两种不同的指令序列,A,B,C三类指令的CPI和两种序列所含的三类指令条数如下,两条指令序列都在时钟周期为2ns的机器上运行,下列说法正确的是

| 指令类型 | CPI | 序列一指令条数 | 序列二指令条数 |

| A | 1 | 1 | 2 |

| B | 2 | 1 | 1 |

| C | 3 | 4 | 2 |

A.序列一的MIPS数比序列二多50,序列一的执行速度比序列二快10ns

B.序列一的MIPS数比序列二多50,序列二的执行速度比序列一快10ns

C.序列二的MIPS数比序列一多50,序列一的执行速度比序列二快10ns

D.序列二的MIPS数比序列一多50,序列二的执行速度比序列一快10ns

答案:D

解析:分析题目,生成了两种指令序列,所以指令序列为2。然后又把这两条指令序列分别分成ABC三类指令。

指令序列一:

| A CPI:1 指令条数:1 | B CPI:2 指令条数:1 | C CPI:3 指令条数:4 |

CPI:每条指令的时钟周期数。所以指令序列一中A段的时钟周期数:1*1=1;指令序列一中B段的时钟周期数:2*1=2;指令序列一中C段的时钟周期数:3*4=12.所以指令序列一的时钟周期数为1+2+12=15.

同理,指令序列二的时钟周期数:1*2+2*1+3*2=10.

时钟周期都是2ns,所以指令序列一的执行速度=时钟周期数*时钟周期=15*2=30ns;指令序列二的执行速度=时钟周期数*时钟周期=10*2=20ns.所以序列二的执行速度比序列一快10ns。排除AC。

MIPS:每秒执行几百万条指令。指令序列一:30ns执行了6条指令=5ns执行1条指令。指令序列二:20ns执行了5条指令=4ns执行1条指令。一秒=10^9ns,所以一秒中,序列一执行了10^9/5条指令,序列二执行了10^9/4条指令.所以序列二比序列一的IPS数多:10^9/4-10^9/5=50*10^6.所以MIPS=50

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?