一.什么是总线?

总线(Bus)是计算机系统中用于在不同组件之间传输数据、地址和控制信号的公共通信通道。它是计算机硬件架构中的关键组成部分,负责连接中央处理器(CPU)、内存、输入/输出设备(I/O设备)以及其他外围设备,使它们能够协同工作。

总线传输的特点:总线传输的特点涵盖了共享性、分时性、传输方式、带宽、协议、控制信号、仲裁机制、扩展性、可靠性、传输距离、功耗和成本等方面。 共享性:总线是多个设备共享的公共通信通道。所有连接到总线的设备都可以通过总线进行数据传输,但同一时刻只能有一个设备占用总线。共享性要求总线必须有一套仲裁机制,以避免多个设备同时访问总线导致的冲突。 分时性:由于总线是共享资源,设备对总线的使用是分时进行的。即在同一时刻,只有一对设备(发送方和接收方)可以占用总线进行通信。分时性通过总线控制器或仲裁器来管理,确保设备有序地访问总线。传输方式:并行传输:同时传输多个比特(bit),速度快,但需要较多的物理线路,适合短距离传输。串行传输:逐比特传输数据,线路较少,适合长距离传输,但速度相对较慢。带宽和速度:总线的带宽决定了单位时间内可以传输的数据量,通常以比特/秒(bps)或字节/秒(Bps)为单位。总线的速度取决于时钟频率和传输协议,时钟频率越高,传输速度越快。

为了减轻总线的负载,连接到总线的部件应具备:高集成度(部件应尽可能集成更多的功能,减少对外部总线的依赖)、本地缓存(用于存储常用数据或指令,减少对总线的频繁访问)、智能控制、数据压缩、分时访问、低功耗设计、高速接口、数据预处理、错误检测与纠正、模块化设计、高效协议、负载均衡、异步通信和缓冲机制等特点。这些特点可以显著提高总线传输效率,降低总线负载,从而提升整个系统的性能。

二.总线如何分类?

1. 按功能分类

数据总线(Data Bus):

用于在组件之间传输数据。数据总线的宽度(位数)决定了每次可以传输的数据量。

功能:传输实际数据(如指令、运算结果、I/O数据)。

方向:双向(CPU可向内存/外设写数据,也可读取数据)。

位宽:决定单次传输的数据量(如64位总线一次传输8字节)。

带宽:由位宽和频率共同决定,公式:带宽=位宽×频率÷8

技术特点:现代多采用串行传输(如PCIe、USB),通过差分信号抗干扰。并行总线(如传统PCI)因信号同步问题逐渐被淘汰。支持突发传输模式(Burst Mode)提高连续数据吞吐量。

应用场景:内存读写、外设数据传输(如硬盘、显卡)。

地址总线(Address Bus):

功能:指定数据操作的目标位置(内存地址或I/O端口号)。

方向:单向(仅由CPU或DMA控制器发出地址)。

位宽:决定最大寻址空间(32位总线支持4GB,64位支持16EB)。

技术特点:通过地址复用技术(如分时复用)减少物理引脚数量。虚拟地址扩展(如PAE技术)突破物理位宽限制。需严格时序控制,确保地址信号在时钟周期内稳定。

关键作用:实现内存管理、外设寻址和虚拟内存映射。

控制总线(Control Bus):

功能:传输协调系统操作的控制信号。

-

信号类型:

-

读写控制:如

MEMR#(内存读)、IOW#(I/O写)。 -

中断管理:

IRQ(中断请求)、INTA#(中断响应)。 -

同步与时序:时钟信号(

CLK)、就绪信号(READY)。 -

总线仲裁:

BREQ(总线请求)、BGNT#(总线授权)。 -

方向:双向或混合(不同信号方向不同)。

-

-

技术特点:采用同步/异步协议协调时序(如PCIe为同步,USB为异步)。支持错误检测机制(如奇偶校验、CRC)。多设备共享时需仲裁逻辑(如轮询、优先级抢占)。

| 特性 | 数据总线 | 地址总线 | 控制总线 |

|---|---|---|---|

| 核心功能 | 传输数据 | 指定地址 | 协调操作 |

| 传输方向 | 双向 | 单向(CPU→外设/内存) | 双向(信号类型决定方向) |

| 位宽影响 | 决定单次数据量 | 决定寻址空间 | 决定控制信号种类 |

| 关键技术 | 串行差分信号、突发传输 | 地址复用、虚拟内存 | 同步协议、仲裁机制 |

| 性能瓶颈 | 带宽和延迟 | 寻址范围和延迟 | 仲裁效率和信号稳定性 |

| 典型示例 | PCIe x16(32GB/s) | DDR5地址线(40位物理地址) | PCIe控制信号(TS1/TS2) |

总结

数据总线是系统的“血液”,决定吞吐量。

地址总线是“导航”,确保数据精准定位。

控制总线是“神经”,协调全局操作。

三者协同工作,通过优化带宽、降低延迟和提高可靠性,共同支撑计算机系统的高效运行。

2. 按位置分类

内部总线(Internal Bus):

位于CPU内部,用于连接CPU的各个部件(如寄存器、算术逻辑单元等)。

外部总线(External Bus):

用于连接计算机与外部设备(如USB、PCI等)。

♥系统总线(System Bus):

连接CPU、内存和其他主要组件,是计算机系统的核心总线。

系统总线通常分为以下三类:

-

数据总线(Data Bus):

-

作用:用于在CPU、内存和I/O设备之间传输数据。

-

方向:双向(数据可以从CPU传输到内存或I/O设备,也可以从内存或I/O设备传输到CPU)。

-

宽度:数据总线的宽度通常与机器的字长(Word Length)一致,决定了每次可以传输的数据量。

-

-

地址总线(Address Bus):

-

作用:用于传输内存或I/O设备的地址信息,指定CPU要访问的具体位置。

-

方向:单向(地址信息只能从CPU传输到内存或I/O设备)。

-

宽度:地址总线的宽度决定了系统可以寻址的内存空间大小。例如,32位地址总线可以寻址2^32(4GB)的内存空间。

-

-

控制总线(Control Bus):

-

作用:用于传输控制信号,如读写信号、中断信号、时钟信号等,以协调CPU、内存和I/O设备之间的操作。

-

方向:双向(控制信号可以从CPU传输到其他设备,也可以从其他设备传输到CPU)。

-

信号类型:控制总线通常包括读写信号、中断请求信号、总线请求信号、总线允许信号等。

-

系统总线与机器字长、存储字长、存储单元的关系:机器字长决定了数据总线的传输效率。存储字长决定了内存与CPU之间的数据传输效率。地址总线的宽度决定了系统可以寻址的存储单元数量。

3. 按传输方式分类

♥并行总线:

同时传输多个比特(bit),速度快,但需要较多的物理线路,适合短距离传输。例如,早期的PCI总线。

♥串行总线:

逐比特传输数据,线路较少,适合长距离传输,但速度相对较慢。例如,USB、SATA、PCIe总线。

| 对比项 | 串行总线 | 并行总线 |

|---|---|---|

| 线路数量 | 较少(通常1-4条),逐位传输。 | 较多(通常8、16、32或64条),同时传输多位。 |

| 物理距离 | 适合长距离传输,信号衰减少。 | 适合短距离传输,长距离易失真。 |

| 传输速度 | 单条线路速度高,整体速度可能较慢。 | 多条线路同时传输,整体速度快。 |

| 时钟频率 | 高(通常GHz级)。 | 低(通常MHz级)。 |

| 信号干扰 | 抗干扰能力强,采用差分信号技术。 | 易受干扰,尤其长距离传输。 |

| 信号同步 | 无需严格时钟同步,采用嵌入式时钟技术。 | 需要严格时钟同步,时钟偏移易导致错误。 |

| 成本 | 线路少,连接器简单,成本低。 | 线路多,连接器复杂,成本高。 |

| 扩展性 | 易于扩展,支持热插拔和多设备连接。 | 扩展性差,增加线路提高复杂性。 |

| 典型应用 | 长距离通信、高速数据传输、现代外设连接(如USB、SATA、PCIe、以太网、HDMI)。 | 短距离高速数据传输、传统内部连接(如IDE、SCSI、PCI、DDR内存总线)。 |

| 优点 | 成本低,抗干扰强,适合长距离,易于扩展。 | 传输速度快,适合短距离高速传输。 |

| 缺点 | 单条线路速度有限,整体速度可能较慢。 | 成本高,易受干扰和时钟偏移影响,扩展性差。 |

4. 按用途分类

处理器总线(Processor Bus):用于连接CPU与内存控制器或缓存,通常是高速总线。

存储总线(Memory Bus):用于连接CPU与内存,负责传输数据和控制信号。

I/O总线(I/O Bus):用于连接CPU与I/O设备,例如PCI、USB、SATA等。

5. 按层次结构分类

前端总线(Front Side Bus, FSB)**:用于连接CPU与北桥芯片(或内存控制器),是传统计算机系统中的核心总线。

后端总线(Back Side Bus, BSB)**:用于连接CPU与二级缓存(L2 Cache),通常是高速总线。

6. 按传输方向分类

单向总线:数据只能在一个方向上传输。例如,地址总线通常是单向的,从CPU向内存或I/O设备传输地址信息。

双向总线:数据可以在两个方向上传输。例如,数据总线通常是双向的,允许CPU与内存或I/O设备之间双向传输数据。

7.按标准化程度分类

标准总线:遵循公开的标准协议,具有广泛的兼容性。例如,PCI、USB、SATA等。

专用总线:为特定设备或应用设计,不具有通用性。例如,某些嵌入式系统中的定制总线。

8. 按传输速率分类

低速总线:传输速率较低,通常用于连接低速设备。例如,I2C、SPI总线。

中速总线:传输速率适中,通常用于连接存储设备或外围设备。例如,SATA、USB 2.0总线。

高速总线:传输速率较高,通常用于连接高性能设备。例如,PCIe、USB 3.0总线。

9. 按拓扑结构分类

点对点总线:仅连接两个设备,传输效率高。例如,PCIe总线。

多点总线:连接多个设备,设备共享总线资源。例如,I2C、SPI总线。

10. 按应用领域分类

计算机总线:用于计算机系统内部或与外部设备的连接。例如,PCI、USB、SATA等。

工业总线:用于工业控制系统中的设备连接。例如,CAN总线、Profibus。

嵌入式总线:用于嵌入式系统中的设备连接。例如,I2C、SPI总线。

三.常见的总线结构

| 结构 | 特点 | 对性能的影响 | 举例 |

|---|---|---|---|

| 单总线结构 | 所有设备共享一条总线,结构简单,成本低。 | 容易成为性能瓶颈,适合小型系统。 | 早期PC系统。 |

| 双总线结构 | 分为CPU-内存总线和I/O总线,减少总线竞争。 | 提高数据传输效率,适合中等规模系统。 | 传统PC的北桥和南桥架构。 |

| 多总线结构 | 多条总线连接特定设备,减少竞争,提高并行性。 | 显著提高系统性能,适合高性能计算和大型系统。 | 现代服务器和工作站。 |

| 分层总线结构 | 高层总线连接高速设备,低层总线连接低速设备,优化资源分配。 | 提高系统效率,适合复杂系统。 | 现代计算机系统中CPU、内存和I/O设备的分层连接。 |

| 点对点总线结构 | 每个设备通过独立通道直接连接,无总线竞争,扩展性强。 | 显著提高性能,适合高性能计算和并行处理。 | 现代CPU与内存之间的DDR通道,以及PCIe总线。 |

1. 单总线结构(Single Bus Structure)

- 描述:所有设备(CPU、内存、I/O设备)共享同一条总线。

- 特点:

- 结构简单,成本低。

- 所有设备共享总线带宽,容易成为性能瓶颈。

- 设备数量增加时,总线竞争加剧,性能下降。

- 对性能的影响:

- 适合小型系统,但在高性能系统中容易成为瓶颈。

- 例如,早期的PC系统采用单总线结构,随着设备增加,性能受限。

2. 双总线结构(Dual Bus Structure)

- 描述:将系统分为两条总线,一条用于CPU与内存之间的高速通信,另一条用于I/O设备。

- 特点:

- 减少CPU与内存之间的总线竞争,提高数据传输效率。

- I/O设备通过独立的I/O总线连接,减轻系统总线负载。

- 对性能的影响:

- 提高了系统的整体性能,适合中等规模的系统。

- 例如,传统PC系统中的北桥和南桥架构采用双总线结构,北桥连接CPU和内存,南桥连接I/O设备。

3. 多总线结构(Multi-Bus Structure)

- 描述:系统中包含多条总线,每条总线连接特定的设备或功能模块。

- 特点:

- 进一步减少总线竞争,提高并行性。

- 支持更多设备,扩展性强。

- 结构复杂,成本较高。

- 对性能的影响:

- 显著提高系统性能,适合高性能计算和大型系统。

- 例如,现代服务器和工作站采用多总线结构,将CPU、内存、存储和网络设备分别连接到不同的总线。

4. 分层总线结构(Hierarchical Bus Structure)

- 描述:将总线分为多个层次,每层总线连接特定类型的设备。

- 特点:

- 高层总线连接高速设备(如CPU、内存),低层总线连接低速设备(如I/O设备)。

- 减少高速总线的负载,提高系统效率。

- 对性能的影响:

- 优化了总线资源分配,提高了系统的整体性能。

- 例如,现代计算机系统中,CPU与内存通过高速总线连接,而I/O设备通过PCIe等低速总线连接。

5. 点对点总线结构(Point-to-Point Bus Structure)

- 描述:每个设备通过独立的通道直接连接到CPU或其他设备。

- 特点:

- 无总线竞争,数据传输效率高。

- 扩展性强,但成本较高。

- 对性能的影响:

- 显著提高系统性能,适合高性能计算和并行处理。

- 例如,现代CPU与内存之间采用点对点连接(如DDR内存通道),以及PCIe总线采用点对点连接。

四.总线的连接方式

| 连接方式 | 描述 | 特点 | 应用场景 |

|---|---|---|---|

| 点对点连接 | 每个设备通过独立通道直接连接。 | 无竞争,效率高;成本高。 | 高性能计算、PCIe总线。 |

| 共享总线连接 | 多个设备共享同一条总线。 | 简单,成本低;竞争加剧性能下降。 | 小型系统、I2C总线。 |

| 星型连接 | 所有设备通过独立线路连接到中心节点。 | 中心节点是瓶颈;易于扩展。 | 网络设备、USB集线器。 |

| 环形连接 | 设备通过环形拓扑连接,数据依次传递。 | 延迟较高;适合分布式系统。 | Token Ring网络。 |

| 树型连接 | 设备通过分层树状拓扑连接。 | 易于扩展;上层节点是瓶颈。 | 大型网络、路由器拓扑。 |

| 网状连接 | 设备通过网状拓扑连接,路径多。 | 可靠性高;结构复杂,成本高。 | 超级计算机、通信网络。 |

| 混合连接 | 结合多种连接方式。 | 兼顾性能和成本;设计复杂。 | 现代PC系统。 |

五.总线标准

总线标准是计算机系统中用于规范各组件间通信接口的统一协议,涵盖机械结构(如接口形状、引脚排列)、电气特性(如电压、信号时序)和功能逻辑(如数据传输协议)。总线标准确保不同厂商生产的硬件设备能够无缝协同工作,简化系统设计并提升兼容性。

为什么要设置总线标准?

- 兼容性:统一接口规范使不同厂商的设备能够互联互通(如USB设备可在任意电脑上使用)。

- 扩展性:标准化的总线支持灵活添加新硬件(如通过PCIe插槽安装显卡)。

- 简化开发:厂商无需为每款设备定制接口,降低研发成本(如遵循SATA标准的硬盘可直接用于主板)。

- 性能优化:通过协议升级(如USB 3.0→USB4)提升传输速度与效率。

目前流行的总线标准及特点

| 总线标准 | 类型 | 带宽/速度 | 典型应用 | 特点 |

|---|---|---|---|---|

| USB | 外部串行总线 | USB 3.2 Gen 2x2: 20Gbps | 外置存储、键盘、鼠标 | 支持热插拔、即插即用,向下兼容性强 |

| PCIe | 内部串行总线 | PCIe 5.0 x16: 64GB/s | 显卡、NVMe SSD、高速网卡 | 多通道聚合、低延迟,支持热插拔 |

| Thunderbolt | 外部串行总线 | Thunderbolt 4: 40Gbps | 显示器、外置显卡坞、高速存储 | 整合PCIe与DisplayPort,支持菊花链拓扑 |

| SATA | 内部串行总线 | SATA III: 6Gbps | 机械硬盘、SSD | 低成本、高兼容性,逐步被NVMe取代 |

| I2C | 板级串行总线 | 标准模式: 100kbps | 传感器、EEPROM | 简单双线制(SDA、SCL),支持多主从设备 |

| CAN | 工业串行总线 | 1Mbps(短距离) | 汽车电子、工业控制 | 抗干扰性强,支持多节点广播通信 |

| Ethernet | 网络总线 | 100Gbps(高速以太网) | 局域网、数据中心 | 长距离传输,支持TCP/IP协议栈 |

什么是即插即用(Plug-and-Play, PnP)?

即插即用是指设备插入系统后,无需手动配置硬件资源(如中断请求IRQ、I/O地址),操作系统自动识别设备并加载驱动程序的功能。其实现依赖于:

- 硬件标识:设备内置描述符(如USB设备的VID/PID)供系统识别。

- 资源分配:操作系统动态分配内存地址、中断等资源。

- 驱动管理:操作系统内置通用驱动或自动下载匹配驱动。

支持即插即用的总线标准

- USB:插入设备后自动识别并分配资源(如U盘即插即用)。

- PCIe:支持热插拔,操作系统动态配置设备(如外置显卡坞)。

- Thunderbolt:通过PCIe协议实现即插即用(如外置显示器即插即显)。

- SATA:部分支持热插拔(需操作系统配合,如外置硬盘盒)。

- PCMCIA/ExpressCard:旧式笔记本扩展卡,支持热插拔。

对比非即插即用总线(如传统ISA总线)

| 特性 | 即插即用总线(如USB) | 非即插即用总线(如ISA) |

|---|---|---|

| 资源分配 | 自动分配IRQ、I/O地址 | 需手动设置跳线或DIP开关 |

| 热插拔 | 支持(如USB设备随时插拔) | 不支持,需关机操作 |

| 驱动安装 | 自动识别并加载驱动 | 需用户手动安装驱动 |

| 典型应用 | 现代外设(打印机、移动硬盘) | 早期声卡、网卡 |

六.总线的数据传送速率

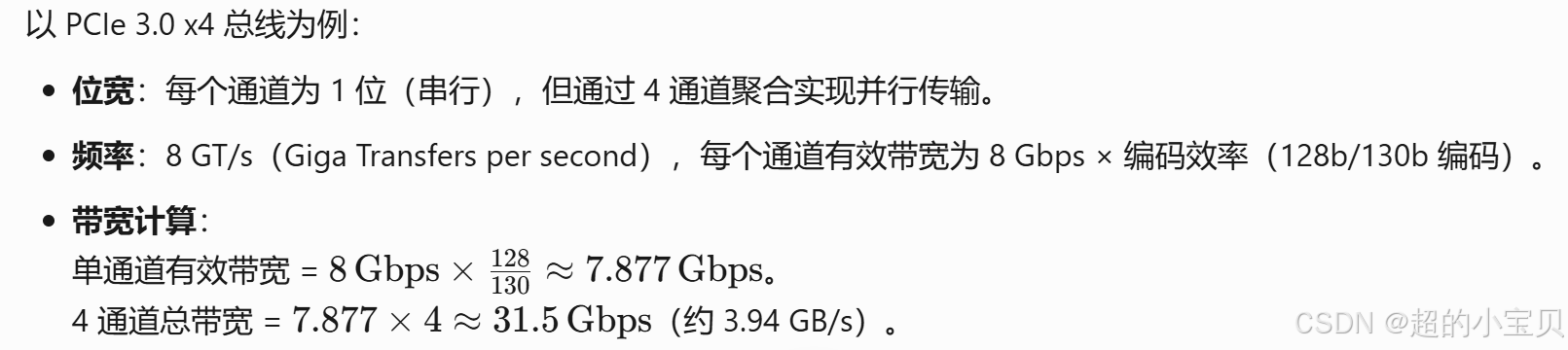

总线的数据传送速率(通常称为 总线带宽)是指总线在单位时间内能够传输的最大数据量,通常以 比特每秒(bps) 或 字节每秒(B/s) 表示。例如,PCIe 4.0 x16 总线的理论带宽可达 32 GB/s。这一速率决定了系统内部或外设之间数据传输的效率。

总线的数据传送速率由 位宽、频率、协议效率 和 物理设计 共同决定。现代技术通过串行高频传输、多通道聚合和智能协议优化,显著提升了总线带宽(如 PCIe 6.0 达 64 GT/s)。实际应用中需权衡速度、成本和兼容性,例如 USB 4 兼顾 40Gbps 速率与即插即用特性,而 DDR5 内存通过高频率和双通道设计满足高性能计算需求。

影响总线数据传送速率的核心因素

-

总线位宽(数据位数)

- 定义:总线一次能传输的二进制位数(如 32 位、64 位)。

- 影响:位宽越大,单次传输的数据量越多。例如,64 位总线比 32 位总线单次传输数据量翻倍。

- 公式:位宽直接影响理论带宽(带宽 = 位宽 × 频率 × 传输效率)。

-

总线时钟频率

- 定义:总线每秒完成的时钟周期数,单位为 MHz 或 GHz。

- 影响:频率越高,单位时间内的数据传输次数越多。例如,DDR5 内存的 4800 MHz 频率显著高于 DDR4 的 3200 MHz。

- 限制:高频可能导致信号完整性问题(如串扰、衰减),需通过差分信号或编码技术缓解。

-

传输协议与编码方式

- 协议效率:部分协议需要额外的控制位或校验位(如 USB 的 8b/10b 编码),导致实际有效带宽降低。

- 同步机制:同步总线(如 PCIe)依赖统一时钟,异步总线(如 USB)通过握手信号协调时序,影响传输效率。

-

总线类型(并行/串行)

- 并行总线:通过多条线路同时传输数据(如传统 PCI 总线),但受限于时钟偏移和信号干扰,难以提升高频性能。

- 串行总线:单线路逐位传输(如 PCIe、USB),通过提高频率和差分信号技术实现高速长距离传输。

-

传输模式与拓扑结构

- 全双工/半双工:全双工总线(如 PCIe)支持同时收发数据,带宽利用率更高;半双工总线(如 I2C)需分时复用线路。

- 多通道聚合:如 PCIe 支持多通道(x1、x4、x16)聚合,带宽成倍增加。

-

物理层限制

- 信号衰减与干扰:长距离传输时,信号衰减和电磁干扰可能导致误码率上升,需降低频率或增强抗干扰设计(如 LVDS 差分信号)。

- 连接器与线材质量:低质量线材或连接器会增加阻抗不匹配,影响高频信号稳定性。

-

系统负载与仲裁机制

- 总线竞争:多设备共享总线时,仲裁机制(如轮询、优先级)决定访问顺序,可能引入延迟。

- 设备兼容性:不同设备的驱动能力或协议支持差异可能导致带宽受限。

技术趋势与优化手段

- 高频化与串行化:现代总线(如 PCIe 5.0、USB4)通过提升频率(32 GT/s)和串行设计突破传统并行总线瓶颈。

- 多通道与分层协议:PCIe 的虚拟通道(Virtual Channels)支持优先级传输,优化实时数据流。

- 抗干扰技术:使用差分信号(如 PCIe 的 LVDS)和纠错编码(如 Ethernet 的 FEC)提升可靠性。

七.总线通信

同步通信(Synchronous Communication)

基本原理 :依赖统一时钟:所有设备共享同一个时钟信号,数据传输的时序由时钟边沿(上升沿或下降沿)严格同步。 固定时序:发送方和接收方在每个时钟周期内完成数据采样或发送,传输速率由时钟频率决定。

典型应用:内存总线(如DDR SDRAM)、高速芯片间通信(如PCIe同步模式)。

关键特点: 高效率:无额外控制信号开销,适合高速、连续数据传输。 时序约束严格:对时钟信号的稳定性要求极高,需避免时钟偏移(Clock Skew)。

异步通信(Asynchronous Communication)

基本原理: 无共享时钟:设备间通过起始位/停止位或握手协议协调数据传输。 自同步机制:接收方根据数据信号的变化(如起始位触发)自主采样数据。

典型应用:UART串口、USB(基于握手协议)、网络通信(如以太网)。

关键特点: 灵活性高:适应不同时钟频率的设备间通信。 额外开销:数据帧需包含起始位、校验位和停止位(如UART的1起始位+8数据位+1停止位)。

| 特性 | 同步通信 | 异步通信 |

| 时钟依赖 | 必须共享统一时钟信号 | 无共享时钟,通过起始位或握手信号同步 |

| 传输效率 | 高(无额外控制位,连续传输) | 较低(需起始/停止位或握手协议) |

| 时序要求 | 严格(时钟偏移需小于一个周期) | 宽松(允许时钟频率差异,但波特率需匹配) |

| 适用场景 | 高速、短距离、设备时钟同步(如CPU-内存、SPI) | 长距离、设备时钟不同步(如串口、USB、网络) |

| 抗干扰能力 | 依赖时钟信号稳定性,高频易受干扰 | 通过校验位(如奇偶校验)增强可靠性 |

| 典型协议 | DDR、SPI、PCIe(同步模式) | UART、USB、I2C(部分模式) |

总结

同步通信以高效率和低延迟为核心,适合短距离高速场景,但依赖精密时钟设计。

异步通信以灵活性和适应性见长,适合异构设备间通信,但需容忍协议开销。

两者共同支撑了计算机系统从芯片级到跨设备的数据交互需求。

♥♥♥题目测试

一、选择题

1. **总线连接中,多个设备共享一条通信线路,这条线路称为( )

A. 分散连接线

B. 总线

C. 串行线

D. 并行线

**答案** :B

**解析** :总线连接的定义是多个设备共享一条通信线路,即总线,用于设备间的信息交换。

2. **在( )传输方式中,数据以位为单位依次在一条线路上进行传输。

A. 并行传输

B. 串行传输

C. 分散传输

D. 总线传输

**答案** :B

**解析** :串行传输的定义是数据以位为单位依次在一条线路上进行传输,与并行传输相对。

3. 单总线结构中,系统内所有设备都连接在( )上。

A. 多条总线

B. 两条总线

C. 一条总线

D. 无总线

答案:C

解析:单总线结构的定义是系统中只有一条总线,所有设备都连接在这条总线上进行通信和数据交换。

4.分散连接和总线连接相比,以下说法正确的是:

A. 分散连接线路数量少,扩展性好

B. 总线连接线路数量多,通信效率高

C. 分散连接通信效率高,扩展性差

D. 总线连接通信效率高,扩展性差

答案:C

解析:分散连接中每个设备通过独立的线路连接,通信效率高,但线路数量多,扩展性差;总线连接中多个设备共享一条总线,扩展性好,但通信效率可能受总线竞争影响。

5. 串行传输和并行传输相比,以下说法正确的是

A. 串行传输适合长距离,成本高

B. 并行传输适合短距离,成本低

C. 串行传输适合长距离,成本低

D. 并行传输传输速度慢,受干扰影响小

答案:C

解析:串行传输适合长距离传输,成本低;并行传输适合短距离传输,成本高,且容易受到信号干扰。

6. 单总线结构的计算机系统中,以下说法正确的是:

A. 结构复杂,扩展性差

B. 总线带宽充足,无性能瓶颈

C. 多个主设备同时访问时会产生冲突

D. 适合高性能计算场景

答案:C

解析:单总线结构中,多个主设备同时访问总线时会产生冲突,形成性能瓶颈。

7. 以CPU/存储器为中心的双总线结构,以下说法正确的是:

A. 结构简单,成本低

B. 数据传输效率低

C. 减少了设备间通信的冲突

D. 扩展性差,难以添加新设备

答案:C

解析:双总线结构通过分离CPU/存储器总线和I/O总线,减少了设备间通信的冲突,提高了数据传输效率。

8. 以下关于总线连接的描述,正确的是:

A. 所有设备共享一条通信总线,易于扩展新设备

B. 设备之间通过点对点方式直接相连,通信效率高

C. 适合设备数量较少的系统,线路数量随设备数量线性增长

D. 总线带宽无限,多个设备可同时通信无冲突

答案:A

解析:总线连接中,所有设备共享一条通信总线,易于扩展新设备,但总线带宽有限,多个设备同时通信时会产生冲突。

9. 串行传输的主要优点是:

A. 传输速度快,适合短距离传输

B. 成本低,适合长距离传输

C. 不受信道带宽和干扰限制

D. 数据一位一位依次传输,复杂度高

答案:B

解析:串行传输成本低,适合长距离传输,且抗干扰能力强。

10. 并行传输的主要缺点是:

A. 成本高,需要多对传输线

B. 传输速度慢,适合长距离传输

C. 不适合用于计算机内部CPU与内存之间

D. 扩展性好,易于添加新设备

答案:A

解析:并行传输需要多对传输线,成本高,且容易受到信号干扰和时钟偏移影响。

11. 单总线结构的缺点是:

A. 结构过于复杂,难以实现

B. 总线带宽无限,性能优异

C. 多个主设备同时访问时会产生冲突,形成性能瓶颈

D. 不适合连接多种不同类型的设备

答案:C

解析:单总线结构中,多个主设备同时访问总线时会产生冲突,形成性能瓶颈。

12. 以CPU/存储器为中心的双总线结构,其优势体现在:

A. 极大降低了设备间通信的冲突,提高了数据传输效率

B. 结构简单,成本远低于单总线结构

C. 扩展性极差,难以适应系统升级需求

D. 总线带宽受限,影响整体性能发挥

答案:A

解析:双总线结构通过分离CPU/存储器总线和I/O总线,降低了设备间通信的冲突,提高了数据传输效率。

13. 在计算机网络中,选择分散连接还是总线连接,主要考虑因素包括:

A. 设备数量、通信频率、成本和扩展性等多方面因素

B. 仅根据设备的物理位置决定

C. 不需考虑成本因素,只关注通信效率

D. 完全取决于网络的拓扑结构,与其他无关

答案:A

解析:选择分散连接或总线连接时,需要综合考虑设备数量、通信频率、成本和扩展性等多方面因素。

14.同步通信的核心特点是:

A. 设备间通过起始位同步

B. 依赖共享时钟信号

C. 允许设备间时钟频率差异

D. 通过握手协议保证可靠性

答案:B

解析:同步通信的核心是依赖共享时钟信号(如SPI的SCLK),所有设备基于同一时钟进行数据采样,故B正确。A是异步通信的特征(如UART起始位),C是异步的优势,D是异步握手协议的特点。

15.以下哪种总线协议属于异步通信:

A. SPI

B. DDR SDRAM

C. UART

D. PCIe(同步模式)

答案:C

解析:UART是典型的异步通信协议(无共享时钟,靠起始位同步),而SPI、DDR SDRAM和PCIe(同步模式)均依赖时钟信号,属于同步通信,故C正确。

16.异步通信中,UART帧格式通常包含:

A. 起始位 + 数据位 + 校验位 + 停止位

B. 同步头 + 数据包 + CRC校验

C. 时钟信号 + 数据信号

D. 地址位 + 控制位 + 数据位

答案:A

解析:UART帧格式为起始位(1位)+ 数据位(5-8位)+ 可选的校验位(1位)+ 停止位(1-2位),故A正确。B是同步协议的帧结构(如SPI的同步头),C是同步通信的物理信号,D是总线地址寻址格式。

17.同步通信的主要缺点是:

A. 传输效率低

B. 需要额外握手协议

C. 对时钟信号稳定性要求极高

D. 无法支持高速传输

答案:C

解析:同步通信要求所有设备严格同步于同一时钟,时钟偏移(Skew)或抖动可能导致数据错误,因此对时钟稳定性要求极高,故C正确。D错误,同步通信反而支持高速传输(如DDR内存)。

二、填空题

1. 在计算机网络中,设备间通过点对点方式连接称为(分散连接),其优点是(连接稳定,通信效率高),缺点是(连接数量随设备增加呈指数增长,布线复杂,系统扩展困难)。

2. 总线连接的优点是(连接简单,易于扩展),缺点是(总线带宽有限,易产生冲突,传输效率可能下降)。

3. 串行传输适合(远距离)传输,成本(低),但速度相对较(慢);并行传输适合(短距离)传输,速度(快),但成本较(高)。

4. 以CPU/存储器为中心的双总线结构中,一条总线用于(CPU与存储器之间的通信),另一条用于(CPU与I/O设备之间的通信)。

三、判断题

1. **总线连接中,设备数量增加会导致布线复杂度显著增加。**(×)

**解析** :总线连接布线相对简单,设备增加只是接入总线,不会导致布线复杂度显著增加,与分散连接不同。

2. **并行传输因为使用多条线路,所以其传输速度一定比串行传输快。**(×)

**解析** :传输速度不仅取决于线路数量,还与传输距离、信号干扰等因素有关。在远距离传输时,串行传输可能更适合,其速度未必比并行传输慢。

3. **单总线结构的性能优于双总线结构。**(×)

**解析** :单总线结构性能瓶颈明显,双总线结构通过两条总线分担通信任务,性能更优,能提高数据传输效率,减少冲突。

四、辨析题

一、比较分散连接和总线连接的优缺点

**答案** :

- **分散连接** :优点是连接稳定,通信效率高,不存在共享通信线路带来的冲突问题;缺点是连接数量随设备增加呈指数增长,布线复杂,系统扩展困难。

- **总线连接** :优点是连接简单,易于扩展,新增设备只需接入总线;缺点是总线带宽有限,多个设备同时传输数据易产生冲突,导致传输效率下降。

二、请比较串行传输和并行传输的适用场景

**答案** :

- **串行传输** :适合远距离传输,因为只需要一对传输线,成本低,且在长距离传输中信号干扰相对较小,如通过电话线进行数据传输。

- **并行传输** :适合短距离、大量数据的快速传输,如计算机内部CPU与内存之间的数据交换,可快速并行传输大量数据,提高处理速度。

三、单总线结构和双总线结构在性能上有何差异?为什么?

**答案** :

- **单总线结构性能瓶颈明显** ,因为只有一条总线,当多个设备同时请求总线时易产生冲突,导致数据传输效率低下,难以满足高性能计算需求。

- **双总线结构性能更优** ,通过两条总线分担通信任务,CPU与存储器、I/O设备可同时进行数据传输,减少总线竞争,提高数据传输效率。

五、综合题

一、某计算机系统采用总线连接方式,现有设备A、B、C、D连接在总线上。某一时刻,设备A要向设备B发送数据,同时设备C要向设备D发送数据。请分析在这种情况下可能会出现什么问题?如何解决?

答案*:

- **可能出现的问题** :由于总线带宽有限,当设备A和设备C同时请求使用总线进行数据发送时,会发生总线冲突,导致数据无法同时传输,出现数据碰撞或传输错误,使有效数据无法正确到达接收方。

- **解决方法** :采用总线仲裁机制,如集中式总线仲裁中的链式查询方式、计数器定时查询方式或独立请求方式等,由总线控制器按照一定优先级规则对多个设备的总线请求进行仲裁,每次只允许一个设备获得总线控制权进行数据传输,其他设备需等待下一次总线空闲时再次请求,从而避免冲突,确保数据正确传输。

二、某计算机系统采用单总线结构,系统中有CPU、存储器和多个I/O设备。当CPU需要从某个I/O设备读取数据并存储到存储器中时,请描述这一过程涉及的总线操作步骤。

答案 :

1. **I/O设备发出中断请求** :I/O设备完成数据准备后,向CPU发出中断请求,表明有数据需要传输。

2. **CPU响应中断** :CPU暂停当前任务,保存现场,转去执行中断服务程序。

3. **CPU通过总线从I/O设备读取数据** :在中断服务程序中,CPU通过总线向I/O设备发送读取命令,I/O设备将数据放到总线上,CPU从总线上获取数据。

4. **CPU通过总线将数据写入存储器** :CPU通过总线向存储器发送写入命令和地址,将从I/O设备读取的数据写入指定存储器地址。

5. **恢复现场并继续执行原任务** :数据传输完成后,CPU恢复现场,继续执行被中断的任务。

三、某计算机系统采用以CPU/存储器为中心的双总线结构,其中CPU与主存之间通过总线A连接,CPU与I/O设备之间通过总线B连接。请分析这种结构的优点,并说明在数据从I/O设备传输到主存的过程中,总线如何协作完成数据传输。

答案 :

- **优点** :这种双总线结构提高了数据传输效率,CPU与存储器、I/O设备可同时进行数据传输,减少总线竞争;减少了冲突,两条总线分担不同设备间的通信任务,降低了冲突概率。

- **数据传输过程** :当I/O设备有数据要传输到主存时,首先I/O设备通过总线B将数据发送给CPU;CPU接收到数据后,通过总线A将数据转发到主存,完成数据传输。在此过程中,两条总线协同工作,确保数据正确传输到目标位置。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?