目录

前言

在专用集成电路( ASIC)领域中,FPGA作为一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。同时FPGA可用于实现硬件灵活定制,能够高效地实现算法加速、数据处理,从而提高系统的性能。

1、FPGA是什么?

FPGA(全称: Field Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。FPGA是一种完成通用功能的可编程逻辑芯片,即可以对其进行编程实现某种逻辑处理功能。FPGA更偏向于硬件电路,是用来设计芯片的芯片(FPGA),通过硬件编程语言在FPGA芯片上自定义集成电路的过程;单片机偏向于软件,是在已有的固化电路的芯片(单片机)上设计开发,通过软件编程语言描述软件指令在硬件芯片上的执行。

2、FPGA开发环境

2.1 语言环境

硬件描述语言主要包括:Verilog、VHDL、System Verilog。

Verilog HDL:拥有广泛的设计群体,成熟的资源也比VHDL丰富,从C编程语言中继承了多种操作符和结构,易于学习和理解。

VHDL:超高速集成电路硬件描述语言是一种标准化程度较高的硬件描述语言,其具有语法严谨、结构规范、移植性强、数据类型丰富等特点。除此之外VHDL支持层次结构设计,独立于器件和设计平台,程序复用性强。

SystemVerilog:结合了来自Verilog、VHDL、C++的概念,将硬件描述语言与现代的高层级验证语言结合了起来。所以System Verilog有上述两种语言和计算机高级语言的特征。

因此,本文采用的就是Verilog 语言对FPGA进行编程。

Verilog既是一种行为描述语言也是一种结构描述语言。这意味着,无论是描述电路功能行为的模块,还是描述元器件或较大部件互联的模块,都可以用Verilog语言来建模。

Verilog语言本身就是从C语言继承并发展而来的,但是它主要用于描述硬件,和C语言这种软件语言思想完全不同。C语言所描述的代码功能在执行时都是逐行(顺序)执行的,而Verilog语言在设计完成后执行时则是并行执行的, C语言所描述的代码功能并不会真实的映射成最后的硬件,只是对内存的操作和进行数据的搬移,而用Verlog语言所描述的代码功能则会真正的生成所对应的硬件电路。

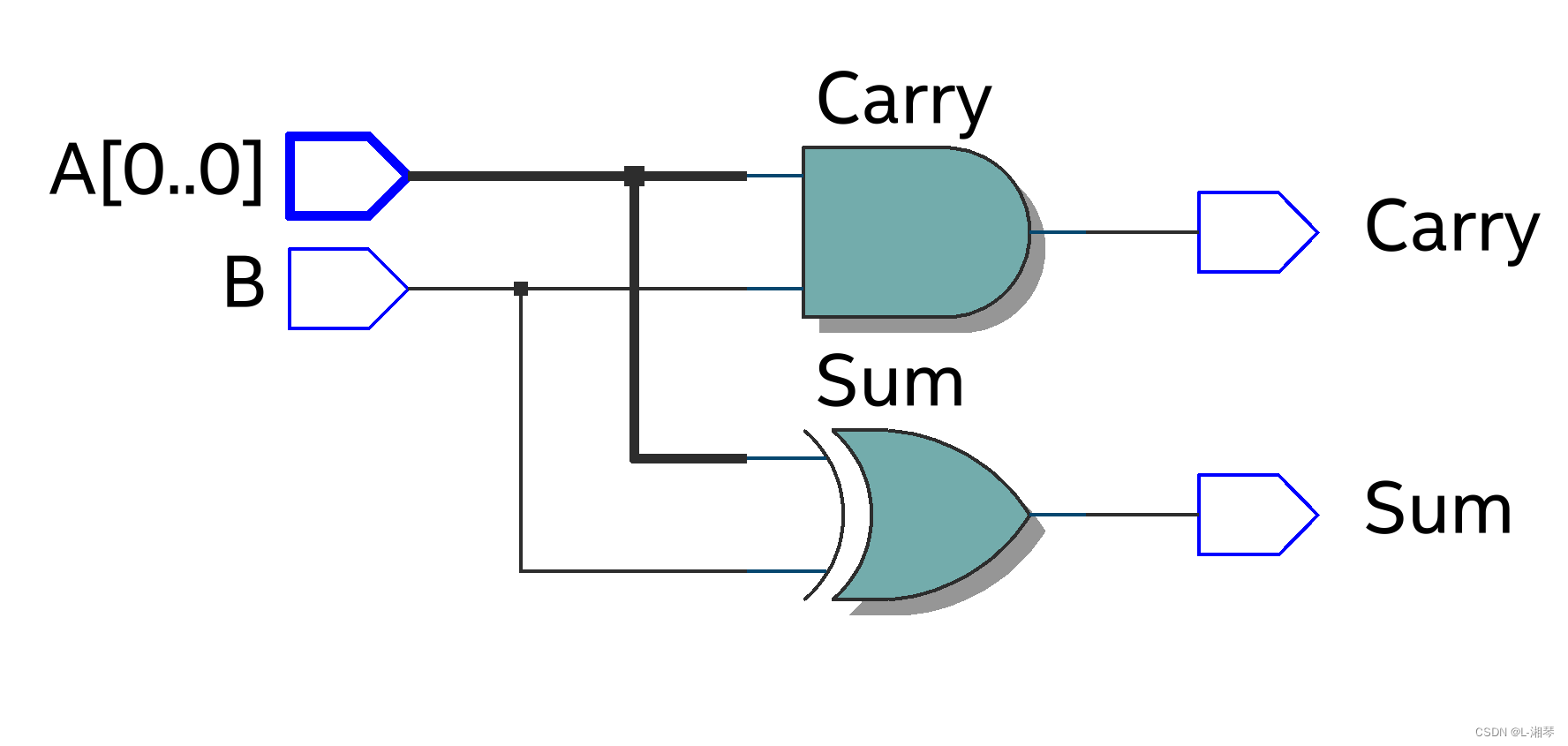

图1 半加器逻辑图

2.2 FPGA 开发思路

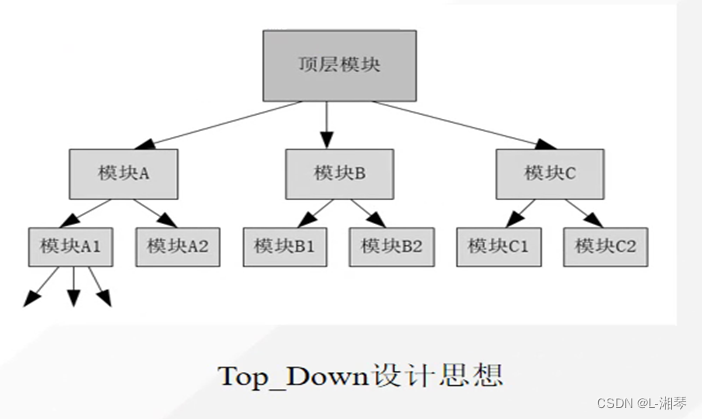

Verilog HDL的设计多采用自上而下的设计方法( top-down) 。即先定义顶层模块功能,进而分析构成顶层模块的必要子模块;然后进一步对各个子模块进行分解和设计,直到到达底层功能块。这样,可以把一个较大的系统,细化成多个小系统,从时间、工作量上分配给更多的人员去设计,从缩短开发周期,节约成本。

例如:我们要设计一个项目,首先根据它所实现的功能及运用到的工具进行模块的划分,以数码管动态显示为例子,我们需要用到的硬件就有 数码管、和定时器,所以我们将其划分为sel_led_dynamic、time_count两个模块,最后用一个top_sel_led_dynamic模块将两个模块进行连接。

sel_led_dynamic模块sel_led_dynamic用于实现LED数码管的动态显示

module sel_led_dynamic(

input clk ,//时钟,50MHz

input rst_n,//复位信号,下降沿有效

input flag ,//周期信号

input sec,

output reg [5:0] sel ,//位选信号,六个数码管

output reg [7:0] seg //段选信号,八段led

);

reg [2:0] cstat ;//当前状态

reg [2:0] nstat ;//下一个状态

reg [3:0] value;

reg [16:0] sec_all;

wire [1:0] hour_h;

wire [3:0] hour_l;

wire [2:0] min_h;

wire [3:0] min_l;

wire [2:0] sec_h;

wire [3:0] sec_l;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin//下降沿有效

sec_all <= 17'd0;

end

else if(sec_all == 17'd86399) begin

sec_all <= 17'd0;

end

else if(sec) begin

sec_all <= sec_all + 1'd1;

end

else

sec_all <= sec_all;

end

//状态跳转

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin//下降沿有效

cstat <= 3'd0;//当前状态置0

end

else begin

cstat <= nstat;//状态跳转

end

end time_count模块用于计时

module time_count(

input clk ,//50MHz时钟信号

input rst_n,//复位信号

output reg flag//一个时钟周期的脉冲信号

);

parameter MAX_NUM = 26'd25_000_000;//计数器最大计数值

reg [25:0] cnt; //时钟分频计数器

//计数器对时钟计数,每0.5s,输出一个时钟周期脉冲信号

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin//按复位时

flag <= 1'b0;//信号为0

cnt <= 26'd0;//计数器清零

end

else if(cnt == MAX_NUM - 1'b1)begin//如果没到时间

flag <= 1'b1;//信号为1

cnt <= 26'd0;//计数器清零

end

else begin //否则到时间

flag <= 1'b0;//信号变为0

cnt <= cnt + 1'b1;//计数器持续累加1

end

end

endmodule

top_sel_led_dynamic模块将两个模块的数据进行整合

module top_sel_led_dynamic(

input clk ,//时钟信号,50MHz

input rst_n,//复位信号,下降沿有效

output [5:0] sel ,//位选信号

output [7:0] seg //段选信号

);

wire flag;//wire连接两个模块

wire sec;

parameter MAX_NUM = 25'd10_000;

parameter TIME = 26'd50_000_000;

time_count #(.MAX_NUM(MAX_NUM)) u_time_count(//实例化计时器模块

.clk (clk) ,//时钟频率,50MHz

.rst_n (rst_n),//复位信号,下降沿有效

.flag (flag) //一个时钟周期的脉冲信号

);

time_count #(.MAX_NUM(TIME)) u1_time_count(//实例化计时器模块

.clk (clk) ,//时钟频率,50MHz

.rst_n (rst_n),//复位信号,下降沿有效

.flag (sec) //一个时钟周期的脉冲信号

);

sel_led_dynamic u_sel_led_dynamic(

.clk (clk),

.rst_n(rst_n),

.flag (flag),

.sec(sec),

.sel(sel),

.seg(seg)

);

endmodule

总结

学习FPGA不易,小白加油吧!

16万+

16万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?