用来验证时钟树上各个结点的时钟频率,输出的时钟信号也可以作为其他外设的时钟。

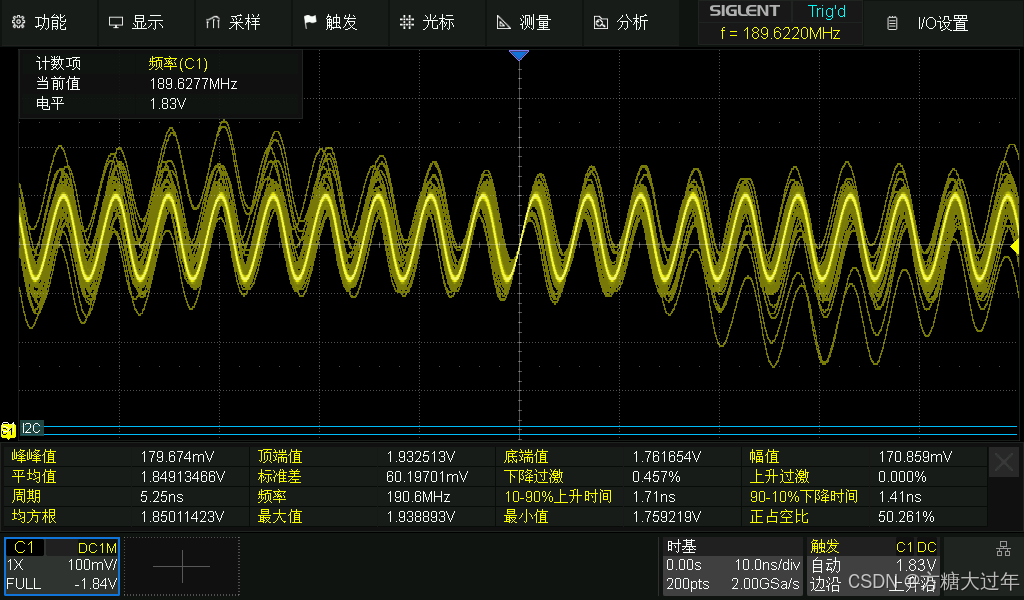

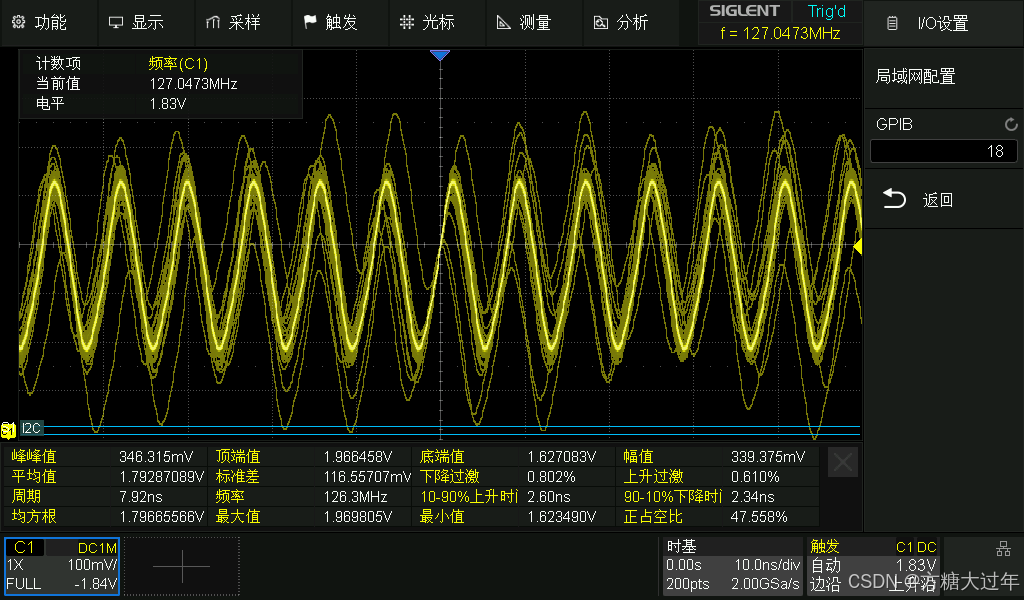

但是频率越高,方波失真越加严重。这是因为方波可以看做是多个谐波叠加成的,而输出端口存在带宽限制,当频率超过带宽时,高频成分会被滤除,剩下的低频成分会形成较为平滑的正弦波

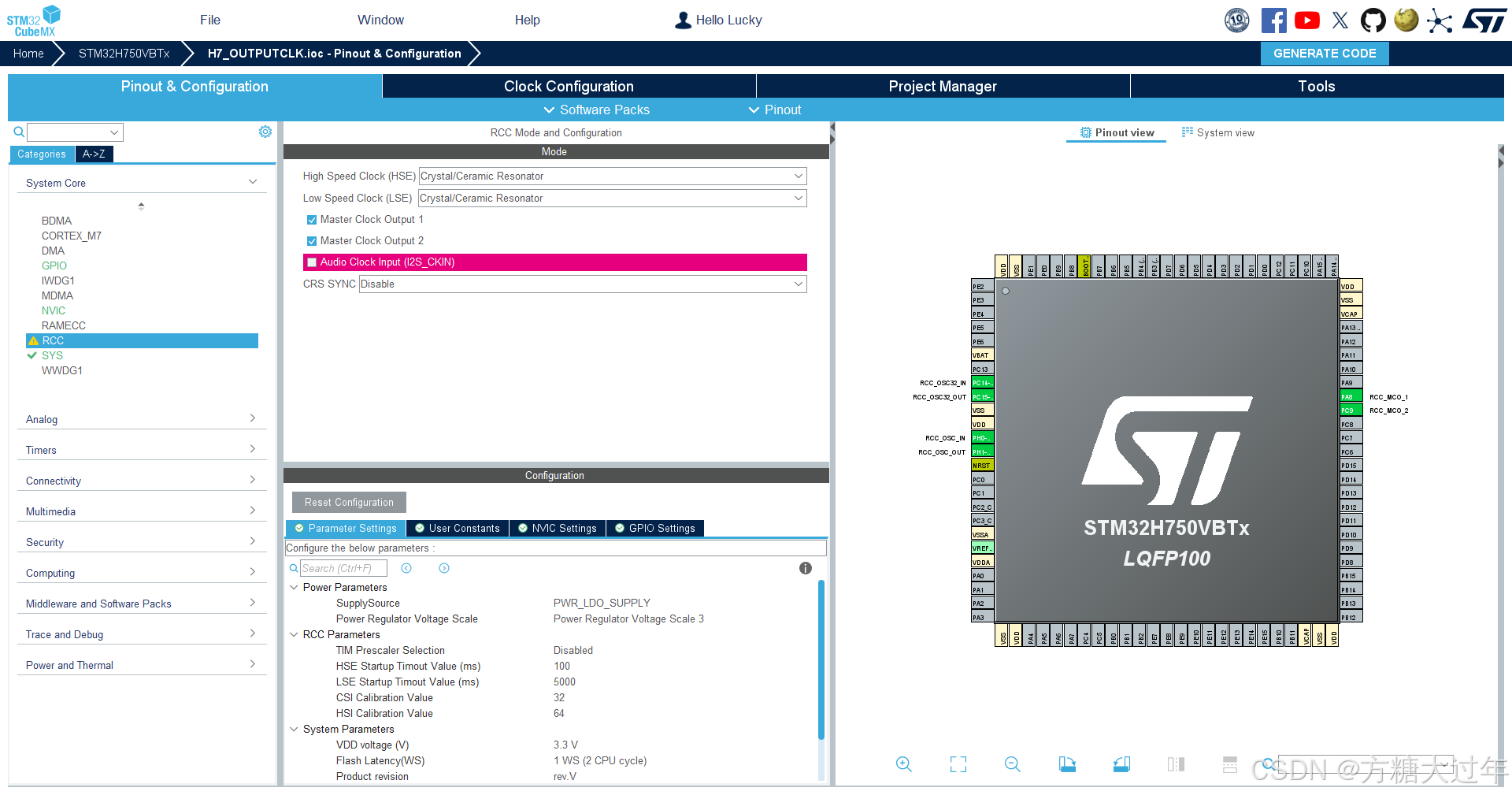

首先打开RCC时钟,勾选“master clock output 1/2”,这里为了实验的方便,两个都选择打开

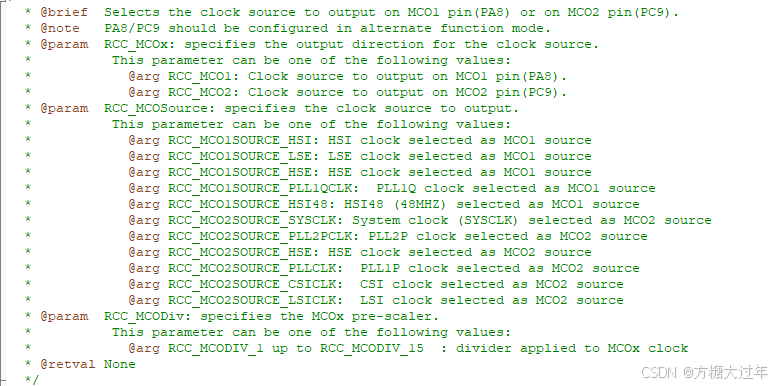

配置时钟输出:跳转到函数定义

参数1可以是RCC_MCO1或者RCC_MCO2,对应的是两个引脚;

参数2可以是时钟树上的结点

参数3是输出的分频系数

HAL_RCC_MCOConfig(RCC_MCO2,RCC_MCO2SOURCE_SYSCLK,RCC_MCODIV_1);

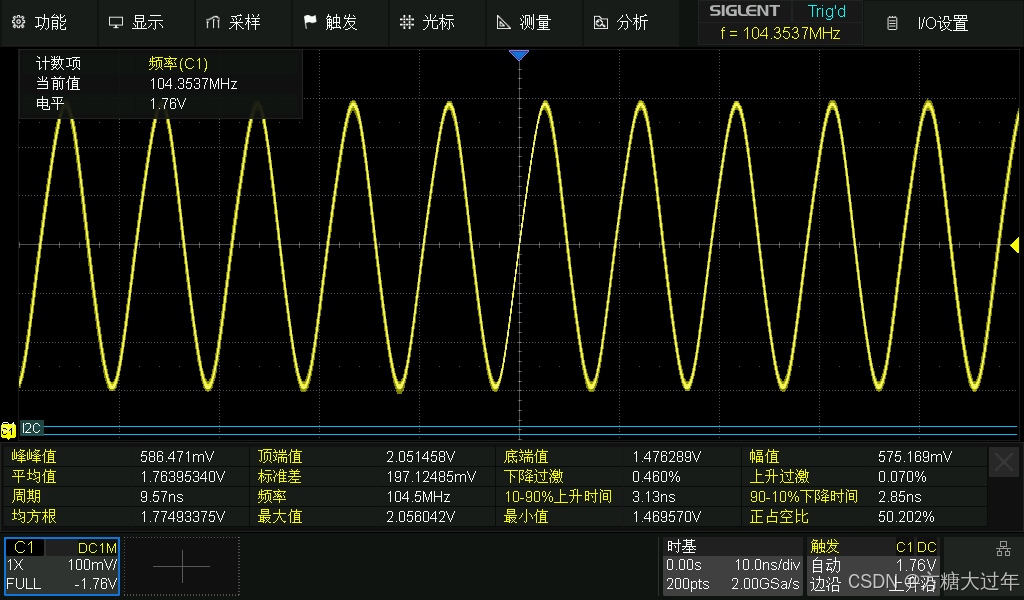

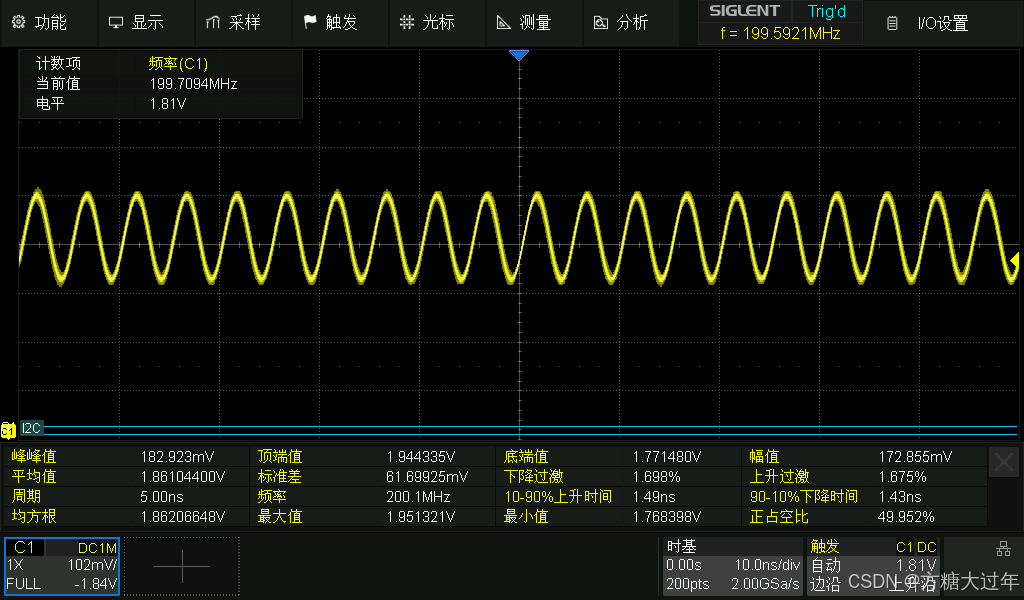

测试效果图:

可能是频率太高,同时使用了杜邦线连接,失真和干扰都很严重

可能是频率太高,同时使用了杜邦线连接,失真和干扰都很严重

去掉杜邦线后可以看到干扰显著减小了

234

234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?