B、C/M bit在DDR的XPI中有实现,即fast/early response , 数据的拆分合并。

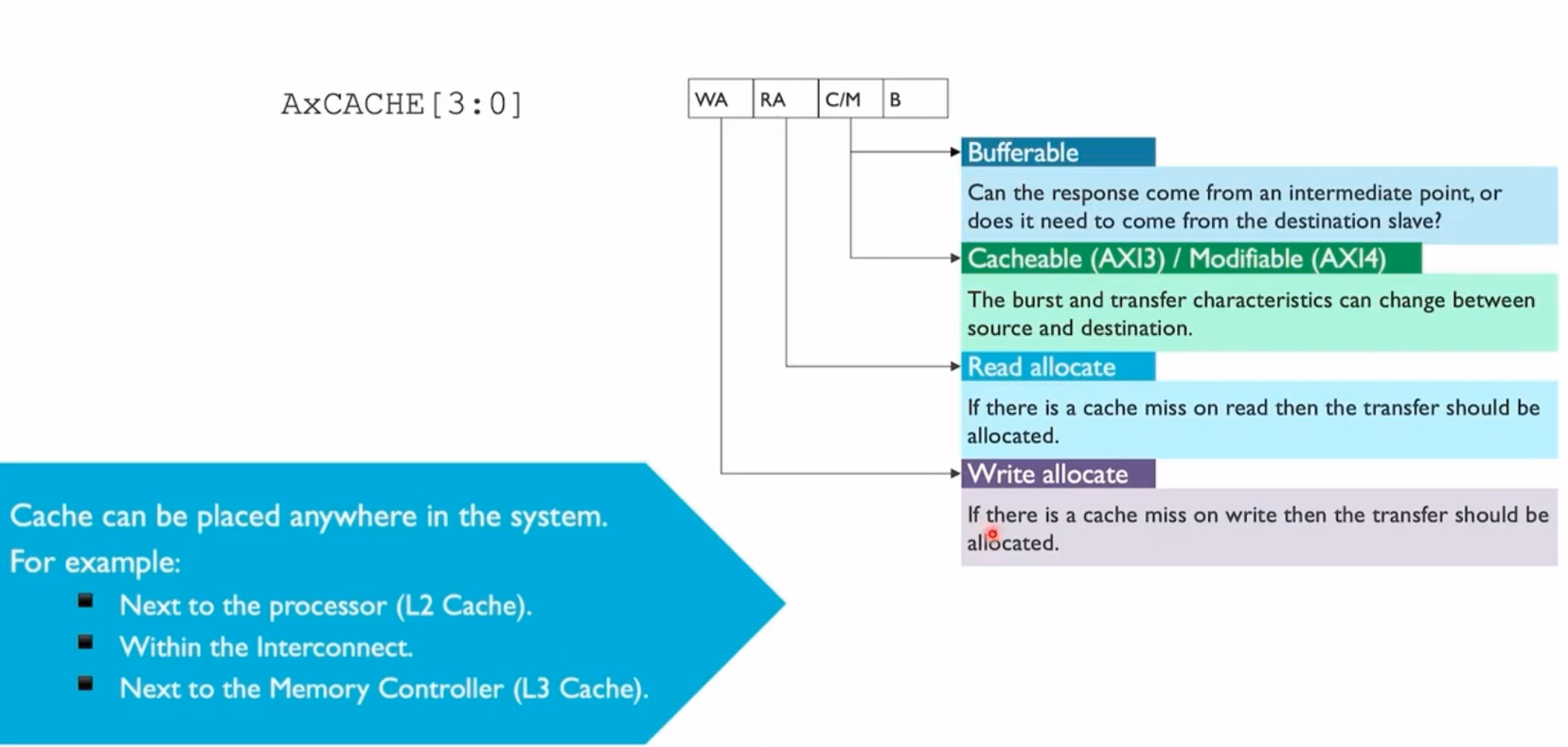

Modern SoC systems often contain caches that are placed in several points of the system. For

example, the level 2 cache might be external to the processor, or the level 3 caches might be in

front of the memory controller.

To support systems that use different caching policies, the AWCACHE and ARCACHE signals

indicate how transactions are required to progress through a system.

The following diagram shows the AxCACHE bit allocations:

The AxCACHE bit allocations specify the following attributes:

• AxCACHE [0] (B) is the bufferable bit. When this bit is set to 1, the interconnect or any

component can delay the transaction reaching its final destination for any number of cycles.

The

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

382

382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?