Ways to fix setup violations:

Setup violation occurs because of high delay in the data path or due to negative skew.

Below are the ways to fix setup violation:

- Gate sizing

- Buffering

- Cloning

- Logic restructuring

- Vt swapping

- Skewing

- Gate Sizing:

This refers to upsizing the cell to a higher drive strength cell.

If a low driving strength cell is driving a higher load, it results in higher cell delay. To fix this, one can upsize the cell which will reduce cell delay and helps to meet the setup time.

- Buffering:

This generally helps if a cell is driving an exceptionally long net.

Considering that the driver cell already has good driving strength, buffering helps to split the net which in turn reduces the total capacitance.

Hence the data path delay will be reduced, and arrival time reduces.

- Cloning:

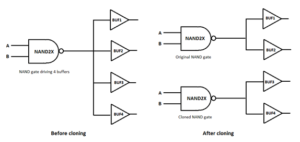

Cloning refers to creating the same driver cell with the same functionality and giving it the same inputs as the original cell.

If gate sizing and buffering are not possible, then cloning can be helpful as this will split the load between the original cell and the newly cloned cell. Refer to the below diagram

Cloning helps in load splitting and hence the driver cell will be having less load capacitance which helps to reduce the cell delay resulting in improvement in data arrival time.

- Logic Restructuring:

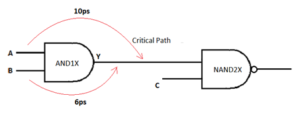

This is the method of re-arranging the logic such that critical paths take the shortest path.

Refer to the figure below;

In the example shown above, the path through Pin A is critical and needs to be optimized.

As delay from A-Y is 10ps and that from B-Y is 6ps, tool directs the critical path to take the less delay path which results in gaining positive slack.

- Vt Swapping:

This method of fixing setup is also known as threshold voltage swapping. There are three different flavors of a cell – HVT, SVT, and LVT. HVT cells have high threshold voltage whereas LVT cells have low threshold voltage.

The HVT cells in the data path can be swapped to LVT cells which have lesser delays for improving the arrival time.

LVT cells require less voltage to turn ON, resulting in lesser cell delay.

- Skewing:

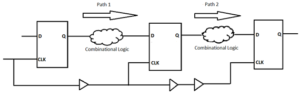

Positive skew is good for setup and negative skew is good for hold. There are 2 ways to fix setup by skewing. This will be easy to understand with the help of the figure below;

Consider setup is getting violated in PATH 1. To fix this using skewing, we can delay the clock at FF2 by adding clock buffers provided that PATH2 has enough setup margin and PATH1 should have enough hold margin.

Consider PATH2 has setup violation. To fix this, we can early the clock at FF2 by optimizing the clock transition or by removing unwanted clock buffers/inverters until unless PATH1 has enough setup margin and PATH2 has enough hold margin.

Ways to fix hold violations:

Hold violations occur if data comes early or due to positive skew.

Below are the steps to fix hold violations;

- Adding buffers/delay cells in the data path

- Vt swapping

- Skewing

- Adding buffers/delay cells in the data path:

Adding buffers or delay cells in the data path increases the data path delay.

But there are certain guidelines for adding buffers or delay cells. Adding buffers/delay cells on the endpoint may give rise to setup violation if the same endpoint is setup critical.

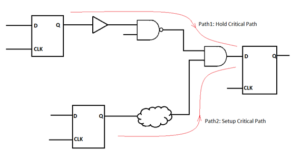

Consider figure below;

Path 1 is hold critical, whereas path 2 is setup critical.

If we add buffer/delay cell at the D pin of capture flop, it may cause setup violation in path 2 as both the paths have the same endpoint.

It’s always a better practice to add buffer/delay cells nearer to startpoint. In this case, you can add it anywhere from the buffer to AND gate in path 1.

- Vt Swapping:

This way is exact opposite of what we do during setup fixing. We can swap lower VT cells to higher VT cells. LVT → SVT → HVT. LVT can be swapped to SVT/HVT and SVT can be swapped to HVT to increased the delay in data path.

- Skewing:

There are 2 ways to fix hold by skewing.

Either we can late skew i.e. increase the clock network delay of launch flop making data to launch late or we can early skew i.e. reduce the clock network delay of capture flop so that data will be reaching faster at the endpoint.

本文详细介绍了在集成电路设计中遇到的设置和保持违规问题,以及相应的修复方法。设置违规通常是由于数据路径延迟过高或负时钟偏斜引起,可以通过门控大小调整、缓冲、克隆、逻辑重构、阈值电压交换和时钟偏移等手段来解决。保持违规则涉及到数据提前到达或正时钟偏斜,解决方法包括增加数据路径中的缓冲器或延迟单元、阈值电压交换和时钟偏移。这些方法有助于优化电路性能,确保满足时序约束。

本文详细介绍了在集成电路设计中遇到的设置和保持违规问题,以及相应的修复方法。设置违规通常是由于数据路径延迟过高或负时钟偏斜引起,可以通过门控大小调整、缓冲、克隆、逻辑重构、阈值电压交换和时钟偏移等手段来解决。保持违规则涉及到数据提前到达或正时钟偏斜,解决方法包括增加数据路径中的缓冲器或延迟单元、阈值电压交换和时钟偏移。这些方法有助于优化电路性能,确保满足时序约束。

3018

3018

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?