目录

CPU的功能:指令控制、操作控制、时间控制、数据加工、中断处理

CPU的功能和基本结构

CPU的功能:指令控制、操作控制、时间控制、数据加工、中断处理

运算器功能:对数据进行加工

控制器功能:协调并控制计算机各部件执行程序的指令序列

基本功能包括取指令、分析指令、执行指令

运算器的基本结构:

1.算数逻辑单元:进行算数、逻辑运算

2.通用寄存器组:用于存放操作数(包括源操作数、目的操作数及中间结果)和各种地址信息。

3.暂用寄存器:用于暂存从主存读来的数据,对应用程序员是透明的。

4.累加寄存器:用于暂时存放ALU运算结果的信息,可作为加法运算的一个输入端

5.程序状态字寄存器:保留由算数逻辑运算指令或测试指令的结果而建立的各种状态信息。溢出、符号、零、进位

6.移位器

7.计数器

控制器的基本结构

控制器有硬布线控制器和微程序控制器两种类型。

1.程序计数器PC:用于指出下一条指令在主存中的存放地址

2.指令寄存器IR:用于保存当前正在执行的那条指令

3.指令译码器:仅对操作字段进行译码

4.微操作信号发生器

5.时序系统

6.存储器地址寄存器MAR

7.存储器数据寄存器MDR

CPU的基本结构:ALU、寄存器、中断系统、CU

用户可见的寄存器:通用寄存器、程序状态寄存器PSW、程序计数器PC

用户不可见的寄存器:MAR、MDR、IR、暂存寄存器

指令周期的数据流

指令的执行过程

指令周期:CPU从主存中每取出一条指令所需的全部时间。

时钟周期->机器周期->指令周期

时钟周期又称节拍、T周期或CPU时钟周期,它是CPU操作的最基本单位

每个指令周期内机器周期数可以不等,每个机器周期内的节拍数也可以不等

指令的周期流程:

四个周期都有CPU访存操作,只是访存的目的不同。

取指周期:取指令

间址周期:取有效地址

执行周期:取操作数

中断周期:保存程序断点

取指周期:

1.(PC)->MAR

2.1->R

3.M(MAR)->MDR

4.(MDR)->IR

5.(PC)+1->PC

间址周期:

1.将地址码送入MAR Ad(IR)->MAR 或 Ad(MDR)->MAR

2.1->R

3.M(MAR)->MDR

4.(MDR)->Ad(IR)

中断周期:

中断:暂停当前的任务去完成其他任务。为了能够恢复当前任务,需要保存断点。一般使用堆栈来保存断点,这里使用SP表示栈顶地址,假设SP指向栈顶元素,进栈操作是先修改指针,后存入数据。

1.CU控制将SP减1,修改后的地址送入MAR

2.1->W

3.(PC)->MDR

4.向量地址->PC

指令执行方案:1.单指令周期2.多指令周期3.流水线方案

数据通路:数据在功能部件之间的传送路径

数据通路的基本结构:

1.CPU内部单总线方式:在同一时刻,只允许两个部件之间进行数据交换

2.CPU内部多总线方式

3.专用数据通路方式

内部总线/系统总线

CPU内部单总线方式:

1.寄存器之间数据传送

2.主存与CPU之间的数据传送

3.执行算数或逻辑运算

专用通路结构

控制器设计

硬布线控制器:微操作控制信号由组合逻辑电路根据当前的指令码、状态和时序,即时产生

微程序控制器:采用“存储程序”的思想,CPU出厂前将所有指令的“微程序”存入“控制器存储器”中

微程序控制器的基本原理

指令流水线

基本概念

指令流水定义

| 顺序执行方式 | 控制简单,硬件代价小 | 执行指令的速度较慢,在任何时刻,处理机中只有一条指令在执行,各功能部件的利用率很低 |

| 一次重叠执行方式 | 程序的执行时间缩短了1/3,各功能部件的利用率明显提高 | 需要付出硬件上较大开销的代价,控制过程也比顺序执行复杂了 |

| 二次重叠执行方式 |

流水线的表示方法

流水线的性能指标:1.吞吐率2.加速比3.效率

1.吞吐率

2.加速比:完成同样一批任务,不使用流水线的时间与使用流水线所用的时间之比

3.效率:流水线的设备利用率

影响流水线的因素

1.结构相关(资源冲突):由于多条指令在同一时刻争用同一资源而形成的冲突

解决方法:

1.后一相关指令暂停一周期

2.资源的重复配置:数据寄存器+指令寄存器

类似于操作系统的互斥

2.数据相关(数据冲突):在同一个程序中,存在必须等前一条指令执行完才能执行后一条指令的情况

解决办法:

1.暂停相关指令:硬件阻塞 , 软件插入“NOP”

2.数据旁路技术 3.编译优化:通过编译器调整指令顺序来解决数据相关

3.控制相关(控制冲突)当流水线遇到转移指令和其他改变PC的值得指令而造成的断流时,会引起控制相关

解决办法:

1.转移指令分支预测:简单预测、动态预测

2.预取转移成功和不成功两个控制流方向上的目标指令

3.加快和提前形成条件码

4.提高转移方向和猜准率

流水线的分类:看看得了

流水线的多发技术:

1.超标量技术

2.超流水技术

3.超长指令字

补充:五段式指令流水线

我还没太体会到知道这玩意儿有啥用。。。。。

多处理器的基本概念:只会考选择题

S单 M多

加图

硬件多线程的基本概念:只考选择题

错题:

5.1

1. 下列不属于控制器的是(程序状态寄存器)

属于的是指令寄存器、程序计数器、时序电路

2.通用寄存器是可编程指定多种功能寄存器

7.在CPU的寄存器中,指令寄存器对用户是透明的

9.PC的值由CPU在执行指令的过程中进行修改

10

19.CPU中不包括地址译码器。地址译码器是主存等存储器的组成部分,其作用是根据输入的地址码唯一选定一个存储单元。

20.间址周期结束时,CPU内寄存器MDR中的内容为操作数地址

21.汇编程序员可见的是程序计数器,即汇编语言程序员通过汇编程序可以对某个寄存器进行访问。汇编程序员可以通过指定待执行指令的地址来设置PC的值,如转移指令、子程序调用指令等。

而IR、MAR、MDR是CPU的内部工作寄存器,对程序员不可见。

5.2

2.

指令周期:CPU从主存中每取出冰执行一条指令所需的全部时间

时钟周期:通常称为节拍或T周期,它是CPU操作的最基本单位

CPU周期也称机器周期,一个机器周包含若干个时钟周期

存取周期:是指存储器进行两次独立的存储器操作(连续两次读或写)所需要的最小间隔时间。

7.取指操作是自动进行的,控制器不需要得到相应的指令

13.中断周期用于响应中断,若有中断,则在指令的执行周期后进入中断周期

14.不同长度的指令,其取指操作可能是不同的。

5.6

1.流水CPU是一种非常经济而实用的时间并行技术

2.超标量通过内置多条流水线来同时执行多个处理器,其实质是以空间换取时间

4.流水CPU是由一系列称为“段”的处理线路组成的。一个m段流水线稳定时的CPU的吞吐能力,与m个并行部件的CPU相比,(具有同等水平的吞吐能力)。

11.在书上

注意:

常规标量单流水线处理机

4级指令流水线

19.不要看答案那个图

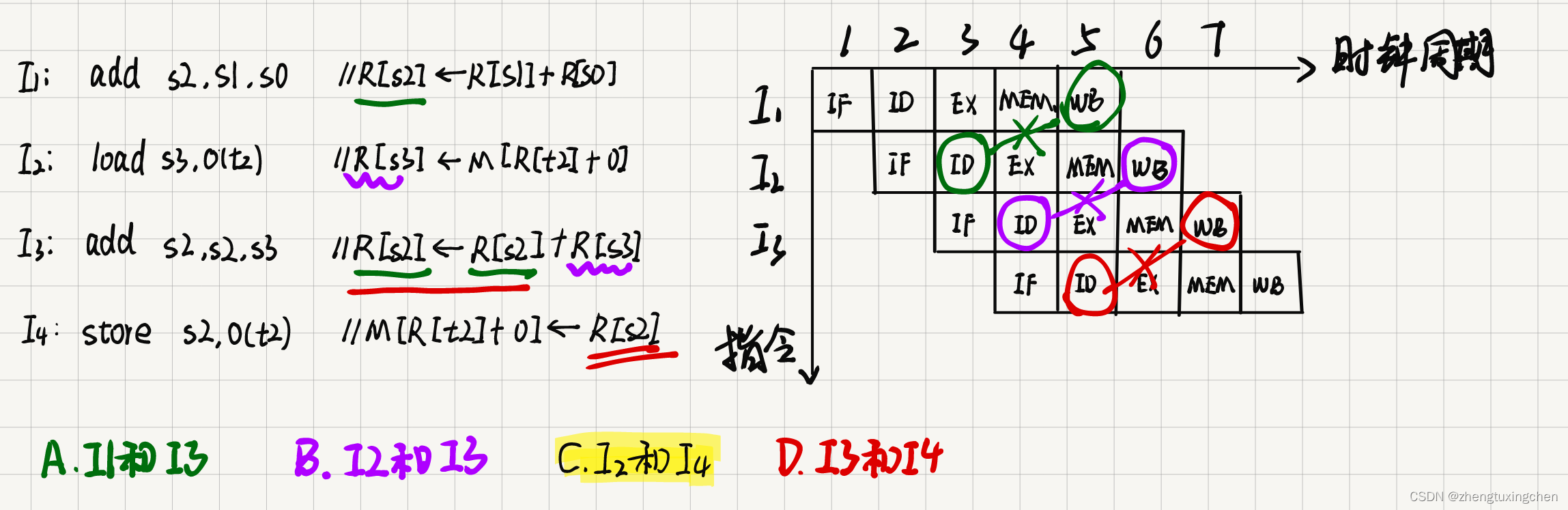

找存在数据冒险->说明这两条指令应该同时访问内存或寄存器->找到有同一个寄存器的

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?