基于FPGA的FIR滤波器滤波

项目简述

上一篇论文中,我们已经讲解了DDS的IP与混频的实现。本篇论文我们将接着上篇文章接着做,在混频之后的信号进行滤波处理。数字滤波器主要有FIR、IIR两种滤波器,但在FPGA中几乎看不到使用IIR滤波器,因为IIR滤波器存在的有限字长效应经反馈后会使得系统不稳定。当然IIR滤波器也有优点,相比同样的频率响应,IIR滤波器的阶数要远小于FIR滤波器。其中因为FIR滤波器的稳定性得到了广泛使用,所以我们主要讲解FIR滤波器。在后面的文章中,我们会手写滤波器代码,并且学习现在信号处理中最重要的内容——自适应信号处理。我们按照循序渐进的步骤,先讲解FIR滤波器IP的使用。

FIR IP的定制及讲解

我们定制FIR滤波器的IP核,必须知道响应的FIR系数的相关信息。这里给同学们提供两种方法:一是使用MATLAB,MATLAB中由专门的库供我们设计‘满足我们要求的函数;二是使用小软件Filter Solutions(随工程一起放入群中,需要的进群自取),使用该工具可以更加方便的设计出来滤波器。由于第二种简单,我们这里以第二种为例。

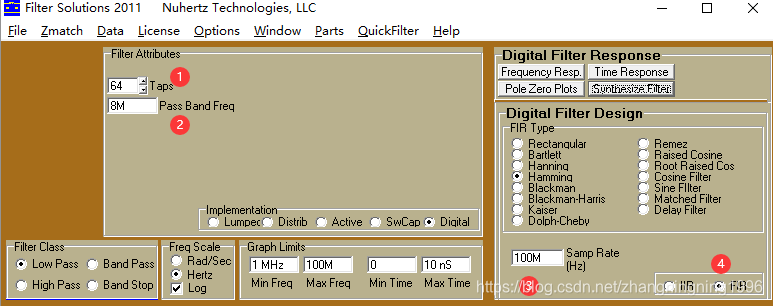

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。整个小软件进行如下的配置:

1、设计滤波器的阶数,我们这里选择了64阶

2、设置低通滤波器的通带频率是8MHz

3、设置采样频率是100MHz

4、使用FIR滤波器

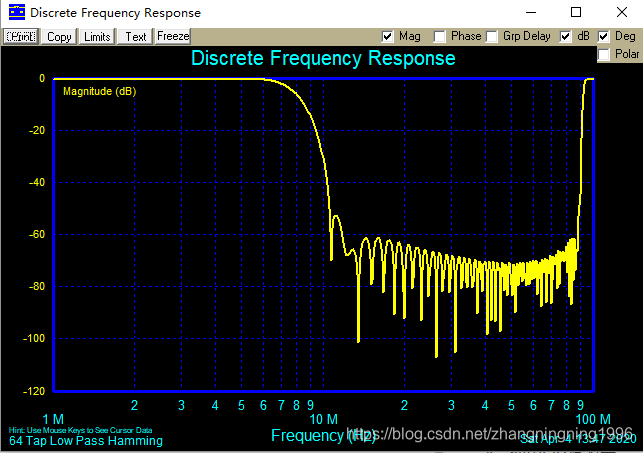

5、点击Frequency Resp观察幅频与相频响应,如下图:

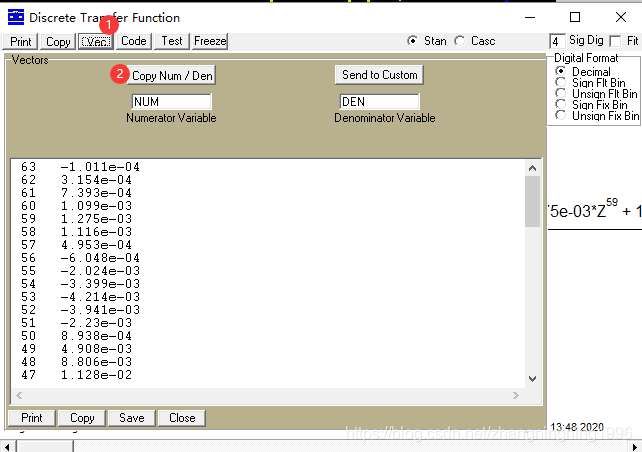

点击Synthesize Filter,再点击其中的vec,如下图:

点击Copy Num/Den复制出相应的系数填入FIR IP的定制界面。

进入Xilinx的FIR IP订制界面,我们可以发现上述界面,其中对我们需要特别关注的配置具体说明一下:

1、我们这

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3978

3978