硬件部分设计

1)建立新项目

2)进行Qsys系统设计

- 点击Tools下拉菜单下的Qsys工具

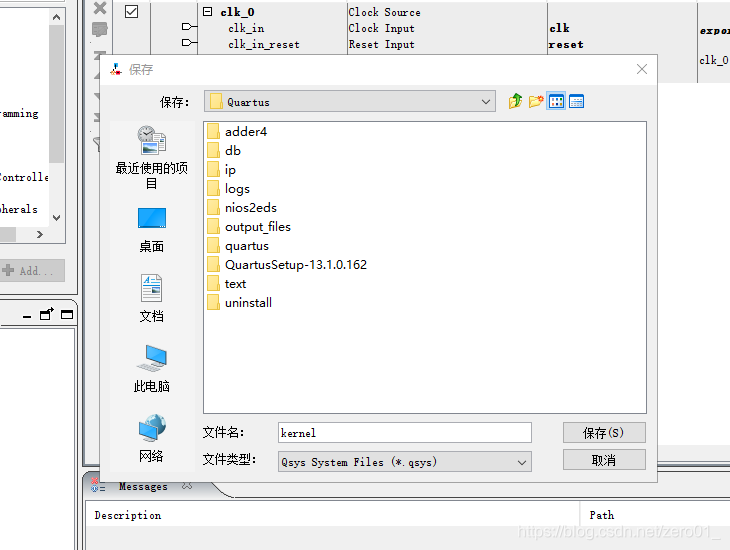

- 启动Qsys后,点击File-save,在文件名中填写为kernel后点击OK

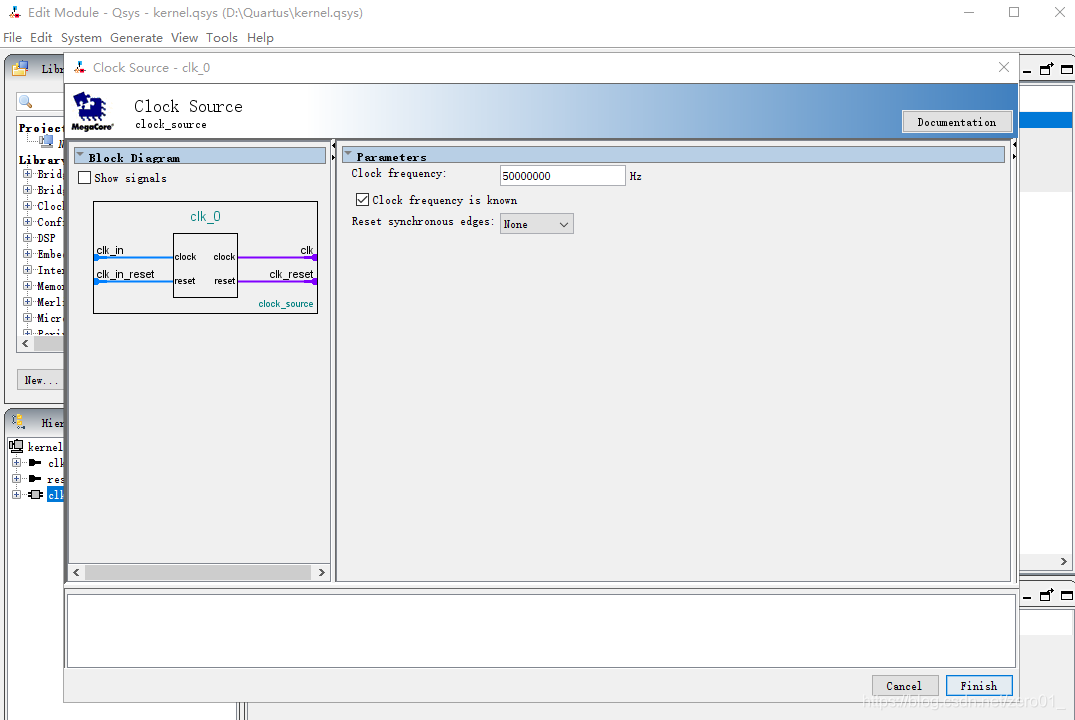

- 双击clk_0元件,对Clock进行时钟设置,设为为50M

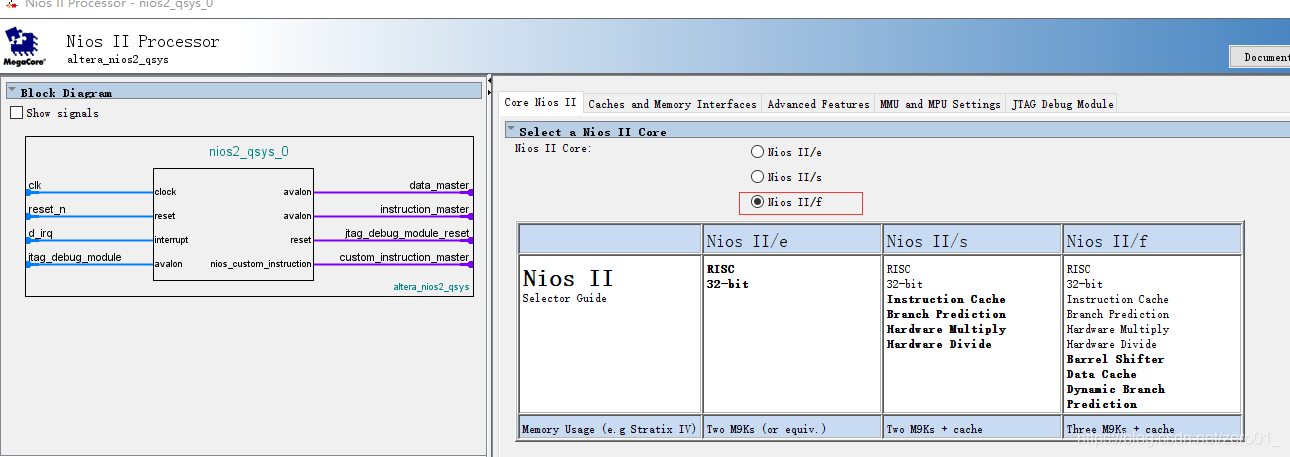

- 在“component library”标签栏中找到“Nios II Processor”后点击Add,在Nios Core栏中选择Nios II/f选项,其他保持默认选项

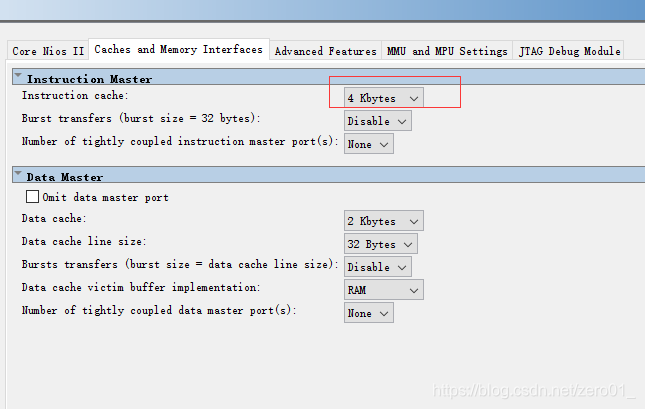

- 在”Caches and Memory Interfaces”标签栏中保持默认设置(Instruction Cache选择4Kbytes),其他全部保持默认设置。

- 将nios2_qsys_0重命名为cpu,点击”Rename”即可重新命名

本文详细介绍了如何在FPGA中使用NIOS-II软核进行硬件设计,包括Qsys系统设计、时钟设置、CPU、片上存储器、PIO接口和中断的配置。内容涵盖从新项目的建立到Qsys系统的生成,以及顶层文件的创建,为初学者提供了全面的入门指导。

本文详细介绍了如何在FPGA中使用NIOS-II软核进行硬件设计,包括Qsys系统设计、时钟设置、CPU、片上存储器、PIO接口和中断的配置。内容涵盖从新项目的建立到Qsys系统的生成,以及顶层文件的创建,为初学者提供了全面的入门指导。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1264

1264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?