基于Verilog HDL的数字秒表设计

一、EDA

电子设计自动化(英语:Electronic design automation,缩写:EDA)是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

二、基于Verilog HDL的数字秒表设计

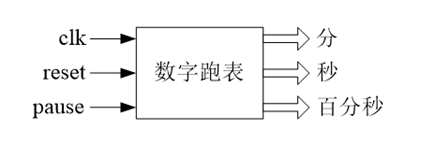

1、 用Verilog HDL设计一个数字跑表,所需引脚和功能如下所示:

2、代码示例

module running_gly(clk,reset,pause,msh,msl,sh,sl,minh,minl);

input clk,reset,pause;

output [3:0] msh,msl,sh,sl,minh,minl;

reg [3:0] msh,msl,sh,sl,minh,minl;

reg count1,count2;

always @(posedge clk or posedge reset)

begin

if(reset)

begin

{msh,msl}<=0;

count1<=0;

end

else if(!pause)

begin

if(msl==9)

begin

msl<=0;

if(msh==9)

begin

msh<=0;

count1<=1;

end

else

msh<=msh+1;

end

else

begin

msl<=msl+1;

count1<=0;

end

end

end

always@(posedge count1 or posedge reset)

begin

if(reset)

begin

{sh,sl}<=0;

count2<=0;

end

else if(sl==9)

begin

sl<=0;

if(sh==5)

begin

sh<=0;

count2<=1;

end

else

sh<=sh+1;

end

else

begin

sl<=sl+1;

count2<=0;

end

end

always @(posedge count2 or posedge reset)

begin

if(reset)

begin

minh<=0;

这篇博客介绍了基于Verilog HDL的数字秒表和多功能数字时钟的设计,详细阐述了设计要求、代码示例及结果展示。同时,文章还提及了一个基于FPGA的贪吃蛇游戏的系统结构,包括食物生成、状态控制和红外解码模块。

这篇博客介绍了基于Verilog HDL的数字秒表和多功能数字时钟的设计,详细阐述了设计要求、代码示例及结果展示。同时,文章还提及了一个基于FPGA的贪吃蛇游戏的系统结构,包括食物生成、状态控制和红外解码模块。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1534

1534

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?