module shift_1x64 (clk,

shift,

sr_in,

sr_out,

);

input clk, shift;

input sr_in;

output sr_out;

reg [63:0] sr;

always@(posedge clk)

begin

if (shift == 1'b1)

begin

sr[63:1] <= sr[62:0];

sr[0] <= sr_in;

end

end

assign sr_out = sr[63];

endmodule

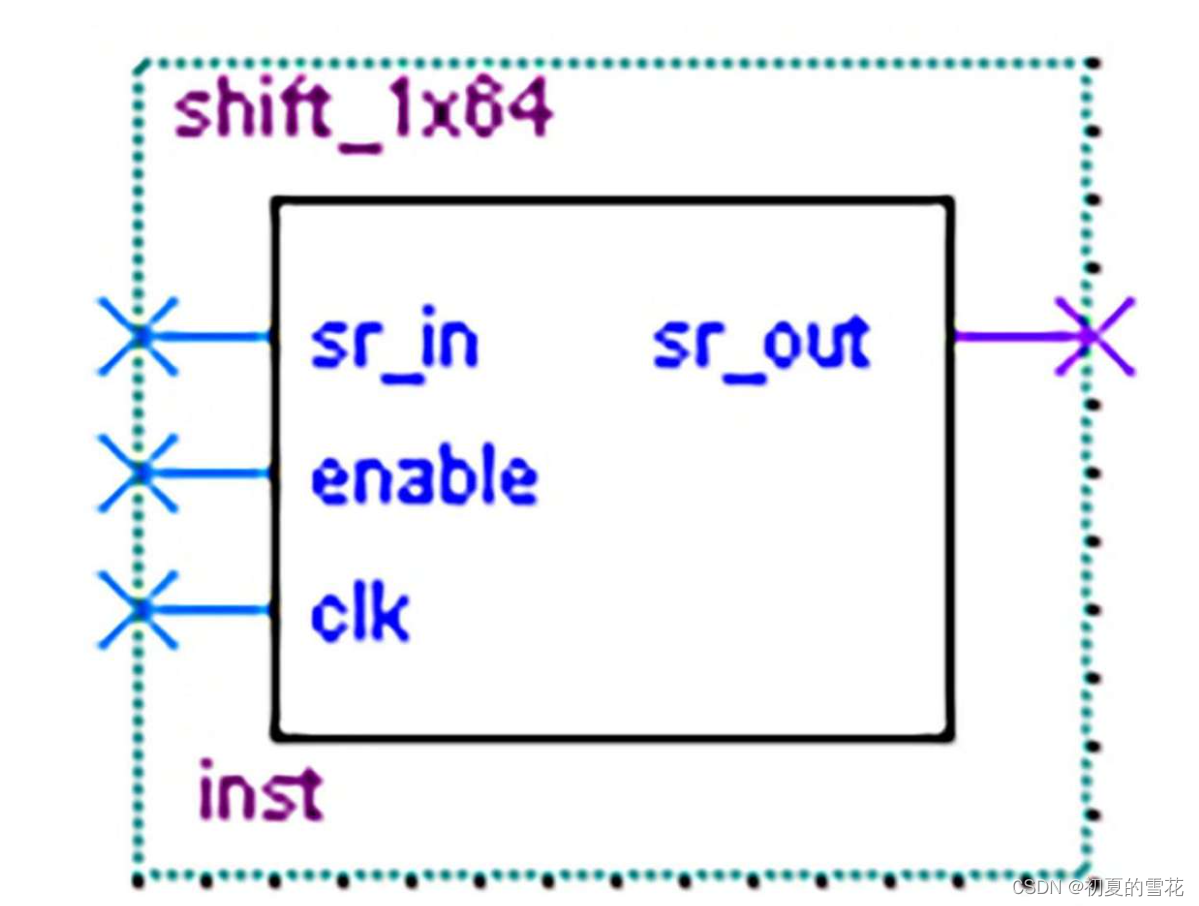

这个Verilog模块 `shift_1x64` 实现了一个 64 位移位寄存器,它具有以下关键特性:

1. 时钟触发:移位操作是由外部时钟信号 `clk` 上升沿触发的。

2. 移位控制:移位操作由 `shift` 信号控制,当 `shift` 为高电平(1)时,移位操作执行。

3. 数据输入:可以通过 `sr_in` 输入新的数据,该数据会在移位操作时加载到寄存器的最低位。

4. 数据输出:模块的输出 `sr_out` 是移位寄存器的最高位(Bit 63)的值。

5. 移位操作:在移位操作触发时,寄存器内的数据会向左移动一位,最高位的数据被丢弃,最低位被加载新的 `sr_in` 数据。

这个模块允许你在时钟上升沿触发时执行数据的左移位操作,并通过 `sr_in` 输入新的数据,以便在移位后将其加载到寄存器的最低位。同时,你可以通过 `sr_out` 输出寄存器的最高位的值。

这篇文章详细描述了一个名为shift_1x64的Verilog模块,实现了一个64位移位寄存器,通过clk时钟上升沿触发,shift信号控制移位,sr_in输入新数据,sr_out输出最高位。移位操作中数据左移并保持最低位数据。

这篇文章详细描述了一个名为shift_1x64的Verilog模块,实现了一个64位移位寄存器,通过clk时钟上升沿触发,shift信号控制移位,sr_in输入新数据,sr_out输出最高位。移位操作中数据左移并保持最低位数据。

4291

4291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?