亚稳态:触发器因不满足建立时间和保持时间而输出端无法在一个规定时间内到达一个确定的状态。亚稳态问题可以传播,会导致系统不稳定,亚稳态有恢复时间。

两种时序分析方法:静态时序分析和动态时序分析。

四种时序路径:输入到输出,输入到寄存器,寄存器到寄存器,寄存器到输出。

相关文章:

【转载】FPGA中亚稳态——让你无处可逃 https://www.cnblogs.com/houxiliang/p/8990801.html

亚稳态以及测试逻辑实现 https://blog.youkuaiyun.com/DdiIcey/article/details/77720197

补充:

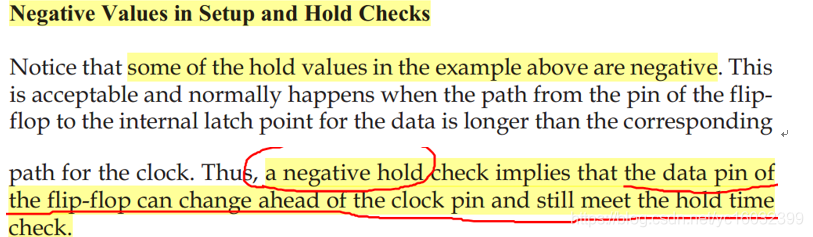

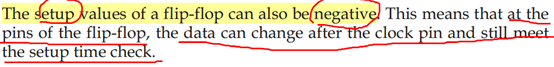

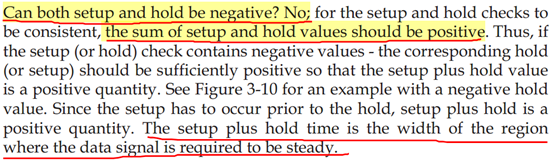

负建立时间和负保持时间

亚稳态是指在FPGA中,由于不满足触发器的建立时间和保持时间导致输出无法稳定。这一问题可能导致系统不稳定,并且有恢复时间。静态和动态时序分析是常见的分析方法,而四种时序路径包括输入到输出、输入到寄存器、寄存器到寄存器以及寄存器到输出。负建立时间和负保持时间是特殊情况,但两者之和必须大于零以确保正确采样。

亚稳态是指在FPGA中,由于不满足触发器的建立时间和保持时间导致输出无法稳定。这一问题可能导致系统不稳定,并且有恢复时间。静态和动态时序分析是常见的分析方法,而四种时序路径包括输入到输出、输入到寄存器、寄存器到寄存器以及寄存器到输出。负建立时间和负保持时间是特殊情况,但两者之和必须大于零以确保正确采样。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

417

417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?