45 nm RF-SOI CMOS 中低功耗 24 GHz 压控振荡器的设计

摘要

本工作提出了一种用于调频连续波(FMCW)雷达基站的低功耗 24 GHz LC 交叉耦合压控振荡器(VCO)的设计。该 VCO 采用 45 nm 射频 SOI 技术制造,因其无源器件具有比体 CMOS 技术更高的品质因数。在印刷电路板(PCB)上实测时,已制造的 VCO 在 1 V 电源下仅消耗 12.3 mA 电流,实现了 2.15 GHz/mW 的功率效率,优于其他最先进的 LC 交叉耦合 VCO。该设计采用一个两位电容阵列,实现了 9% 的调谐范围。实测相位噪声在 1 MHz 和 10 MHz 偏移频率下分别为 -96.4 dBc/Hz 和 -119 dBc/Hz。在 10 MHz 偏移频率下,其品质因数(FOM)达到 -179.5 dBc/Hz。

关键词

压控振荡器,FMCW 雷达,低功耗。

I. 引言

基于调频连续波(FMCW)雷达的室内定位系统在近几年变得非常流行,被广泛应用于安全疏散系统和室内导航系统等场景中,用于对人员或物体进行跟踪与定位。

FMCW 雷达系统的主要组成部分之一是压控振荡器(VCO)。传统的 VCO 通常采用 LC 谐振电路,设计使其在所需的工作频率下谐振。为了提高目标检测能力,FMCW 雷达的 VCO 需具备低相位噪声 [1]。此外,为了应对工艺偏差,还需要较宽的调谐范围。对于电池供电设备而言,低功耗也至关重要。通过向深亚微米 CMOS 工艺缩小尺寸,可以实现快速晶体管和低功耗 [2]。然而,在毫米波频段下,随着工艺尺寸的缩小,带来了诸多设计挑战。首先,高导电性的衬底会降低 VCO LC 谐振电路中无源元件的品质因数 [2]-[6];其次,电源电压的降低限制了最大振荡输出摆幅,恶化了相位噪声性能,并减小了 VCO 的控制电压范围 [2],[7]-[8]。因此,在 20 GHz 以上的频率下实现低相位噪声将导致功耗显著增加 [3]。由于 SOI-CMOS 技术中的无源器件品质因数高于体硅 CMOS 技术 [2],因此本设计采用 45 nm RF-SOI CMOS 工艺来实现一款低功耗 24 GHz 压控振荡器。

本文其余部分组织如下:在第二节中,介绍了实现的 VCO 设计。然后在第三节中,展示了晶圆探针台和印刷电路板(PCB)上的仿真和测量结果。接着与最先进的 CMOS 压控振荡器进行了比较。最后,在第四节中,总结了本工作成果。

II. 电路设计

考虑到相位噪声的利森方程简化形式 [3]:

$$

L{\Delta f} = 10 \log\left( \frac{1}{8Q^2} \cdot \frac{FkT}{P_{sig}} \cdot \left(\frac{f_0}{\Delta f}\right)^2 \right)

$$

其中,$L{\Delta f}$ 是以 dBc/Hz 为单位的单边带相位噪声功率谱密度,$\Delta f$ 是相对于载波的频偏(单位为赫兹),$f_0$ 是振荡频率(单位为赫兹),$Q$ 是有载谐振器品质因数,$P_{sig}$ 是以瓦特为单位的信号功率,$F$ 是振荡器噪声系数,$k$ 是玻尔兹曼常数,$T$ 是开尔文温度。

根据公式(1),为了降低相位噪声,应提高谐振腔品质因数和/或信号功率(从而提高直流功耗)。由于该压控振荡器将用于电池供电的调频连续波雷达系统,因此希望降低功耗。因此,需要提高谐振电路的品质因数,以改善工作频率下的相位噪声性能。在 45 纳米 SOI 工艺中,可以实现品质因数高于体 CMOS 工艺的电感和变容二极管 [2]。

选择差分 LC 交叉耦合压控振荡器拓扑结构(图1),因其对称结构可提供更好的共模抑制和更低的闪烁噪声拐点 [9]。压控振荡器振荡频率由以下公式确定:

$$

f_0 = \frac{1}{2\pi \sqrt{L(C_{var} + C_{fixed} + C_{par})}}

$$

其中 $L$ 为电感,$C_{var}$ 为与固定电容 $C_{fixed}$ 并联的变容二极管电容,$C_{par}$ 为来自交叉耦合晶体管、输出缓冲器以及布线的寄生电容。

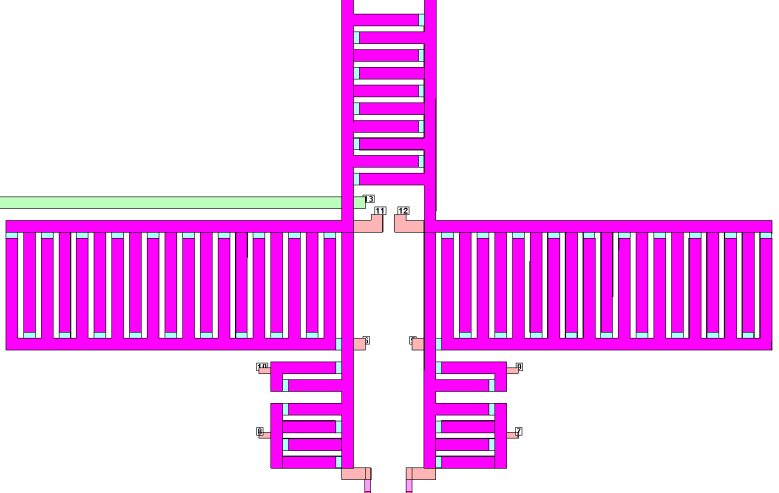

采用了一个对称中心抽头电感,其电感 $L$ 在 24 GHz 时为 113 pH,品质因数为 30.7。变容二极管设计为在 24 GHz 时具有 10 fF 的 $C_{min}$ 和 50 fF 的 $C_{max}$,对应的品质因数分别为 5 到 25 之间。变容二极管的偏置使得最大斜率出现在 0.5 V 的中间电源电压处。因此,本设计中使用了 400 fF 的隔直电容($C_{dc-block}$),以阻止变容二极管偏置电压($V_{bias}$)进入压控振荡器输出节点。在估计寄生电容为 200 fF 后,采用 220 fF 的固定电容 $C_{fixed}$,以根据 (2) 实现 24 GHz 的振荡频率。为了补偿工艺偏差,使用可切换的 2 位电容阵列($C_{b1}$,$C_{b0}$)来增加压控振荡器频率调谐范围。固定电容($C_{fixed}$)、隔直电容($C_{dc-block}$)和电容阵列($C_{b1}$,$C_{b0}$)均定制设计为金属-氧化物-金属电容器,并使用 SONNET 进行电磁(EM)仿真(图2),以考虑对压控振荡器输出节点附加的寄生电感和电容。

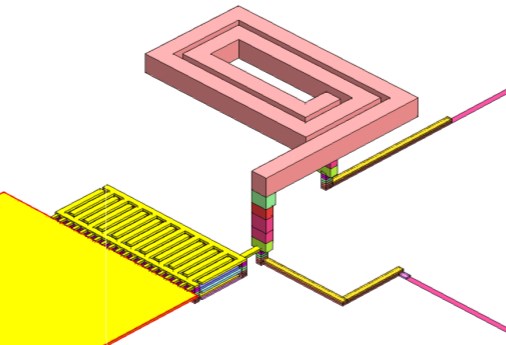

采用电流镜为压控振荡器提供偏置电流,其中设计了一个 LC 噪声滤波器(图3),使其在二次谐波频率处谐振,以降低压控振荡器的相位噪声 [10]。差分压控振荡器输出被送入一个共漏极输出缓冲器,随后连接一个输出匹配网络,该网络也经过电磁仿真(图4)。输出匹配网络包括一个并联电感(同时提供静电放电保护)和一个串联电容(同时作为输出直流隔离电容)。

III. 仿真与测量结果

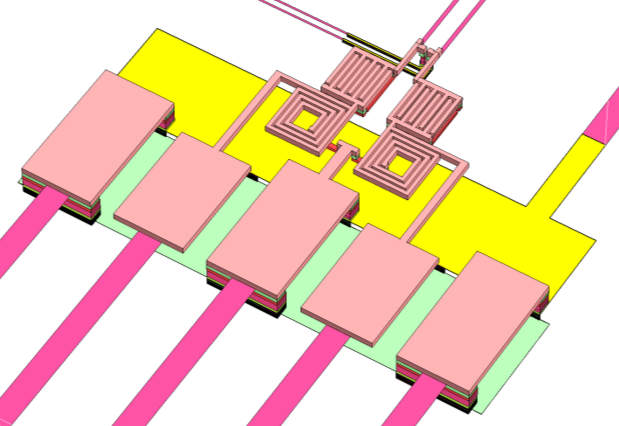

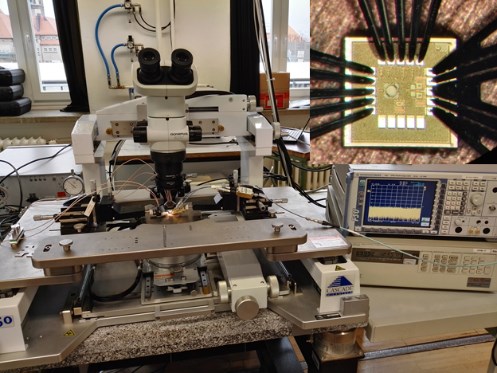

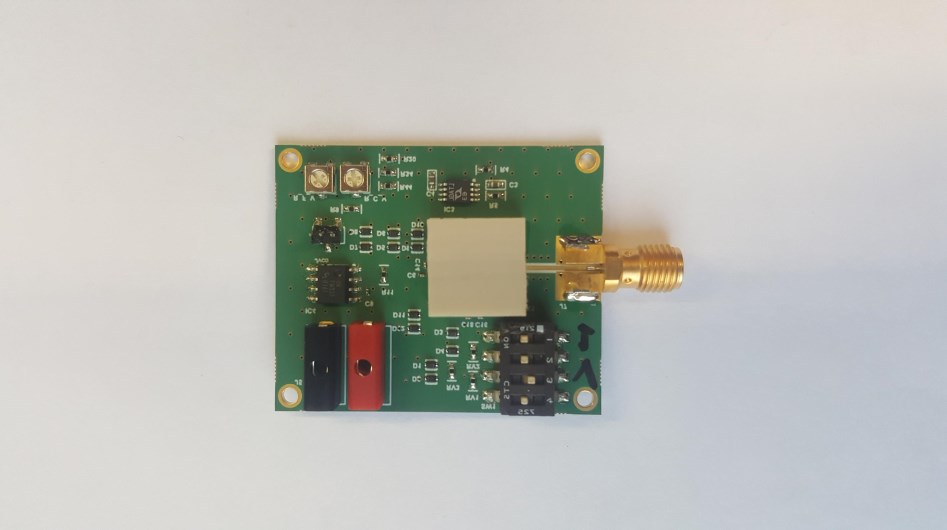

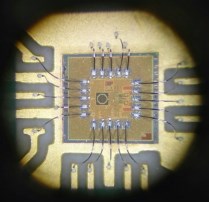

该 VCO 设计基于 45 nm 射频 SOI 技术制造,总面积为 0.64 mm²。芯片照片和片上测量装置如图5所示。此外,两个 VCO 芯片被键合在 Rogers 4350B 印制电路板上(图6)。总直流功耗测量值为 12.3 mW,其中 VCO 核心消耗 5.1 mW,输出缓冲器消耗 7.2 mW。

图7 显示了实测与仿真相位噪声(PN)曲线之间良好的一致性,在 1 MHz 和 10 MHz 偏移频率处分别实现了 -96.4 dBc/Hz 和 -119 dBc/Hz 的实测相位噪声。10 MHz 之后的差异是由于频谱分析仪的 -130 dBc/Hz 相位噪声底限所致。

图8 和图9 显示了在印刷电路板和晶圆探针台上测得的仿真与实测 VCO 调谐曲线。测量中观察到 $f_0$ 增加了 3%,可能是由于工艺偏差所致。在中间调谐范围内,测得 VCO 增益($K_{vco}$)为 1.4 GHz/V。已制造的 VCO 实现了 9% 的频率调谐范围,其中频率调谐范围(TR)定义为:

$$

TR = \frac{f_{max} - f_{min}}{f_{center}} \times 100\%

$$

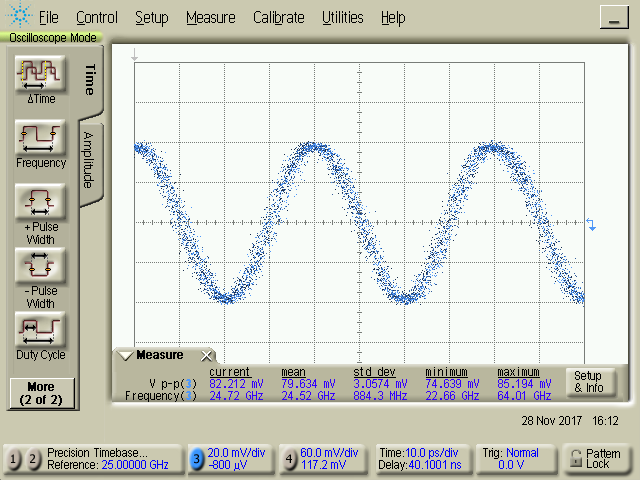

使用安捷伦 86100 数字通信分析仪测量了 VCO 瞬态输出信号,如图10所示。测得的 82.2 mV 峰峰值信号对应 -17.7 dBm。考虑到从 VCO 到分析仪路径中的 7 dB 损耗,估计实际的 VCO 输出功率为 -10.7 dBm。尽管输出功率在仿真中为 -8.2 dBm,但该差异估计是由于工艺偏差和/或 24 GHz SMA 连接器焊接不完美所致。

表1 展示了与其他先进 CMOS 压控振荡器的比较。采用文献 [3] 中定义的常用品质因数(FOM)进行对比:

$$

FOM = L{\Delta f} - 20 \log\left(\frac{f_0}{\Delta f}\right) + 10 \log\left(\frac{P_{DC}}{1\,\text{mW}}\right)

$$

此外,还考虑了另一个将调谐范围纳入考量的品质因数(FOMₜ),如 [4] 中所示,其定义为:

$$

FOM_T = L{\Delta f} - 20 \log\left(\frac{TR}{10} \cdot \frac{f_0}{\Delta f}\right) + 10 \log\left(\frac{P_{DC}}{1\,\text{mW}}\right)

$$

其中 $P_{DC}$ 为直流功耗(单位为毫瓦),$\Delta f$ 为相对于载波的频偏。该压控振荡器在 10 MHz 偏移频率下表现出具有竞争力的 FOM 和 FOMₜ,分别为 -179.5 和 -178.6 dBc/Hz,同时在其他 LC 交叉耦合压控振荡器中实现了最高的功率效率($\eta$),达到 2.15 GHz/mW,其中:

$$

\eta = \frac{f_{max}}{P_{DC}}

$$

表1. 与最先进的 CMOS VCO 的比较

| 参数 | [3] | [6] | [5] | [8] | [13] | [14]¹ | [15] | [3] | [7] | [11] | [12] | 本工作 | 本工作 | 单位 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 工艺 | 180 | 180 | 110 | 180 | 110 | 180 | 180 | 180 | 130 | 130 | 130 | 45 RF-SOI | 45 RF-SOI | nm |

| $P_{dc}$ | 11 | 15 | 160 | 16.8 | N/A | 10.1 | 25 | 45 | 43 | 42.8 | 18 | 12.3 | 12.3 | mW |

| 电源 | 2.2 | 1.8 | 2 | 0.6 | 1.2 | 1.7 | 1.8 | 3 | 2 | 1.35 | 1.2 | 1 | 1 | V |

| Area | 0.58 | 0.56 | 0.14 | 0.16 | 0.39 | 0.13 | 0.23 | 23.83 | 0.544 | 0.5 | 0.49 | 0.83 | 0.64 | 0.64 |

| $f_0$ | 23 | 23.5 | 23.5 | 24.39 | 24 | 24.6 | — | — | 23 | 24.62 | 25 | 24.3 | 25 | GHz |

| $f_{max}$ | 25.1 | 25.9 | 24.25 | 25 | 24.85 | 26.4 | 25.3 | 21.6 | — | 25.5 | 26.5 | 26.5 | 26.5 | GHz |

| 调谐范围 | 12 | 20 | 6.35 | 3.4 | 6.7 | 15.5 | 12.6 | 6.25 | 13 | 4.3 | 11.8 | 9 | 9 | % |

| 1 MHz 时的相位噪声 | -99.9 | -100 | — | — | — | — | -95 | — | — | -97 | -111.6 | -95.3 | -96.4 / -119² | dBc/Hz |

| $P_{out}$ | -18.8 | -8.5 | 8.4 | -10 | N/A | -12 | 4.37 | -4.2 | 4 | -6.4 | N/A | -10.7 | -10.7 | dBm |

| 输出缓冲器 | Y | Y | N | Y | Y | Y | Y | Y | Y | Y | N | Y | Y | — |

| PCB 测量 | N | N | N | N | N | N | N | N | N | N | N | Y | Y | — |

| 效率 | 2.28 / -177.5 | 1.73 / -175.7 | 0.15 / -160.7 | 1.49 / -185.5 | N/A / -180.1 | 2.61 / -179.8 | 1.01 / -174.9 | 0.48 / -171.9 | 0.57 / -173.4 | 0.59 / -185.7 | 1.42 / -170.5 | 2.15 / -177 / -179.5² | 2.15 / -177 / -179.5² | GHz/mW |

| 1 MHz 时的品质因数 | -179.1 | -181.7 | -156.8 | -176.2 | -176.6 | -183.6 | -176.9 | -171.8 | -175.6 | -178.3 | -171.9 | -176 / -178.6² | -176 / -178.6² | dBc/Hz |

| FOMT@1 MHz | — | — | — | — | — | — | — | — | — | — | — | — | — | dBc/Hz |

| 拓扑结构 | 12 GHz 核心 + 倍频器 | 12 GHz 核心 + 倍频器 | 基于变压器 | 基于变压器 | 基于变压器 | 电流复用 | 电流复用 | LC 交叉耦合 | LC 交叉耦合 | LC 交叉耦合 | LC 交叉耦合 | LC 交叉耦合 | LC 交叉耦合 | — |

¹ 非对称核心,缺乏差分设计的优势

² 在 10 MHz 偏移频率处

IV. 结论与未来工作

一款 24 GHz VCO 采用 45 nm 射频 SOI 技术设计并制造。该已制造的 VCO 在保持低直流功耗和高功率效率的同时,实现了低相位噪声和相对较宽的调谐范围。未来的工作包括 FMCW 雷达基站的设计、进行测距测量以及评估测距精度和准确度。

121

121

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?