作为电子工程师,我们每天都在接触各种不同封装的芯片,这里收集了一篇介绍芯片封装的科普文章,可以帮助对芯片的封装过程有一些了解,这样可以给我们在分析电路问题的时候带来一些帮助,思路上可以打开一些。

一、芯片封装目的

半导体芯片封装主要基于以下四个目的: 防护、 支撑、 连接、 可靠性

(1) 防护:裸露的装芯片只有在这种严格的环境控制下才不会失效,如恒定的温度(23±3℃)、恒定的湿度(50±10%)、严格的空气尘埃颗粒度控制(一般介于 1K 到 10K)及严格的静电保护措施,但是,实际生活中很难达到这种要求,如工作温度可能低至-40℃、高至60℃、湿度也可能达到100%,为了要保护芯片,所以我们需要封装。

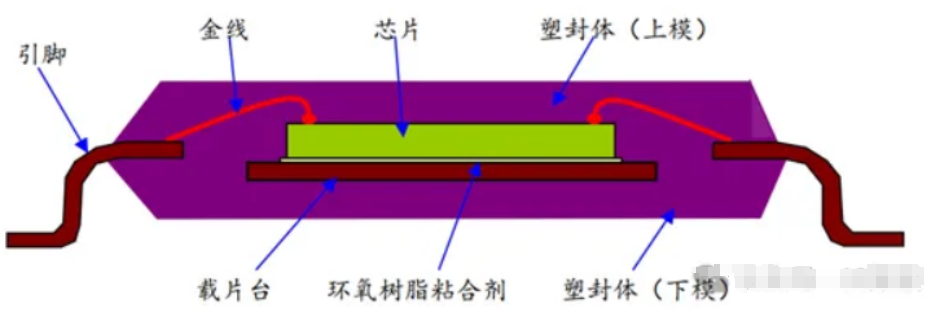

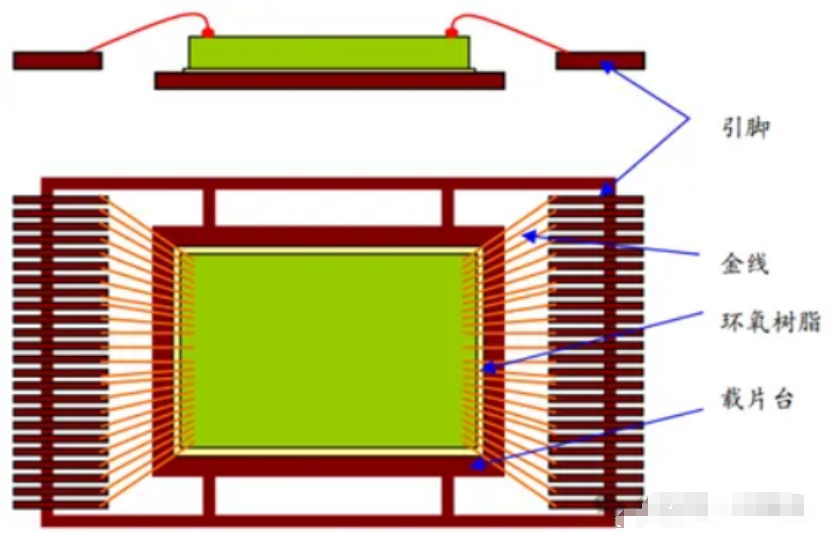

(2) 支撑:一是支撑芯片,将芯片固定好便于电路的连接,二是支撑封装完成后的器件,使得整个器件不易损坏。载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定及保护作用。

(3) 连接:将芯片的pad和外界的电路连通。如上图所示,引脚用于和外界电路连通,金线则用于引脚和芯片的电路连接。

(4) 可靠性:其实和防护有点关系,但主要是考虑一些机械压力,温度,湿度,化学腐蚀等损害,封装材料等选择会直接影响到芯片的期的可靠性,因此芯片的工作寿命,主要决于对封装材料和封装工艺的选择。

二、芯片封装技术的发展趋势

引脚数量变多,从而集成度更高,可以容纳更多芯片

封装尺寸变小、厚度变薄

芯片制造与封装工艺逐渐结合

焊盘大小、节距变得越来越小

成本越来越低且绿色环保

以下就是芯片封装技术的发展趋势:

(1) 插装时代:最早期的封装形式为引线封装,包括DIP(双列直插封装)等,这时候主要解决的问题是封装内部的绝缘以及良好的热传导性能。因此,多数封装使用了塑料、陶瓷或金属等材料,以提供一定程度的物理和环境保护。然而,由于引线封装尺寸较大,因此集成度较低。

(2)表贴时代:也就是表面贴装技术(Surface Mount Technology),主要的封装形式包括SOP(小尺寸封装),QFP(四角扁平封装)等,与早期的通孔插装技术相比,表贴时代的封装技术显著提高了封装密度,使得更多的电子元件能够集成在更小的空间内,推动了封装技术朝着更小型更高集成度的方向发展。

(3) 面阵列时代:指的是20世纪90年代以后的封装技术发展阶段,主要的封装形式包括BGA(球栅阵列封装),QFN(无引脚封装),CSP(Chip Scale Package)等,这种封装技术显著提高了封装密度和I/O引脚数量,满足了高性能芯片对封装技术的需求,并且提供了更短的信号传输路径和更好的电气性能,满足了高速、高频、高性能芯片对封装技术的要求。

(4) 基板+堆叠封装时代:是指在不改变封装体的尺寸的前提下,如2.5D TSV技术,是半导体封装技术发展的一个重要阶段,它起源于快闪存储器(NOR/NAND) 及 SDRAM 的叠层封装。为了增大单个器件的存储容量,通常的做法就是减小芯片的线宽、采用集成度更高的工艺。不过,减小线宽会使晶圆带来生产成本的上升,技术难度也会相应加大。然而,采用叠层芯片封装技术,在一个封装体内放入两个芯片就可以将单个器件的容量提高一倍,同样可以将单个器件的容量成倍提升,但是生产成本的上升、工艺难度都比前者低,这一技术结合了基板技术和堆叠封装技术的优势,进一步提高了封装密度、性能和可靠性。

(5) 扇出封装时代:通过在晶圆级别进行封装,并在封装过程中将芯片的I/O互连点布置在芯片面积区域以外的空隙中,从而实现了更高的封装密度和更多的I/O引脚数量。

三、以SOP封装技术作为封装工艺流程介绍

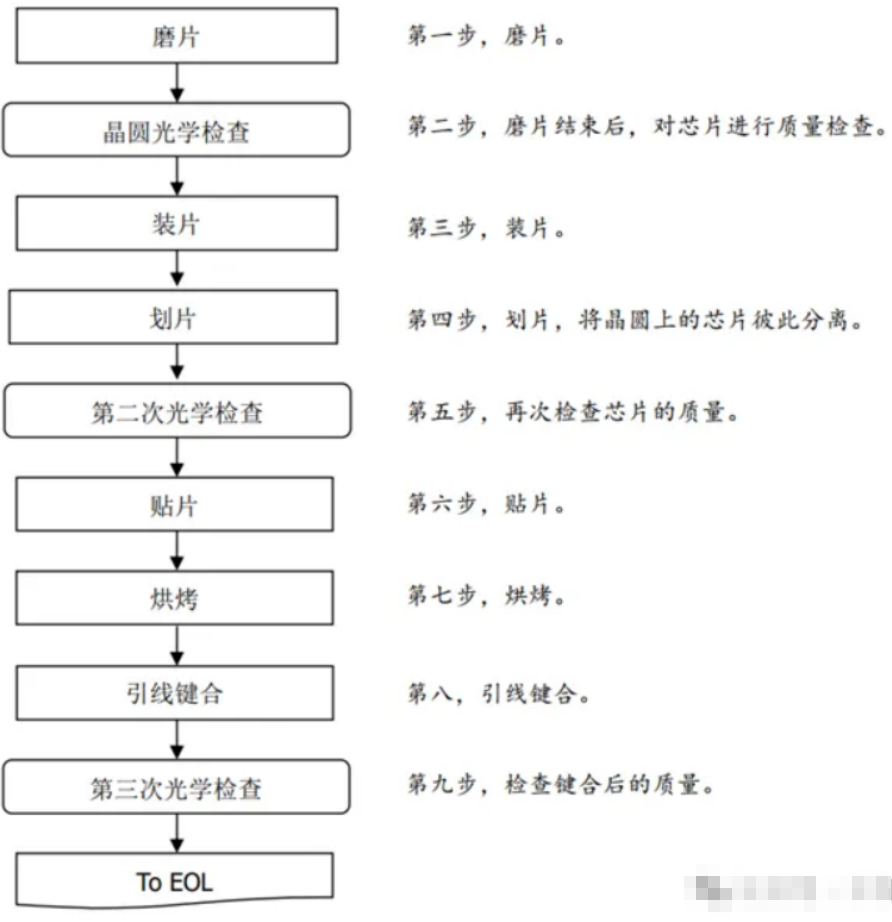

芯片封装工艺分为两段,分别叫前道(Front-of-line,FOL)和后道(End-of-line,EOL), 前道(FOL)主要是将芯片和引线框架(Leadframe)或基板(Substrate)连接起来,即完成封装体内部组装。后道(EOL)主要是完成封装并且形成指定的外形尺寸,及封装成型。

前道生产工艺

下面,用示意图来简单介绍主要的加工工艺:

1. 晶圆(wafer)

封装厂接收到一个从晶圆厂(Wafer Fab)出来的晶圆,上面布满了矩形的芯片, 有切割槽的痕迹。

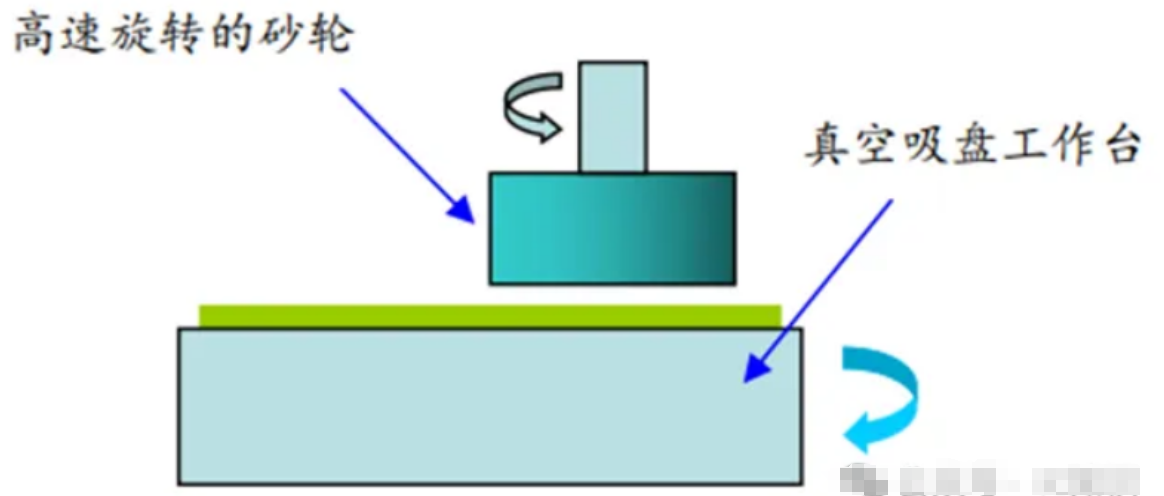

2. 磨片(Backgrinding)

晶圆出厂时,其厚度通常都在 0.7mm 左右,比封装时的需要的厚度大很多,所以需要磨片。下图就是磨片工艺示意图,晶圆被固定在高速旋转的真空吸盘工作台上,高速旋转的砂轮从背面将晶圆磨薄,将晶圆磨到指定的厚度。

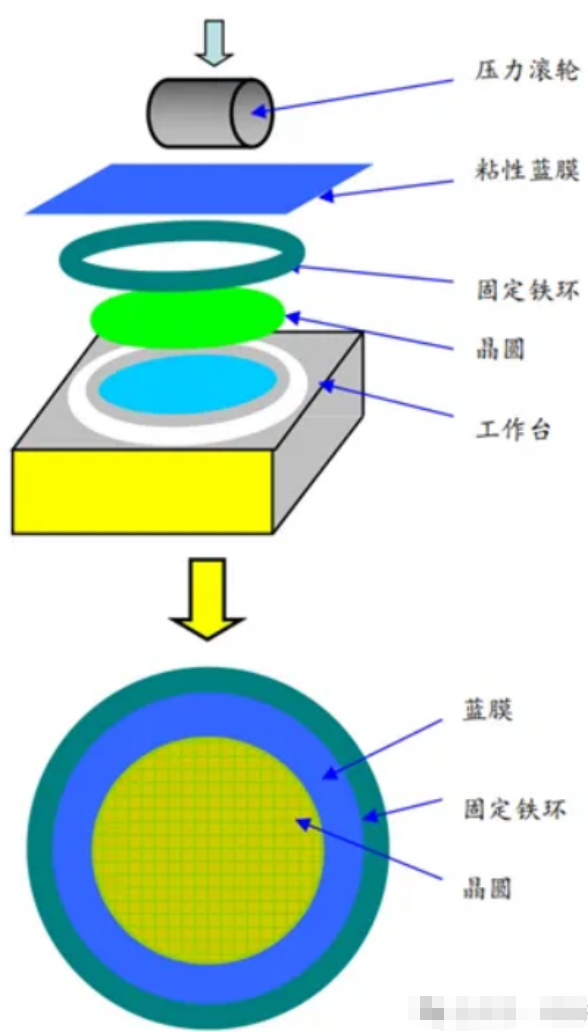

3. 装片(Wafer Mount)

下图展示了如何将晶圆粘贴到粘性蓝膜上。首先将晶圆正面朝下固定在工作台的真空吸盘上,然后铺上不锈刚晶圆固定铁环(Wafer Ring), 再在铁环上盖上粘性蓝膜(Blue Tape),最后施加压力,把蓝膜、晶圆和铁环粘合在一起。中央的晶圆被固定在蓝膜上,蓝膜被固定在不锈钢铁环上,以便后续工序加工。

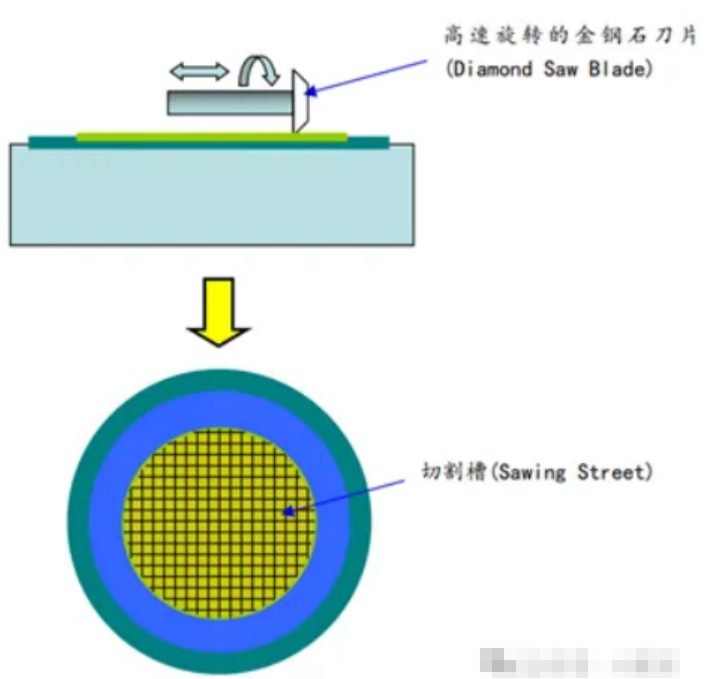

4. 划片(Die Sawing)

高速旋转的金刚石刀片在切割槽中来回移动,将芯片分离。下图是完成切割的晶圆,芯片被沿着切割槽切开。

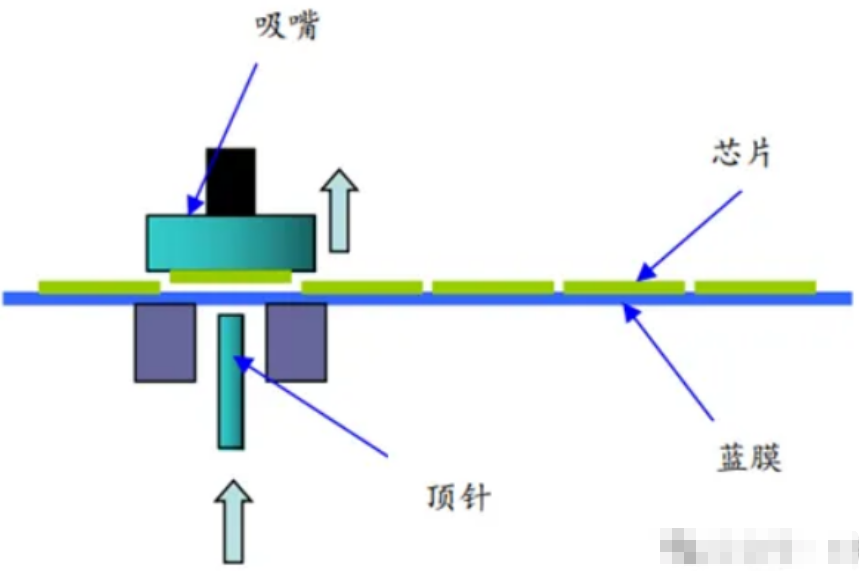

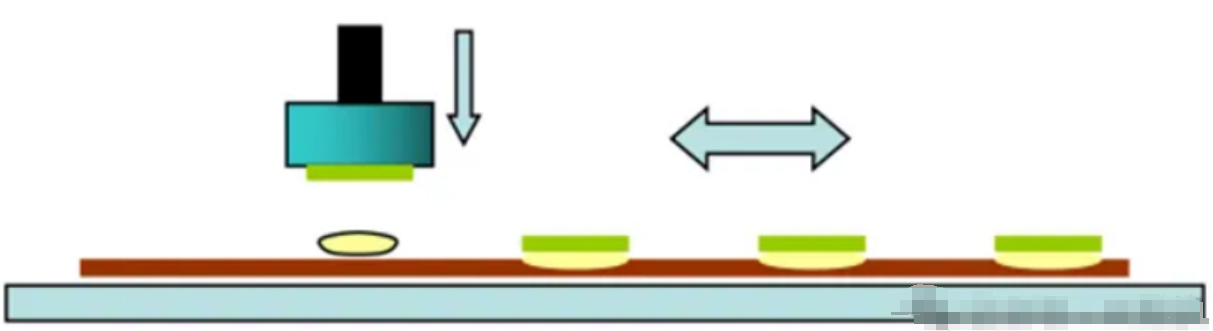

5. 贴片(Die Attach)

第一步:顶针从蓝膜下面将芯片往上顶、同时真空吸嘴将芯片往上吸,将芯片与膜蓝脱离。

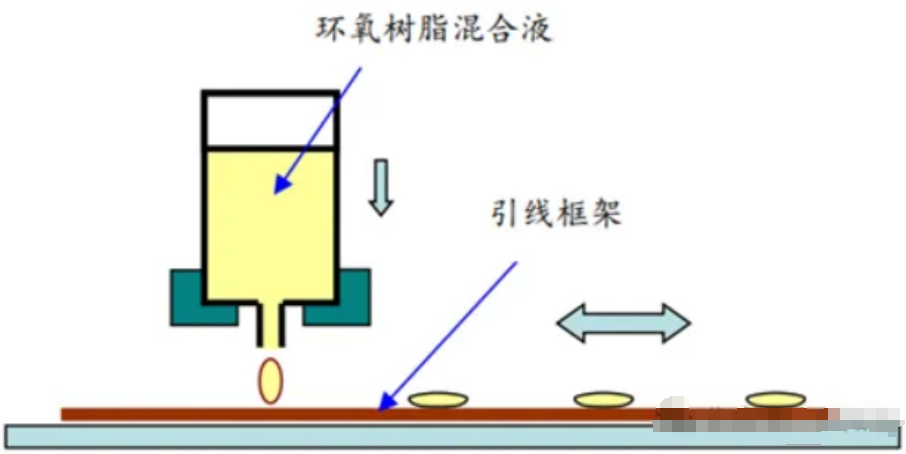

第二步:将液态环氧树脂涂到引线框架的台载片台上

第三步:将芯片粘贴到涂好环氧树脂的引线框架上

6. 引线键合(Wire Bonding)

是用金线将引线框架的引脚和芯片的焊盘连接起来,上图是截面图,下图俯视图

后段生产工艺

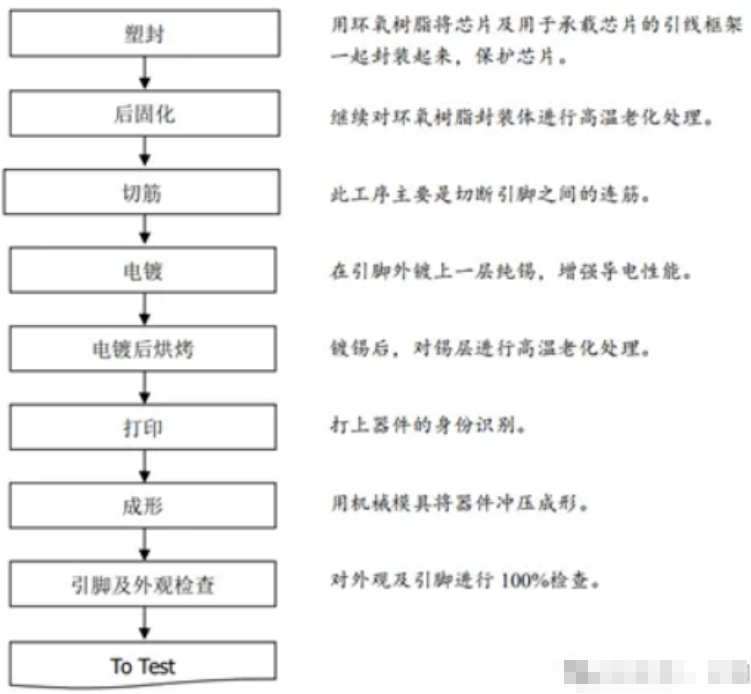

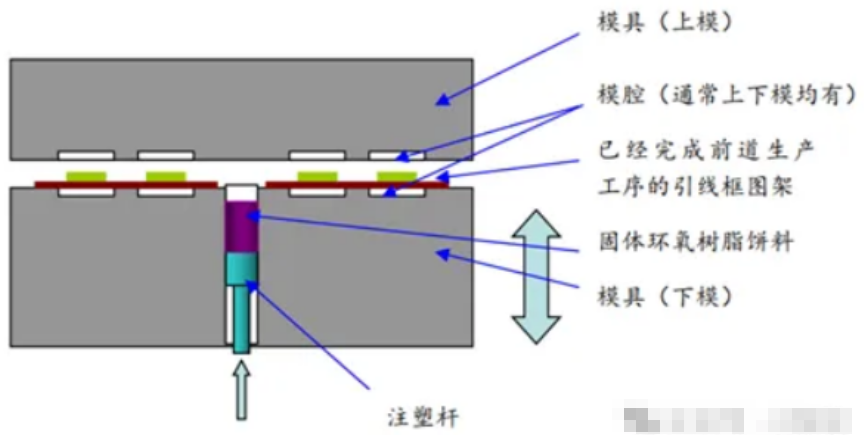

1. 塑封(Molding)

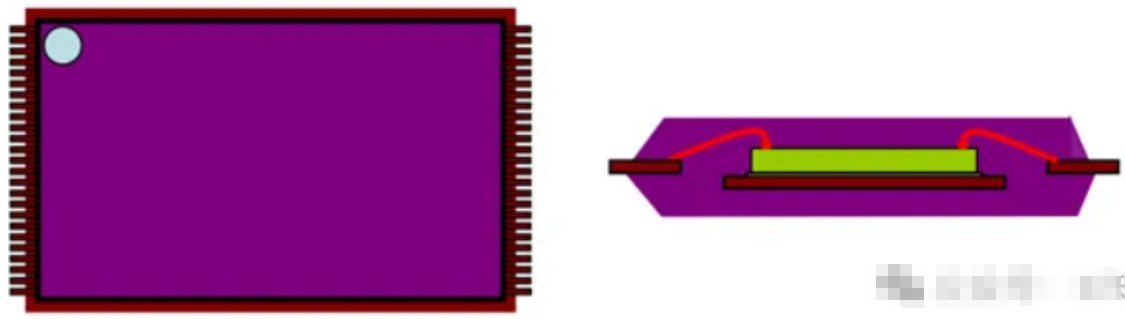

塑封是用环氧树脂将芯片及用于承载芯片的引线框架一起封装起来,保护芯片,并形成一定等级的的可靠性。具体模具分成上下模,模具上有根据封装体尺寸所预先定好的模腔,其工作温度在通常在 165-185℃范围内。将需要封装的引线框架放置到模具上,然后放入固体环氧树脂饼料,再合上模具并施加合模压力(至少在 30 吨以上)。合模后,给注塑杆上施加压力,环氧树脂在高度高压下开始液化然后在被挤入腔中后,它将再次固化,形成我们所需要的外形尺寸。上图是塑封过程,下图是塑封后的俯视图和截面图

2. 切筋(Trim)

对比塑封后的图我们可以发现,切筋后引脚之间的连筋已经没有了。切筋的作用是将引脚之间的连筋切开,以方便成形工艺。

3. 电镀(Plating)可以发现,相比切筋后,引脚之间的颜色有了变化。电镀的作用是增强导电性能。

4. 成形(Form)引脚的外形是由冲压模具来完成,器件被固定在模具上,刀具从上下冲压成形,然后将器件与引线框架分离,成形工艺是半导体封装的最后一步,其外形尺寸有严格的行业标准, TSOP 封装的总高度不得超过 1.27mm、 引脚节距 0.5mm,塑封体厚度为 1.0mm

6739

6739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?