1、问题现象

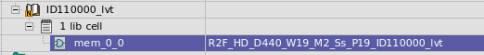

NNA集成TSMC_N7 Macro memory进行Top Level仿真,仿真结果错误,经分析为dpstore读取的数据为X状态,具体dpstore如下图所示。

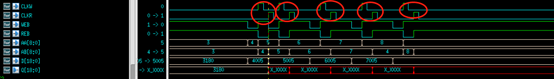

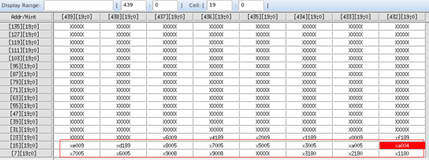

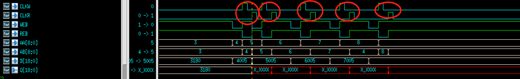

仿真波形如下图所示,Q为读数据,读取地址4至8的数据为X状态。导致整个NNA Top Level仿真失败。

2、原因分析

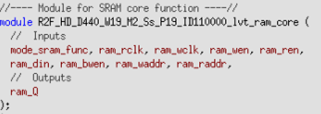

首先分析数据是否正确写入memory, 按代码查找到memory读写数据的主要模块如下图,

写数据的主要代码如下:

将memory写入的数据通过工具展示出来,具体如下图所示,证明memory中存在数据,与仿真波形吻合,说明数据已经正确的写入,存储在memory中。

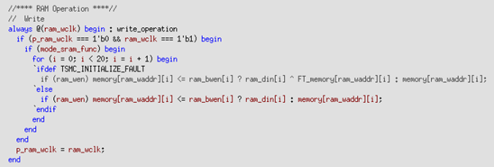

在对读取的数据Q进行波形分析的时候,发现数据可以正确的读取,但只持续了5ps后变为X状态,说明数据可以正确地被读取,5ps后被改变了,读数据的代码如下图所示,未发现明显问题。到这一步,因为读写程序都没问题,貌似查找问题的路径中断了。

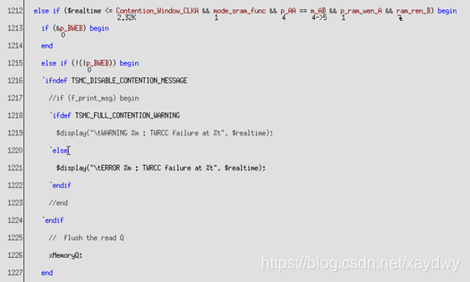

开始怀疑,是不是有其他地方对memory的读取端口数据进行了更改,根据读数据接口关键字ram_Q在代码中进行查找。发现程序中存在很多task对ram_Q进行了赋值,如下图所示(只截取一部分):

这么多task对ram_Q进行了赋值,到底是哪个task在该时候发生作用了呢,由于task有打印信息,寻找打印信息,根据打印信息找到task xMemoryQ改变了读取数据。打印信息如下:

![]()

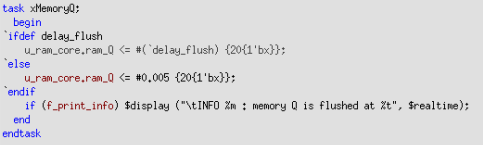

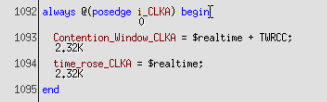

task xMemoryQ的代码如下:

根据打印信息 TWRCC failure at, 找到该代码具体位置,如下图:

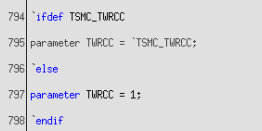

结合波形,分析上述代码产生的条件。由于TSMC_TWRCC宏定义并未定义,所以TWRCC采用参数值为1。

则,变量Contention_Window_CLKA=$realtime + 1,该变量的意思是,数据写入memory在i_CLKA上升沿后TWRCC才能正确被读取,负责读取的数据为X态。

再结合波形分析,发现读数据晚于写数据一个时钟周期,由于我们的时间单位采用的是1ns,参数TWRCC=1也就是1ns的意思,则在读数据的时候$realtime=Contention_Window_CLKA,则上述的条件成立,进入task xMemoryQ执行,结合xMemoryQ的描述,ram_Q在延迟5ps后被赋值为X。

从上述的分析可以得知,TWRCC是同一个地址写数据到读数据的最短时间间隔,如果小于该时间间隔,则读取的数据不稳定,否则,则数据正常。但在仿真问题出现之前,我们并不知道TSMC dpstore有这一点特性。编译工具生成的dpstore memory默认值TWRCC=1,则代表该memory model能运行的最高时钟频率不超过1GHz。而我们运行的时间单位为1ns,正好是1GHz,导致出现该现象。

3、解决方法

通过分析我们可以知道,解决该问题有两种方法:

<1>、定义一个宏定义文件,改变TWRCC的值;

<2>、更改NNA顶层的时钟单位,使其频率小于1GHz。

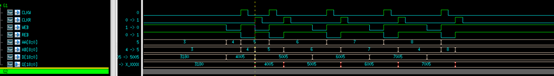

由于APU在实际应用时,采用的频率小于1GHz,所以我选择了采用降低时钟频率的方法进行解决,我将时钟频率改为800MHz,仿真的波形如下图,可以正常的读取数据,且数据符合预期。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?