Altium Designer原理图模块化,AD软件原理图模块化

Altium Designer模块化布线,AD软件模块化布线

Altium Designer模块化丝印命名,AD软件模块化丝印命名,

Altium Designer模块化元件命名格式,AD软件模块化元件命名格式。Multi-Channel指示器格式

Altium Designer多通道,AD软件多通道设计

Altium Designer里相同的原理图模块,可以使用多通道设计,实现模块化布局。如下图:

然后生成PCB图如下:

这时候会发现一个问题。PCB里面的元件丝印的命名,太长了。C16_NAMEA表示NAMEA模块里面的零件,C16_NAMEB表示NAMEB模块里面的零件。这种命名,真不好。

解决方法:

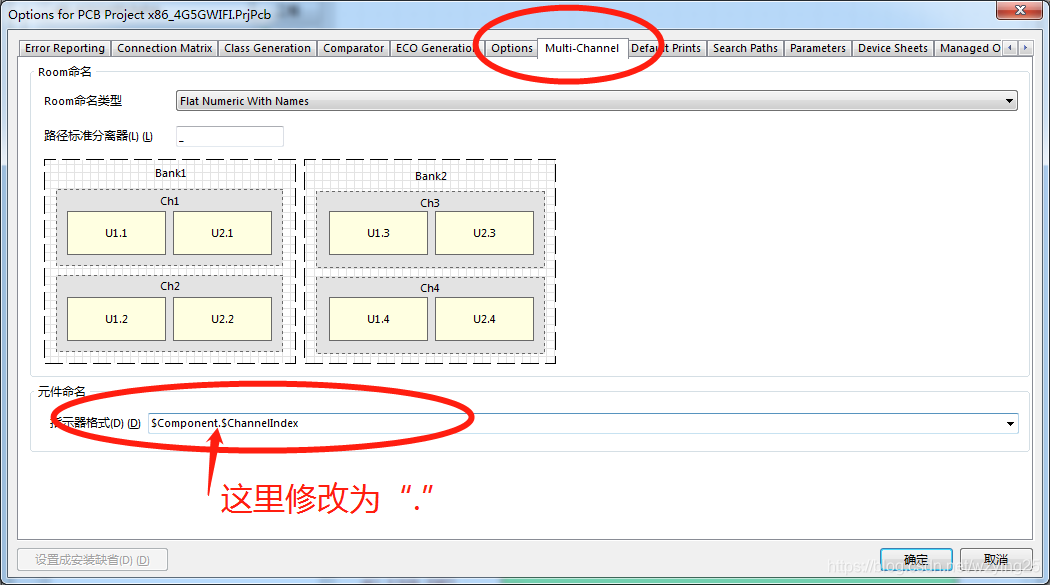

右键工程 -> 选择“工程参数” -> 选择“Multi-Channel” 。元件命名,指示器格式,选择$Component.$ChannelIndex 。

保存工程,更新PCB后,元件丝印格式为C16.1 、 C16.2 ,这样名字短了很多。,如下图:

本文介绍了如何在Altium Designer中进行模块化设计,包括原理图模块化、布线和元件命名。针对多通道设计中元件丝印命名过长的问题,提出了通过设置'Multi-Channel'的元件命名和指示器格式来简化命名的方法,例如使用$Component.$ChannelIndex。此外,还提到了使用Repeat功能快速复制相同模块的功能。

本文介绍了如何在Altium Designer中进行模块化设计,包括原理图模块化、布线和元件命名。针对多通道设计中元件丝印命名过长的问题,提出了通过设置'Multi-Channel'的元件命名和指示器格式来简化命名的方法,例如使用$Component.$ChannelIndex。此外,还提到了使用Repeat功能快速复制相同模块的功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

955

955

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?