引言

在现代计算与通信设备中,DDR内存的稳定运行至关重要,而一个高性能的终端电源是确保内存总线信号完整性的关键之一。本文将以TPS51260为例,介绍灌/拉电流终端稳压器的工作原理、核心特性和硬件设计参考。

TPS51206芯片简介

芯片主要特性

TPS51206是一款适用于DDR2、DDR3、DDR3L和DDR4,且具有VTTREF缓冲基准的,2A峰值灌电流/拉电流DDR终端稳压器。

- 电源输入电压:支持 3.3V 和 5V 电源轨

- VLDOIN 输入电压范围:VTT+0.4V 至 3.5V

- VTT 端接稳压器

- 输出电压范围:0.5V 至 0.9V

- 2A 峰值灌电流和拉电流

- 仅需 10μF 的多层陶瓷电容 (MLCC) 输出电容

- ±20mV 精度

- VTTREF 缓冲参考输出

- VDDQ/2 ± 1% 精度

- 10mA 灌/拉电流

- 支持高阻态(S3 状态)和软停止(S4 和 S5 状 态),通过 S3 和 S5 输入选择

- 过热保护

- 10 引脚 2mm × 2mm 小外形尺寸无引线 (SON) (DSQ) 封装

(以上参考自芯片规格书)

芯片引脚定义

| 引脚 | 定义 | I/O方向 | 说明 |

| 1 | VDDQSNS | I | VDDQ sense input, reference input for VTTREF |

| 2 | VLDOIN | I | Power supply input for VTT/ VTTREF |

| 3 | VTT | O | Power output for VTT LDO, need to connect 10-μF or greater MLCC for stability. No maximum limit for VTT output capacitance |

| 4 | PGND | - | Power GND for VTT LDO |

| 5 | VTTSNS | I | VTT LDO voltage sense input |

| 6 | VTTREF | O | VTTREF buffered reference output. Connect to MLCC between 0.22-µF and 1-µF for stability. The VTTREF pin can not be open |

| 7 | S3 | I | S3 signal input |

| 8 | GND | - | Signal ground |

| 9 | S5 | I | S5 signal input |

| 10 | VDD | - | Device power supply input (3.3 V or 5 V) |

(以上参考自芯片规格书)

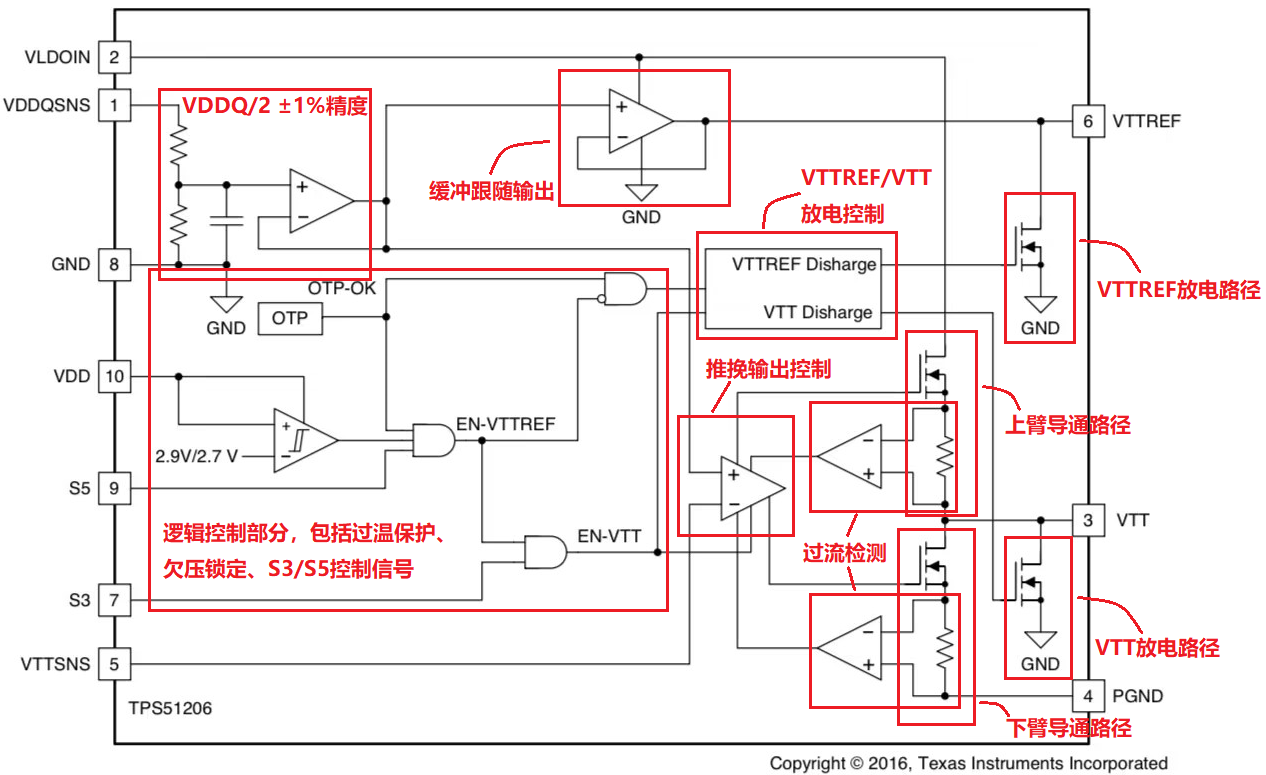

芯片功能框图

芯片工作状态控制

通过S3和S5两个控制引脚,TPS51206能够无缝对接现代系统的电源管理状态。

- S3状态:当S3为高电平时,VTT输出进入高阻态(High-Z),内部的上下功率管均关闭,输出端与芯片内部电路断开,既不拉电流也不灌电流,同时保持VTTREF输出。此时内存数据被保持。

- S4/S5状态:当S3和S5均为低电平时,芯片进入S4/S5状态,VTT和VTTREF输出均被关闭并内部放电至GND。这实现了系统的快速、安全关机。

| STATE | S3 | S5 | VTTREF | VTT |

| S0 | HI | HI | ON | ON |

| S3 | LO | HI | ON | OFF(High-Z) |

| S4 and S5 | LO | LO | OFF(discharge) | OFF(discharge) |

(以上参考自芯片规格书)

上下电时序

建议的上电顺序为:先开启VDD、S3和S5,再开启VLDOIN和VDDQSNS。掉电顺序则相反。

(以上参考自芯片规格书)

核心工作原理:灌电流与拉电流的实现

工作原理:TPS51206的VTT输出级本质上是一个双向、高精度的运算放大器,其同相输入端接入一个精准的参考电压(0.5*VDDQSNS),输出级采用推挽结构的功率管。

- 拉电流:当内存总线信号从低电平变为高电平时,总线需要从VTT电源“吸取”电流来充电。此时,TPS51206内部的上臂MOS功率管导通,将电流从VLDOIN源出,通过VTT引脚输送到总线上,表现为 “拉电流”。

- 灌电流:当内存总线信号从高电平变为低电平时,总线上的电荷需要被泄放至地。此时,TPS51206内部的下臂MOS功率管导通,形成一条低阻抗路径,将总线上的电流通过VTT引脚“吸入”,再导向GND,表现为 “灌电流”。

这种独特的推挽结构使得TPS51206能够像一个“智能双向电源”一样工作,无论总线需要电流还是泄放电流,都能迅速响应,确保VTT电压始终精准地跟踪在0.5*VDDQSNS,维持总线信号的完整性。

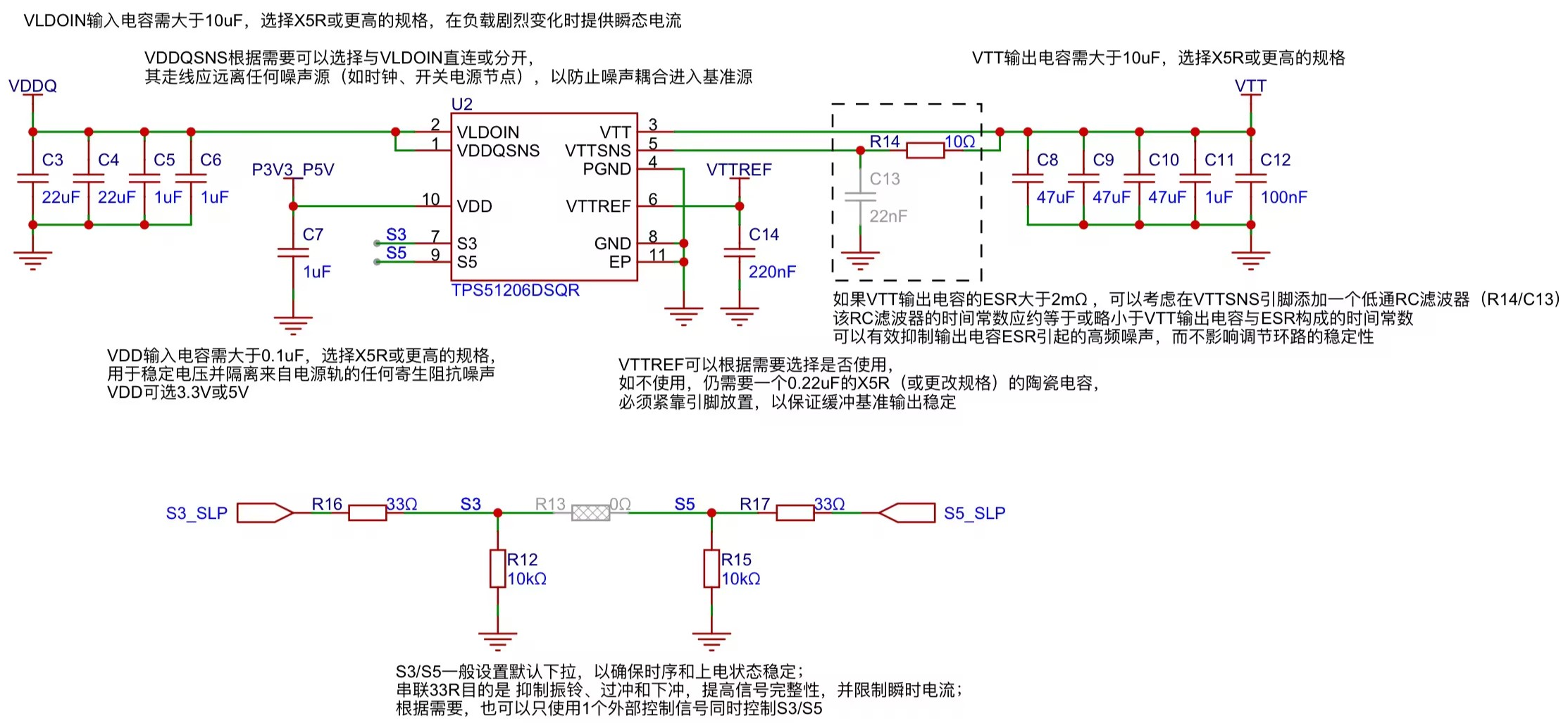

硬件设计参考原理图

设计要点与注意事项

1. 功耗计算与热管理:

- 作为线性稳压器,其功耗为 P_LOSS = (VLDOIN-VTT) * I_VTT。例如,当 VLDOIN = 1.2V、VTT = 0.6V、I_VTT =2A 时,功耗为1.2W。这是一个相当大的热功耗。

- 设计要点:必须严格按照数据手册要求,优化芯片底部的散热焊盘设计。建议使用多个过孔将散热焊盘连接到PCB的大面积接地铜皮上,以提供有效的散热路径。

2. 电源状态控制引脚的处理:

- S3和S5是数字信号输入引脚,如果它们由长走线连接或来自可插拔的连接器,建议增加上下拉电阻(一般建议默认下拉)并在引脚附近添加一个小电容(如10pF~100nF)进行滤波,以防止噪声引起意外的状态切换。

3. PCB Layout

- VLDOIN 输入电容应尽可能靠近引脚放置,并采用短而宽的连接。

- VTT 输出电容应靠近引脚(VTT 和 PGND)放置,并采用短而宽的连接,避免引入额外的ESR和ESL。

- VTTSNS 必须从VTT输出电容的正极单独引出一条走线连接到VTTSNS引脚,严禁与VTT大电流电源走线共享。建议将此反馈走线布置在独立的PCB层,并远离其他大电流走线和其他噪声源。

- VDDQSNS是VTTREF和VTT的参考电压输入。其走线应远离任何噪声源(如时钟、开关电源节点),以防止噪声耦合进入基准源,导致VTT和VTTREF输出电压产生抖动。

- GND 引脚(以及 VTTREF 输出电容的负极)和 PGND 引脚(以及 VTT 输出电容的负极)应通过多个过孔连接到内部系统接地平面(为达到更好效果,建议使用至少两个内部接地平面)。尽可能多地使用过孔,以降低 GND 引脚或 PGND 引脚与系统接地平面之间的阻抗。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?