跟着野火的视频学习了一下全加器的实现~

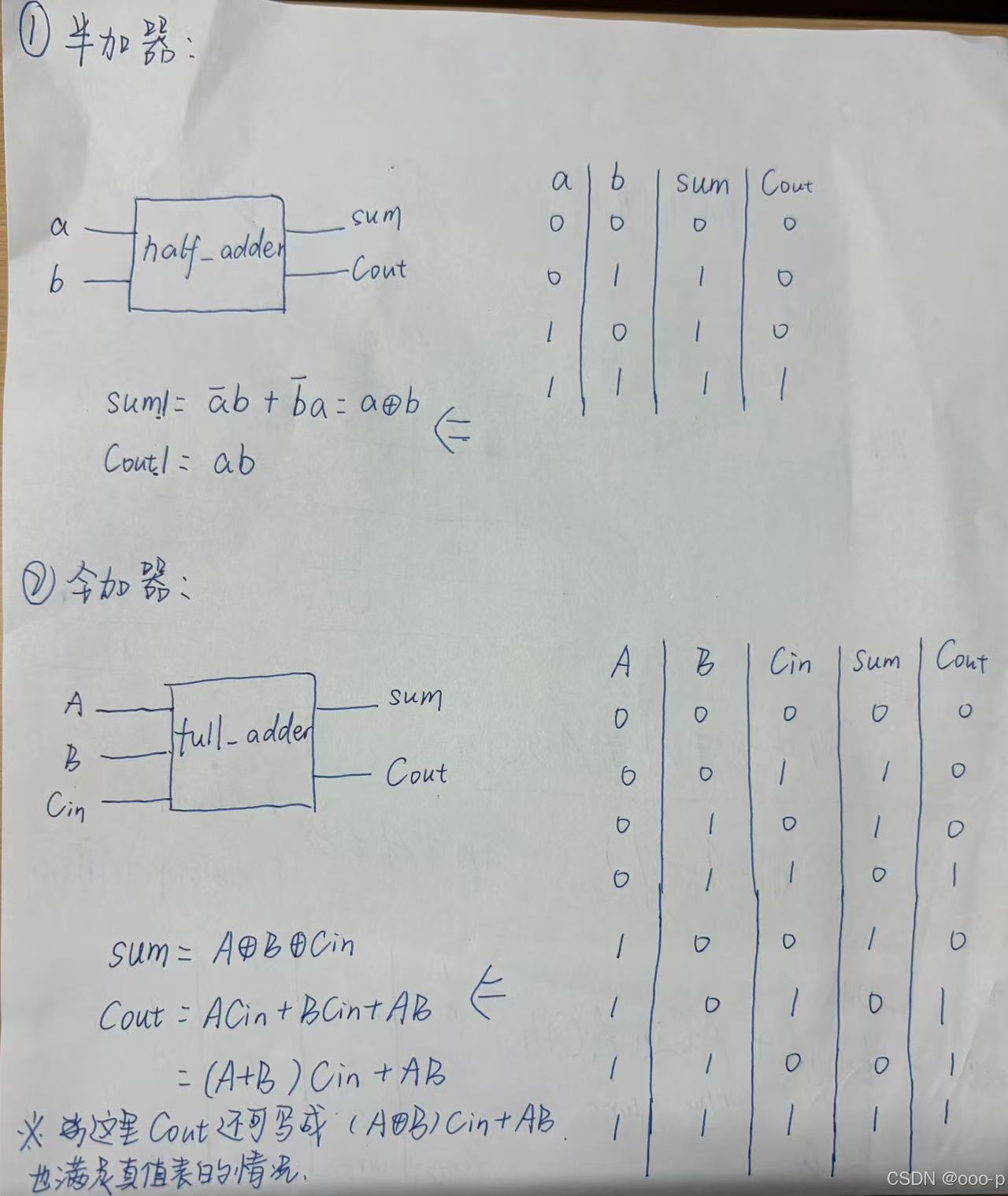

1 半加器和全加器原理

首先,解释一下为什么全加器的 公式还可以写成以下形式:

(1)首先我们要明白:

因为由真值表来看,他们是不相同的(当a=b=1时)

| a | b | a+b (OR) | a⊕b (XOR) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

(2)但在这里为什么能进行替换呢?

其中, 这一项是通过上图中真值表的第四行和第六行得来的,这两行,AB的值只有其中一个为1的情况,而这种情况下,

和

在真值表中是一样的(上表中黄色两行),因此就可以进行替换。

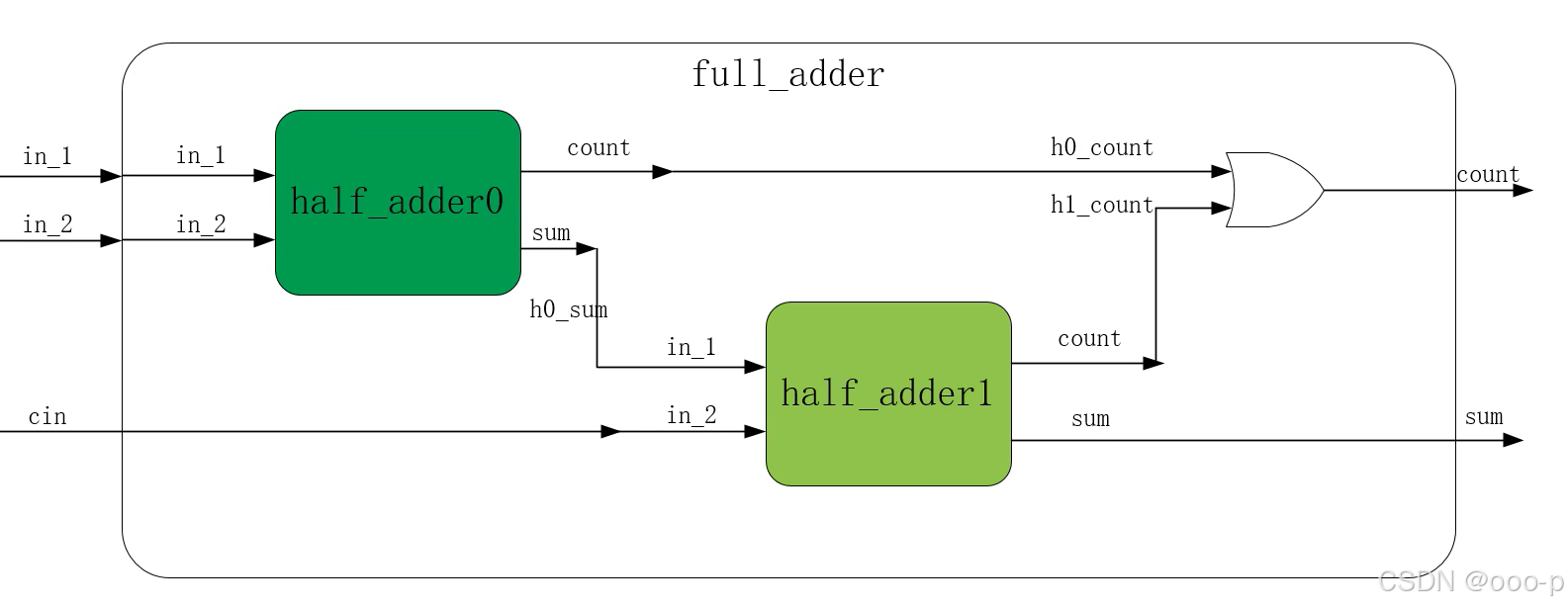

2 实现半加器到全加器

(借用野火老师的图~)

两个半加器加一个或门用以上方式就能得到一个全加器。

其实可以用公式推导得来:

全加器的输出很容易理解,就是

信号一起作为输入,那么将第一个半加器的

(=AB)连接到第二个半加器作为其中一个输入,

直接作为第二个半加器的另一个输入即可。

全加器的 由公式可知,AB可由第一个半加器的

得到,而

这一项中可变成

,前面我们提到了将第一个半加器的

(=AB)连接到第二个半加器作为其中一个输入,那么第二个半加器的

,则将

和

通过或门相连就恰好是 全加器

的公式。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?