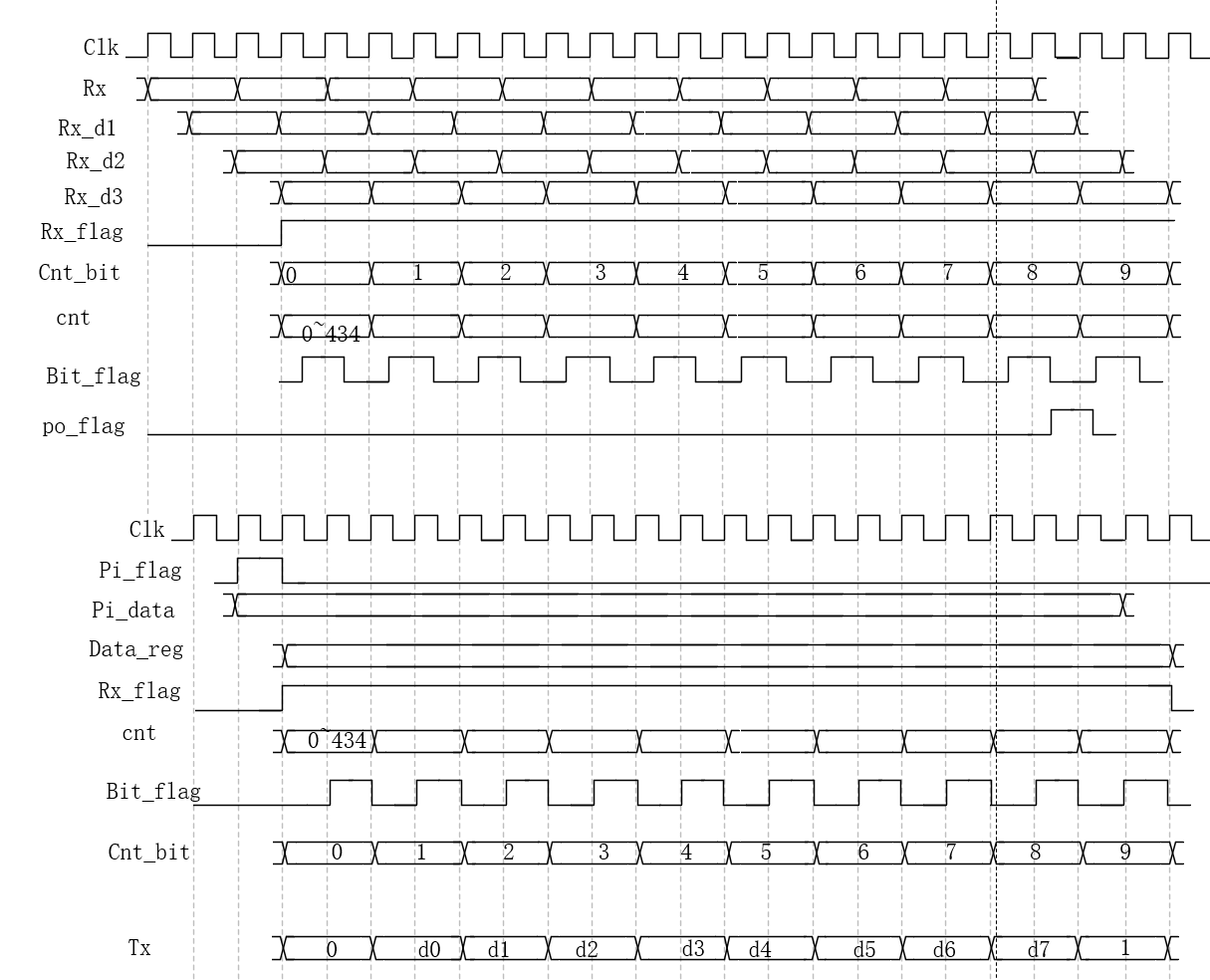

本文是本人经过学习uart后再自己独立不参考任何资料,自己独自写的代码,其主要目的就是想让自己习惯这种自己来设计代码过程,刚开始是比较慢的,但是我相信不断地重复这些,慢慢都会熟悉的。一下是我当时的一些时序图和代码的部分,有问题的读者可以私聊我交流讨论。非常感谢!!!

rx

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : tang 207993041@gmail.com

// File : uart_rx.v

// Create : 2023-03-13 16:48:51

// Revise : 2023-03-13 16:48:51

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

module uart_rx(

input wire clk,

input wire rst_n,

input wire rx,

output reg po_flag,

output reg [7:0] po_data

);

parameter CNT_MAX=433;

reg rx_1,rx_2,rx_reg;

reg rx_flag;

reg [3:0] cnt_bit;

reg [8:0] cnt;

reg bit_flag;

always @(posedge clk ) begin

{rx_reg,rx_2,rx_1}<={rx_2,rx_1,rx};

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

rx_flag<= 1'b0;

end

else if(cnt_bit=='d8 && bit_flag==1'b1)begin

rx_flag<= 1'b0;

end

else if(rx_reg==1'b1 && rx_2==1'b0) begin

rx_flag<= 1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

cnt<= 'd0;

end

else if(cnt==CNT_MAX)begin

cnt<= 'd0;

end

else if(rx_flag==1'b1) begin

cnt <= cnt + 1'b1;

end

else begin

cnt<= 'd0;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

bit_flag<= 'd0;

end

else if(cnt==CNT_MAX/2) begin

bit_flag<=1'b1;

end

else begin

bit_flag<= 1'b0;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

cnt_bit<= 'd0;

end

else if(cnt_bit=='d8 && bit_flag==1'b1)begin

cnt_bit<= 'd0;

end

else if(bit_flag==1'b1) begin

cnt_bit<= cnt_bit+1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

po_data<= 'd0;

end

else if(bit_flag==1'b1 && cnt_bit>=1 && cnt_bit<='d8) begin

po_data<={rx_reg,po_data[7:1]};

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

po_flag<= 1'b0;

end

else if(bit_flag==1'b1 && cnt_bit=='d8) begin

po_flag<= 1'b1;

end

else begin

po_flag<= 1'b0;

end

end

endmodule

tx

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : tang 207993041@gmail.com

// File : uart_tx.v

// Create : 2023-03-13 16:50:11

// Revise : 2023-03-13 16:50:11

// Editor : sublime text3, tab size (2)

// -----------------------------------------------------------------------------

`timescale 1ns / 1ps

module uart_tx(

input wire clk,

input wire rst_n,

input wire [7:0] pi_data,

input wire pi_flag,

output reg tx

);

parameter CNT_MAX=433;

reg tx_flag;

reg [8:0] cnt;

reg bit_flag;

reg [3:0] cnt_bit;

reg [7:0] data_reg;

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

data_reg<= 'd0;

end

else if(pi_flag==1'b1) begin

data_reg<=pi_data;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

tx_flag<= 'd0;

end

else if(pi_flag==1'b1) begin

tx_flag<=1'b1;

end

else if(bit_flag==1'b1 && cnt_bit=='d8)begin

tx_flag<=1'b0;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

cnt<= 'd0;

end

else if(cnt==CNT_MAX)begin

cnt<= 'd0;

end

else if(tx_flag==1'b1) begin

cnt<=cnt+1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

bit_flag<= 'd0;

end

else if(cnt==CNT_MAX-1) begin

bit_flag<= 1'b1;

end

else begin

bit_flag<= 'd0;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

cnt_bit<= 'd0;

end

else if(cnt_bit=='d8 && bit_flag==1'b1)begin

cnt_bit<= 'd0;

end

else if(bit_flag==1'b1) begin

cnt_bit<= cnt_bit+1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

tx<= 1'b1;

end

else if(pi_flag==1'b1) begin

tx<=0;

end

else if(bit_flag==1'b1 && cnt_bit<=7)begin

tx<=data_reg[cnt_bit];

end

else if(bit_flag==1'b1 && cnt_bit=='d8)begin

tx<= 1'b1;

end

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?