DRAM

注意,当题目问DRAM的引脚的时候,要默认DRAM使用了地址线复用技术,并且使用了行列地址技术。

之前我们介绍过RAM随机存取存储器,因为存储介质的不同RAM也具有分类:

( 1 ) (1) (1)DRAM(Dynamic Random Access Memory)芯片(动态RAM)

用处:一般用于主存

注:现在DRAM过时了,现在的主存一般使用SDRAM存储器芯片。

注:SDRAM本质还是动态随机存储器,其特性和DRAM基本一致,同样需要刷新这类操作。

Dynamic Random Access Memory 动态存储器

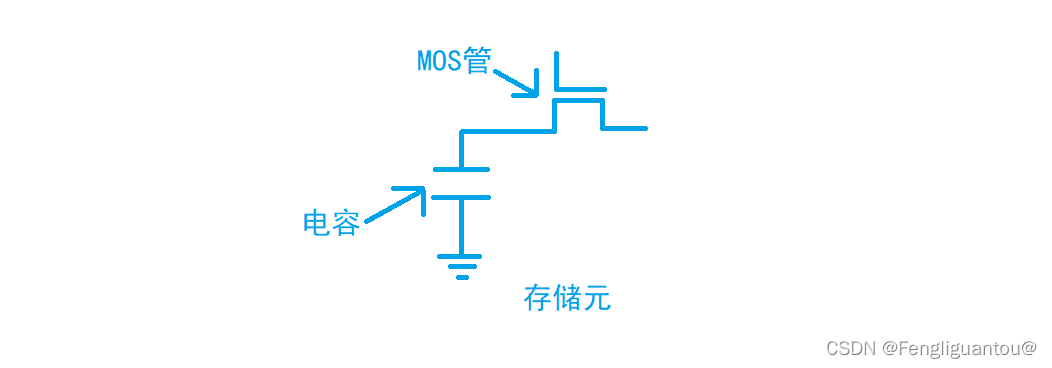

1.DRAM芯片的存储体由存储元构成。

通过存储元内的栅极电容来存储二进制的01信息。

2.每次对DRAM的读操作都会对DRAM产生破坏

DRAM存储信息是的元器件是电容,每次读信息的时候都需要导通MOS管,通过检测电容是否含有电荷来判断存储的是0信息还是1信息。电容的放电操作是对存储元的一种破坏操作,放电后电容内的电荷会流失,下次进行读操作时,就会读到错误的数据。如原本存储1信息的电容,由于上一次的放电操作导致电荷流失。最后读到的变成了二进制的0信息。所以每次读完数据信息以后,都需要对DRAM进行一次重写操作,也正是因为如此DRAM的读写速度较慢,多用于主存。

3.存储元需要按时刷新

电容中存储的电荷随着时间会逐渐流失,原本电容存储的是二进制的1信息,由于电荷的流失,电荷变成存储二进制的0信息,对于电容内的信息每次只能维持2ms,所以每2ms必须对所有的电容进行一次刷新操作,这里需要理解的更加深刻,什么是对所有的电容进行一次刷新,其实上就是对整个DRAM的存储单元里的电容都进行刷新。也就是说每2ms的周期,就需要对整个存储器芯片里的存储单元进行刷新。

DRAM的刷新操作是如何完成的?

之前,我们说过n位的地址,需要n条地址线, 2 n \color{red}{2^n} 2n条字选线。但是这就会造成一个问题,一旦地址的位数变多,那么字选线的数量就会曾爆炸增长。 所以在字选线这一存储单元检索环节,DRAM做了升级:

其将地址分成了两半,前半部分代表行地址,后半部分代表列地址。所以也就有了行地址译码器和列地址译码器,行地址译码器每次会将一整行的字选线都导通,列地址移码器每次导通一列的地质信息,两者会有一个交集,如图纸的(0,0),一个存储单元只有被行地址译码器的子选线导通并且被列地址译码器的字选线导通的时候,才能对其进行读和写。所以DRAM每次刷新可以刷新一整行,需要花费一个读写周期。并且因为行列地址的使用,原本n位的地址需要 2 n \color{red}{2^n} 2

本文详细介绍了DRAM的地址线复用技术,包括其工作原理、字选线的升级以及行列地址的使用,同时对比了与其不同性质的SRAM,强调了它们在存储器中的应用和区别。

本文详细介绍了DRAM的地址线复用技术,包括其工作原理、字选线的升级以及行列地址的使用,同时对比了与其不同性质的SRAM,强调了它们在存储器中的应用和区别。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?