计算机组成原理课后答案(唐朔飞第三版) 第3章

第4章 存储器

教材课后思考题与习题:

4.1 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory

主存:主存储器,用于存放正在执行的程序和数据。CPU可以直接进行随机读写,访问速度较高。

- RAM:(Random Access Memory),随机存取存储器,是一种可读/写存储器,一般用于计算机的主存。

- SRAM:(Static RAM),静态随机存储器

- DRAM:(Dynamic RAM),动态随机存储器

- ROM:(Read Only Memory),掩膜式半导体只读存储器

- PROM:(Programmable ROM),可编程只读存储器 -

- EPROM:(Erasable Programmable ROM),可擦写可编程只读存储器

- EEPROM:(Electrically Erasable Programmable ROM),用电可擦除可编程只读存储器

- 辅存:辅助存储器,作为主存的后备存储器,不直接与CPU交换信息,容量比主存大,速度比主存慢。

- CDROM:只读型光盘

- Cache:为解决主存和CPU的速度匹配,提高访存速度的一种存储器,设在CPU和主存之间,存放CPU近期要用的信息。

- Flash Memory:闪速存储器。或称快擦型存储器

4.2 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。

计算机中的寄存器、Cache、主存、硬盘可以用于存储信息,这个顺序:速度从高到低、容量从小到大、价格从高到低。

4.3 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?

-

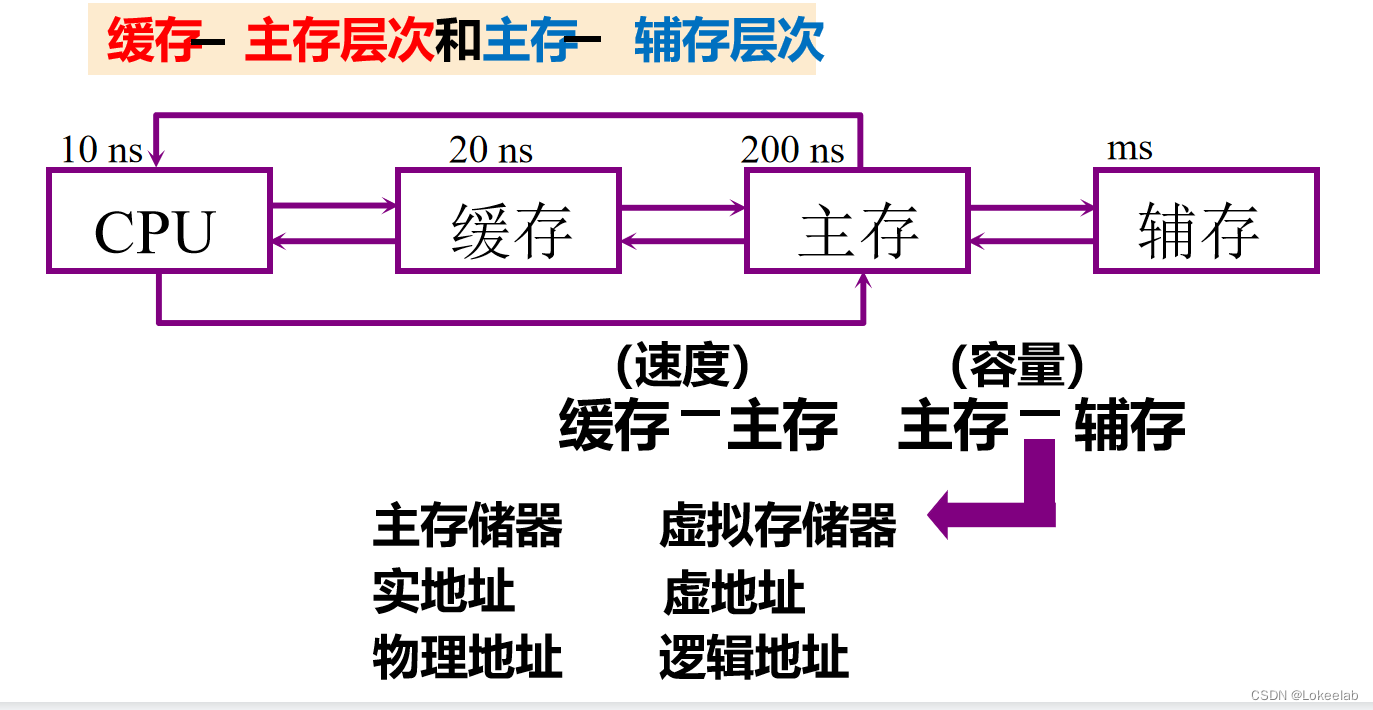

存储器的层次结构主要体现在下面两个层次上:Cache—主存、主存—辅存。

-

”Cache—主存“层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

-

”主存—辅存“层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

-

综合上述两个存储层次的作用,从整个存储系统来看,就达到了速度快、容量大、位价低的优化效果。

-

主存与Cache之间的信息调度功能全部由硬件自动完成。而主存与辅存层次的调度目前广泛采用虚拟存储技术实现,即将主存与辅存的一部分通过软硬结合的技术组成虚拟存储器,程序员可使用这个比主存实际空间(物理地址空间)大得多的虚拟地址空间(逻辑地址空间)编程,当程序运行时,再由软、硬件自动配合完成虚拟地址空间与主存实际物理空间的转换。因此,这两个层次上的调度或转换操作对于程序员来说都是透明的。

4.4 说明存取周期和存取时间的区别。

存取周期和存取时间的主要区别是:存取时间仅为完成一次操作的时间,而存取周期不仅包含操作时间,还包含操作后线路的恢复时间。即: 存取周期 = 存取时间 + 恢复时间

4.5 什么是存储器的带宽?若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少?

存储器带宽:单位时间内存储器存取的信息量,单位用:字/秒 or 字节/秒 or 位/秒

带宽计算:1/200ns ×32位 = 160M位/秒 = 20MB/秒 = 5M字/秒

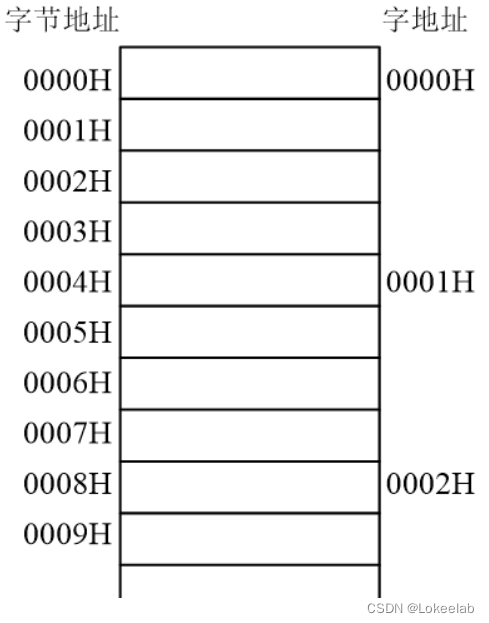

4.6 某机字长为32位,其存储容量是64KB,按字编址它的寻址范围是多少?若主存以字节编址,试画出主存字地址和字节地址的分配情况。

- 按“字”编址寻址范围:64KB /(32/8) = 16K

- 按“字节”编址寻址范围:就是64K

- 字地址与字节地址的分配情况如下图:

4.7 一个容量为16K×32位的存储器,其地址线和数据线的总和是多少?当选用下列不同规格的存储芯片时,各需要多少片?

1K×4位,2K×8位,4K×4位,16K×1位,4K×8位,8K×8位

- 地址线总数:log2(16×1024) = 14根

- 数据线总数:32根

- 1K×4位:(16K×32) / (1K×4) = 16×8 = 128片;每组8片,共16组。每次读出一个存储字,只需选中一组芯片(8片)。

- 2K×8位:(16K×32) / (2K×8) = 8×4 = 32片

- 4K×4位:(16K×32) / (4K×4) = 4×8 = 32片

- 16K×1位:(16K×32)/ (16K×1) = 1×32 = 32片

- 4K×8位:(16K×32)/ (4K×8) = 4×4 = 16片

- 8K×8位:(16K×32) / (8K×8) = 2×4 = 8片

4.8 试比较静态RAM和动态RAM。

-

静态RAM和动态RAM都属于随机存储器,即在程序的执行过程中既可读出信息又可写入信息。但静态RAM靠触发器原理存储信息,只要电源不掉电,信息就不会丢失;

-

动态RAM靠电容存储电荷原理存储信息,即使电源不掉电,由于电容要放电,信息也会丢失,故需再生。

4.9 什么叫刷新?为什么要刷新?说明刷新有几种方法。

- 动态RAM靠电容存储电荷原理存储信息,电容上的电荷要放电,信息即丢失。为了维持所存信息,需要再一定时间(2ms)内,将所存信息读出再重新写入(恢复),这一过程称为刷新,刷新是一行一行进行的,由CPU自动完成。

- 刷新方式有三种:

- 集中刷新: 即在2ms时间内,集中一段时间对存储芯片的每行刷新一遍,在这段时间里不能对存储器进行访问,即所谓的死时间。

- 分散刷新: 是将存储系统周期分为两半,前半段时间用来读/写操作,后半段时间用来刷新操作,显然整个系统的速度降低了,但分散刷新没有存储器的死时间。

- 异步刷新: 为集中刷新和分散刷新的结合。这种刷新可在2ms时间内对存储芯片的每一行刷新一遍,两行之间的刷新时间间隔为 2ms/芯片的片数。

4.10 半导体存储器芯片的译码驱动方式有几种?

- 线选法:地址信号只需经过一个方向的译码就可选中某一存储单元的所有位,适用于地址线较少的芯片。

- 重合法:适用于地址线较多的芯片。地址线分为两组,分别经过行、列两个方向译码,只有行、列两个方向均被选中的存储元才能进行读/写信息。

本文详细介绍了计算机存储系统的层次结构,包括Cache、主存、辅存的工作原理及其相互关系。讨论了存取时间、带宽等关键性能指标,以及如何通过优化存储器设计提升访问速度。此外,还涵盖了存储器的地址分配、存取周期、刷新机制等关键技术。最后,分析了动态RAM与静态RAM的区别,以及如何利用汉明码进行错误检测与校正。

本文详细介绍了计算机存储系统的层次结构,包括Cache、主存、辅存的工作原理及其相互关系。讨论了存取时间、带宽等关键性能指标,以及如何通过优化存储器设计提升访问速度。此外,还涵盖了存储器的地址分配、存取周期、刷新机制等关键技术。最后,分析了动态RAM与静态RAM的区别,以及如何利用汉明码进行错误检测与校正。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?