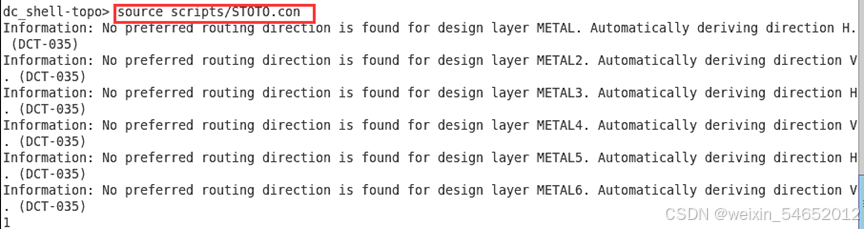

使用综合规范表中的信息编译一个名为STOTO的设计。整个实验主要围绕设计 STOTO 展开,具体来说包括了:使用 num_cores.sh 确定机器可用核心数;在 DC shell 中交互式读入、约束、编译设计;应用相关技术与命令,验证指令及属性;分析结果;利用 LayoutWindow 查看布局; Formality 等价性检查(可选)。

一.什么是STOTO

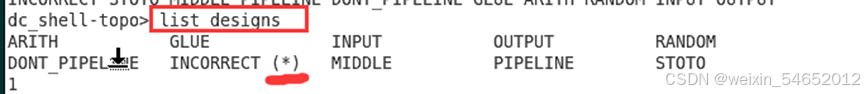

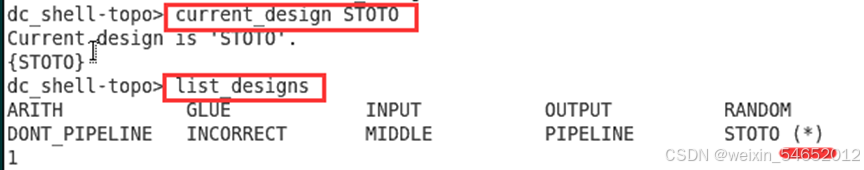

STOTO 设计包含多个模块,如 INPUT、MIDDLE、PIPELINE、DONT_PIPELINE、GLUE、ARITH、RANDOM、OUTPUT 等,通过特定的连接关系构成整体设计,这些模块之间会协同工作。例如在数据处理过程中,数据在不同模块间流动,经过一系列的逻辑操作(如 MIDDLE 模块可能涉及的逻辑处理,PIPELINE 模块中的流水线操作等),最终产生输出结果。模块之间的连接和交互方式决定了数据的流向和处理流程

在DC综合中,STOTO可作为实验对象,用于验证在复杂设计场景下,各种综合技术(如流水线优化、自适应重定时、寄存器重定时等)的实际应用效果,帮助工程师理解和掌握这些技术在实际设计中的作用和影响,以便在其他项目中合理运用。除此之外,通过分析 STOTO 设计的编译结果(如是否存在时序违规、资源使用情况、设计层次结构变化等),可以评估设计的可综合性和质量,发现潜在问题并寻找改进方向,确保设计能够满足预期的性能指标和功能要求。

二. Task

1.确定机器上可用的核心数,“指令 “./num_cores.sh”,在编译设计(如 STOTO 设计)时,能够根据实际可用核心数合理地启用多核优化。

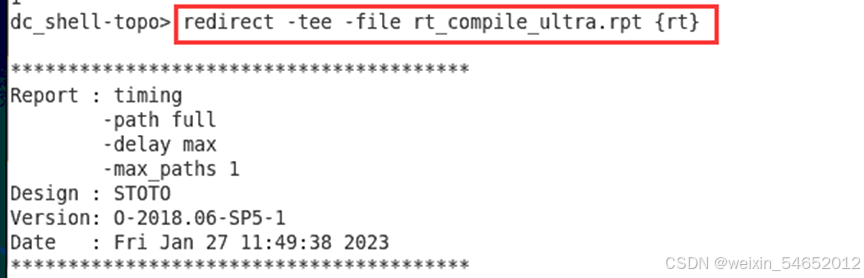

2.以拓扑模式调用 DC shell,创建 dc.tel 文件用于记录命令。

3.在读取设计之前,创建一个SVF文件,为Formality指定一个SVF文件名。

![]()

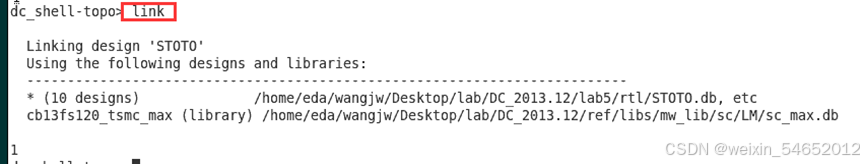

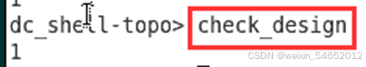

4.交互式读取、链接和检查设计 STOTO,然后获取并检查时序约束。

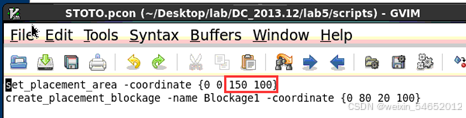

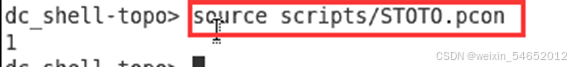

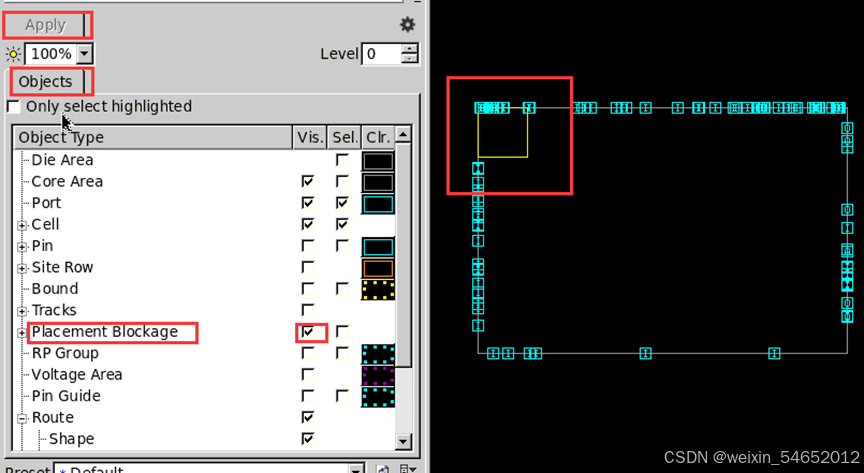

5.应用非默认物理约束,交互式应用命令(直至但不包括第一次编译),并将命令复制到 dc.tel 文件中。

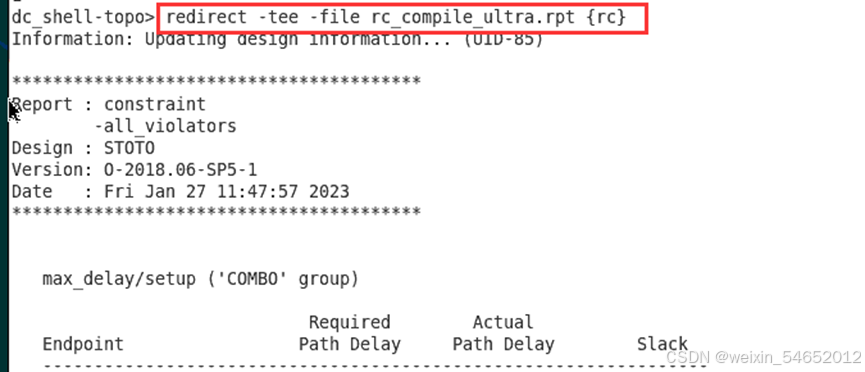

6.验证应用的指令和属性是否正确,保存未映射设计,根据可用核心数启用多核优化,确定 compile_ultra 选项,编译设计。

7.分析编译过程中的信息,如多核优化是否生效、设计是否重定时、自动解组的设计层次结构等。

8.生成约束报告和时序报告,分析是否有时序违规。

9.确定自适应重定时和寄存器重定时对寄存器的影响,根据编译结果确定下一步建议的步骤(如果有违规),并判断这些步骤是否符合设计规范。

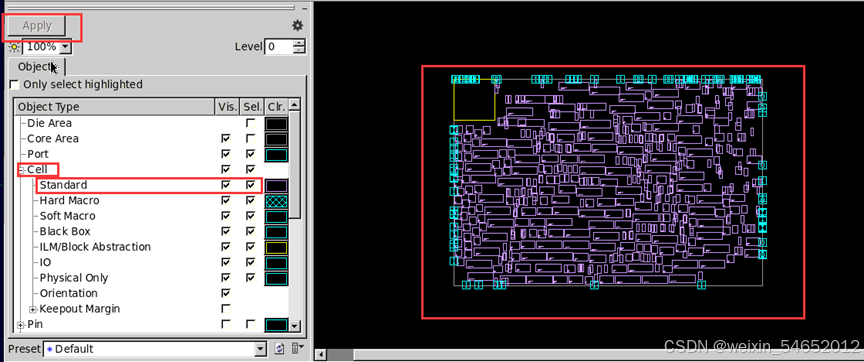

10.打开 LayoutWindow 查看布局规划和单元放置情况,检查放置区域大小和位置是否与物理约束匹配,最后退出 Design Compiler。

1065

1065

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?