modelsim一点仿真就闪退?别怪华为管家了!其实是stop/finish的原因!!

项目场景:

平时的vivado自带的仿真用得多(下文会说,用finish也不会出问题的。。。)

最近用TD需要仿真它的IP核,就只能用modelsim了。。。。。

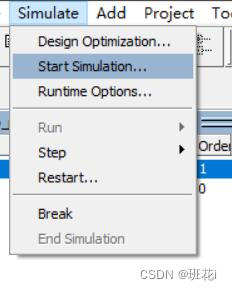

结果我在modelsim里,compile all之后,一点击start simulation就闪退。。。。

问题描述

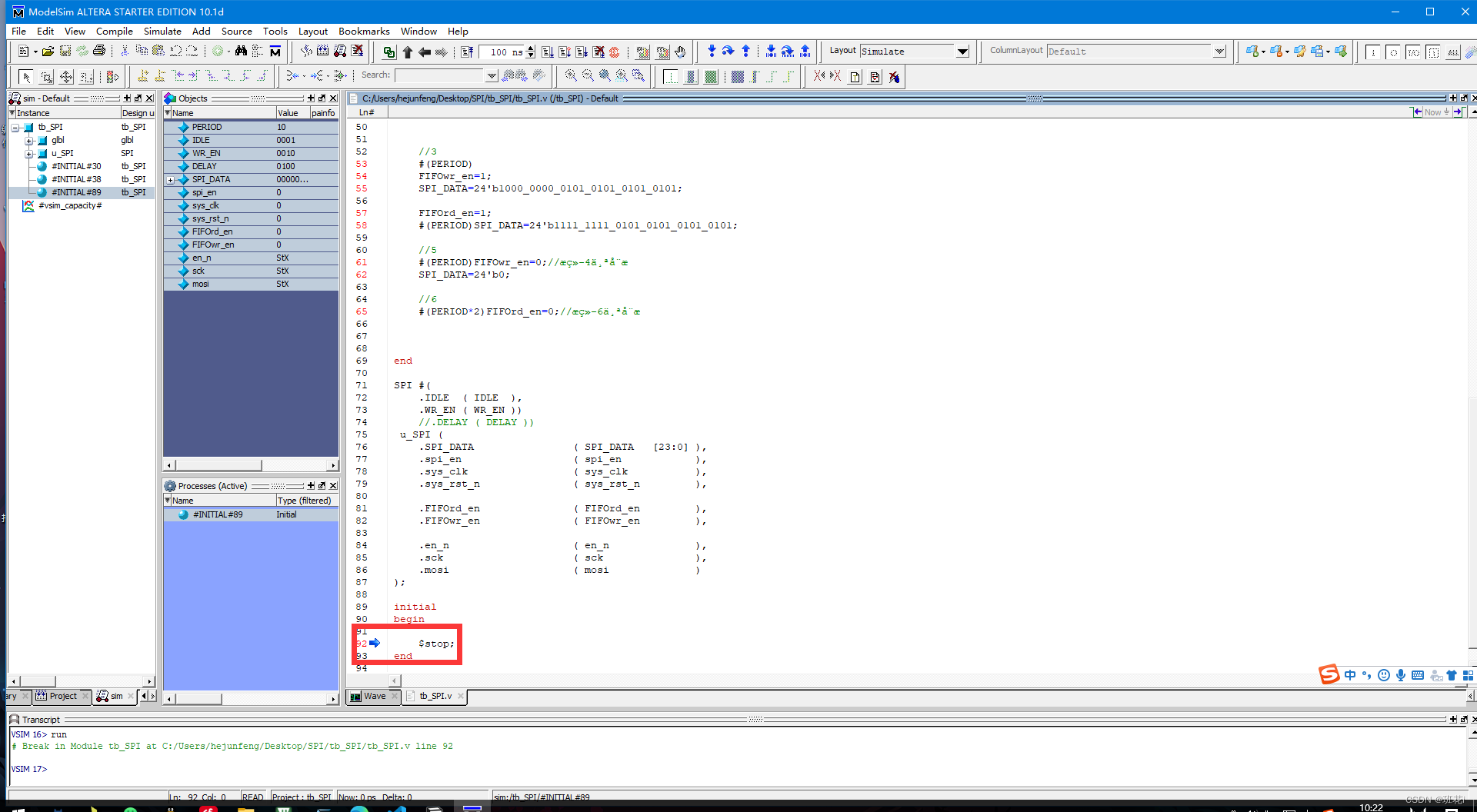

提示:一般你写testbench的时候不会去写最后这个initial语句,这是vscode的插件自动生成的模板~

注意最后的initial语句中:$finish;

//~ `New testbench

`timescale 1ns / 1ps

module tb_top1;

// top Parameters

parameter PERIOD = 10;

// top Inputs

reg clk = 0 ;

reg rst = 1 ;

reg [23:0] di = 1 ;

reg re = 0 ;

reg we = 0 ;

// top Outputs

wire [23:0] do ;

wire empty_flag ;

wire full_flag ;

glbl glbl();

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) rst = 0;

#(PERIOD*2.5);

we=1'b1;//di=24'd9;

#(PERIOD) di=24'd2;//

re=1'b1;//读使能

#(PERIOD) di=24'd3;

#(PERIOD) di=24'd4;

we=1'b0;

#(PERIOD) di=24'd0;

#(PERIOD*0.2) re=1'b0;

//#(PERIOD*0.5)

end

top u_top (

.clk ( clk ),

.rst ( rst ),

.di ( di [23:0] ),

.re ( re ),

.we ( we ),

.do ( do [23:0] ),

.empty_flag ( empty_flag ),

.full_flag ( full_flag )

);

initial

begin

$finish;

end

endmodule

尝试解决(失败)

如果你去百度or优快云搜索,有关“modelsim仿真闪退”相关的关键词,大致会得到的原因&解决方案:

华为管家,退出

安全模式

爱奇艺等启动选项(我觉得很玄学)

甚至我也责怪了我的荣耀笔记本一段时间。。。。

发现小丑竟是我自己!!!!(请继续阅读下去~)

原因分析&解决方案:

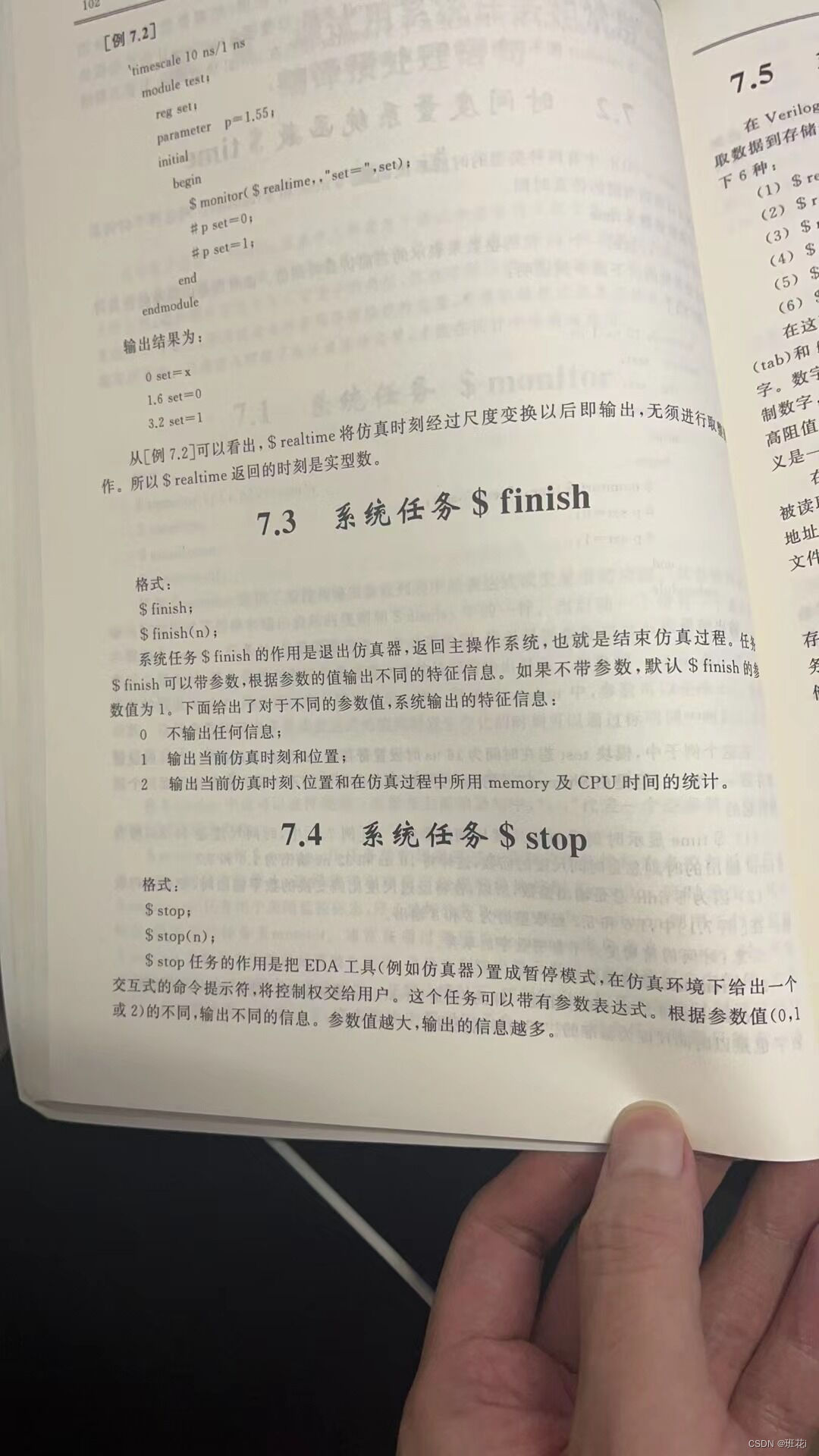

还是在于自己忽略了 $ stop和$ finish的作用。。。verilog基础不牢,地动山摇~

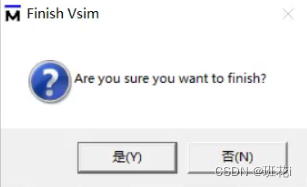

其实,从Are you sure you want to finish?; 其实也应该反应过来,啊 ,我用的是“$finish”

简单来说,

f

i

n

i

s

h

就

是

退

出

,

finish就是退出,

finish就是退出,stop就是退出

;

(其实个人建议不用 $ stop那一段话)

如果用了,你第一次点击仿真就会新打开Tb的文件,停留在$stop这个地方,确实就是“停止仿真”的意思

然后回到仿真界面,再点一次运行多少s,波形就出来了~

关于modelsim的其他帖子

我还会整理其他相关的modelsim相关的使用技巧~

(待更新)

本文揭示了ModelSim仿真闪退的真正原因——$finish命令的不当使用。通过深入分析,作者指出理解stop和finish的区别至关重要,并提供了解决方案,避免读者遇到同样的问题。

本文揭示了ModelSim仿真闪退的真正原因——$finish命令的不当使用。通过深入分析,作者指出理解stop和finish的区别至关重要,并提供了解决方案,避免读者遇到同样的问题。

1168

1168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?