前言▷▷▷

想用FPGA去控制一个器件,首先要学会阅读器件的数据手册,去了解器件的功能和使用方法。下面就来梳理一下IS42R16320D的数据手册里面本案例会用到的部分。

SDRAM时钟▷▷▷

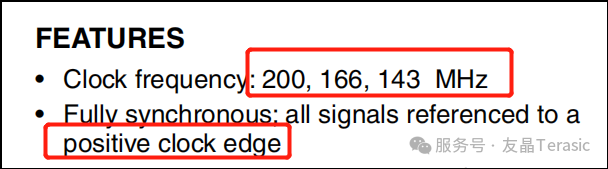

IS42R16320D时钟支持最高200M,也就是其读写速度不能超过200M,案例里面我们选择100M时钟进行读写操作。

IS42R16320D在时钟上升沿进行数据捕获。

SDRAM容量▷▷▷

DE2-115配备2片IS42S16320器件

2片* 210列* 213行* 4 bank * 16bit=2 * 32M * 16bit=2 * 64MB=128MB

DE10-Standard配备1片IS42S16320器件

210列 * 213行 * 4 bank * 16bit=32M * 16bit=64MB

DE1-SOC配备1片IS42S16320器件

210列 * 213行*4 bank * 16bit=32M * 16bit=64MB

注:16bit代表每个存储单元位宽是16bit。

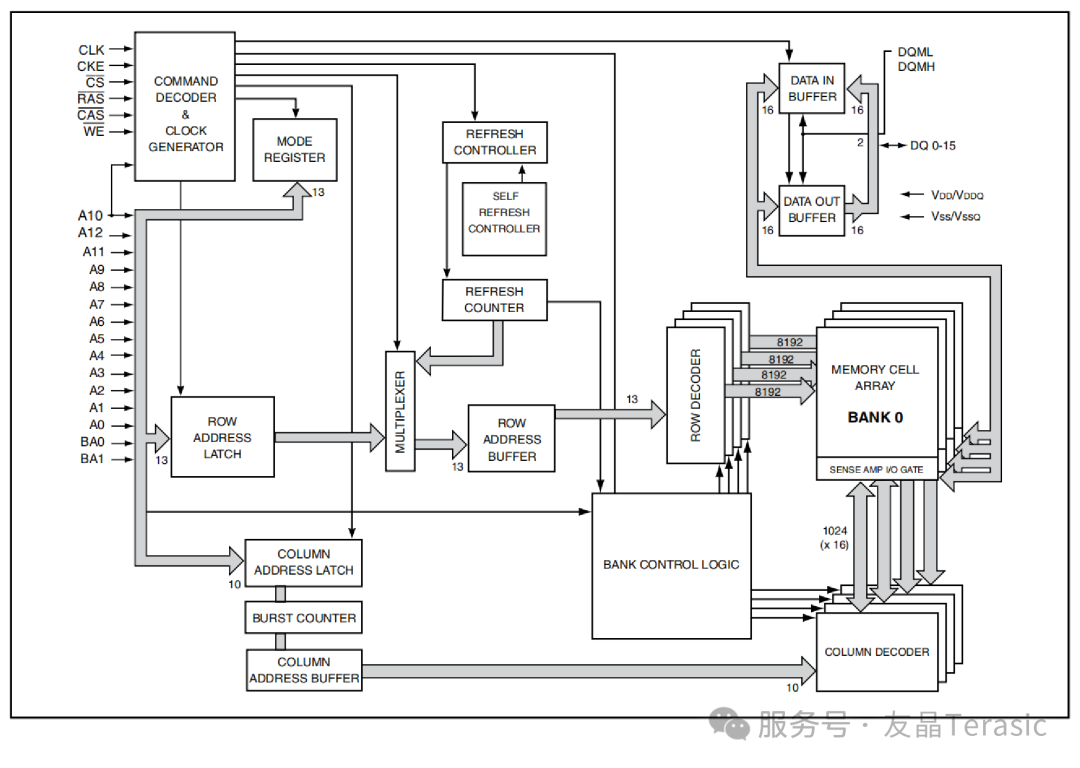

IS42R16320D功能框图▷▷▷

IS42R16320D的引脚功能描述:

备注:

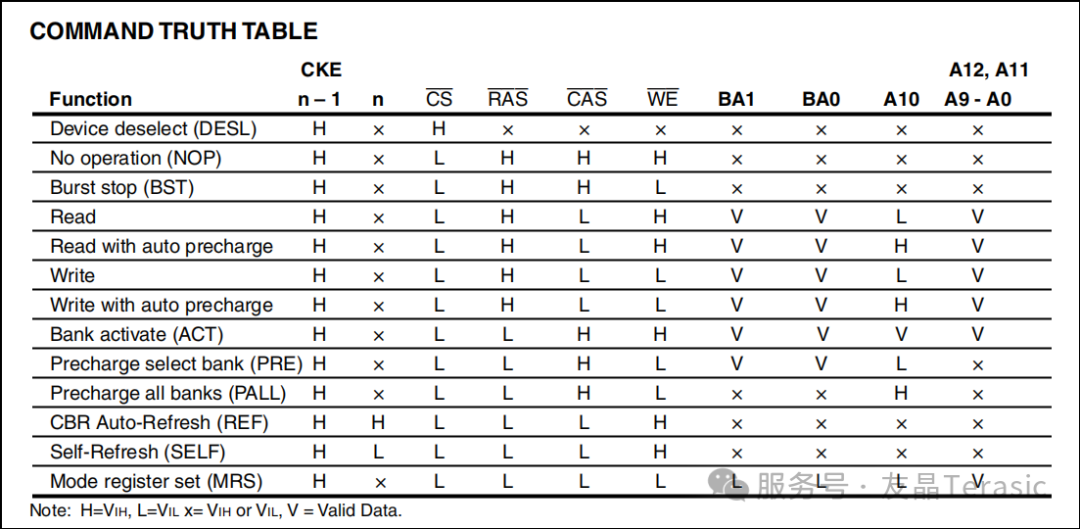

RAS\CAS\WE组合起来作为命令控制SDRAM的具体操作。

DQML和DQMH是数据输入输出掩码,IS42R16320D数据输入输出一次是16bit,有的时候只需要取高字节8位或者低字节8位的时候,就可以通过这两个信号线来控制哪个字节有效。注意DQM在写操作时是立即生效,DQM在读操作时是2个时钟周期后生效。

SDRAM的命令控制▷▷▷

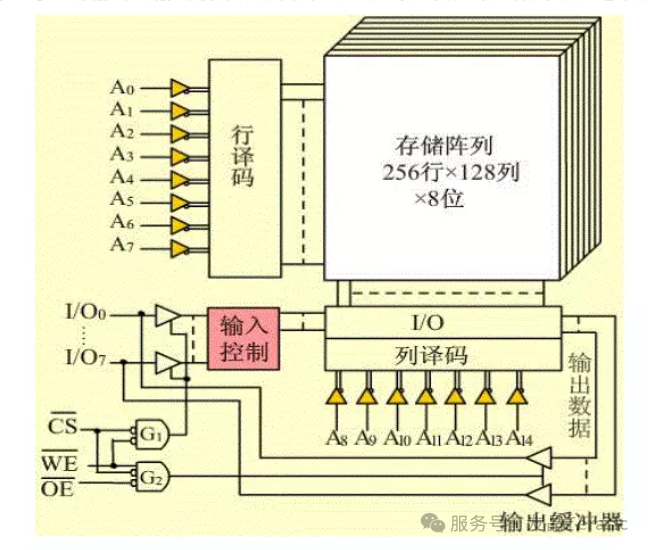

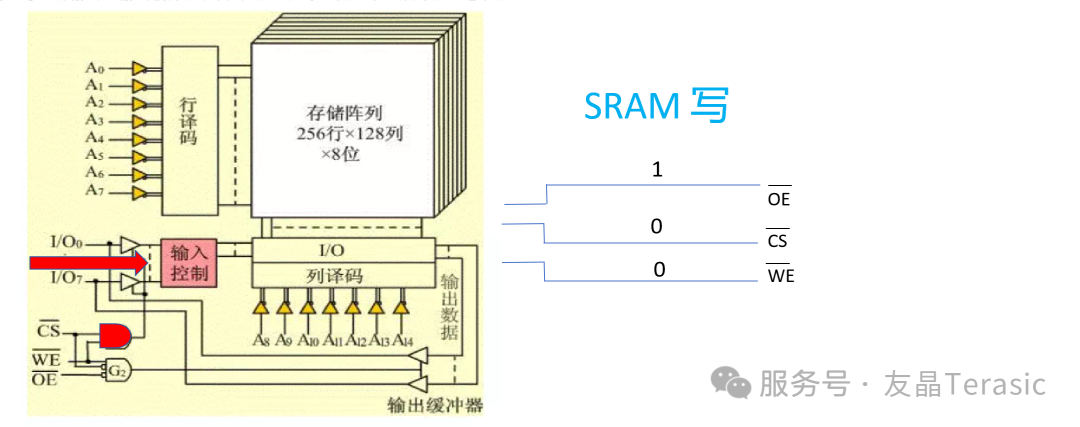

在了解IS42R16320D命令控制之前可以先参考普通SRAM读写控制原理:

下图为32KByte容量的SRAM结构示意图,该SRAM有8位行地址,译码后生成 256根(2的8次方)行地址线,列地址线为7位,译码后生成128根(2的7次方)列地址线。

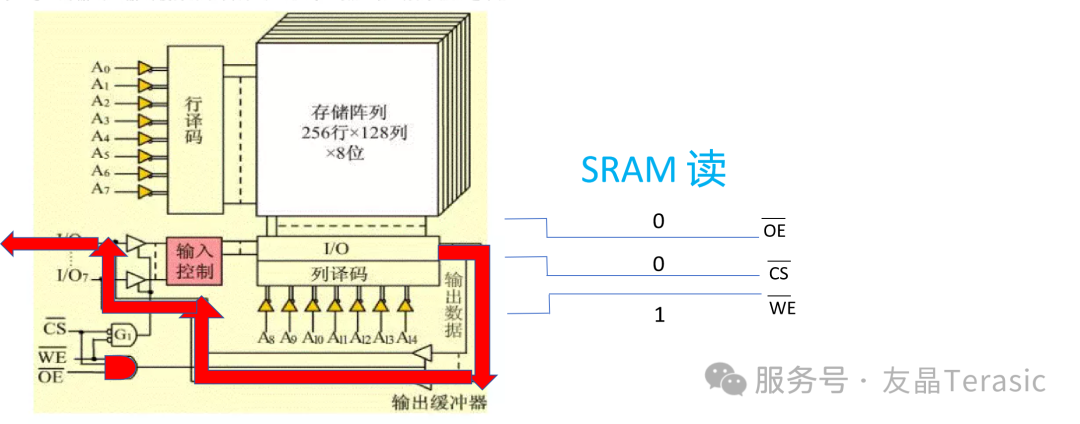

对SRAM进行读操作时,0E#和CS#为低电平,WE#为高电平,G1输出低电平将输入控缓冲器关闭,G2输出高电平将输出缓冲器打开,通过行列地址线选中的存储单元数据经I/0和输出缓冲器,最后从I/0[0:7]输出,如下图:

对SRAM进行写操作时,WE#和CS#为低电平,0E#为高电平,G1输出高电平将输入缓冲器打开,G2输出低电平将输出缓冲器关闭,I/0[0:7]上的输出经输出缓冲器和内部I/0总线,最后写入行列地址选中的存储空间中。

SDRAM的读写控制跟SRAM读写控制类似,但是因为SDRAM行列地址复用,支持突发读写等等,SDRAM的读写控制会更复杂一些,它主要由RAS\CAS\WE等信号组合起来作为命令控制SDRAM完成各项操作。

控制SDRAM的常用命令有:

以上表格参考IS42R16320D数据手册第9页:

下面结合IS42R16320D数据手册给出的命令发送时序图详细介绍SDRAM 的各项常见操作。

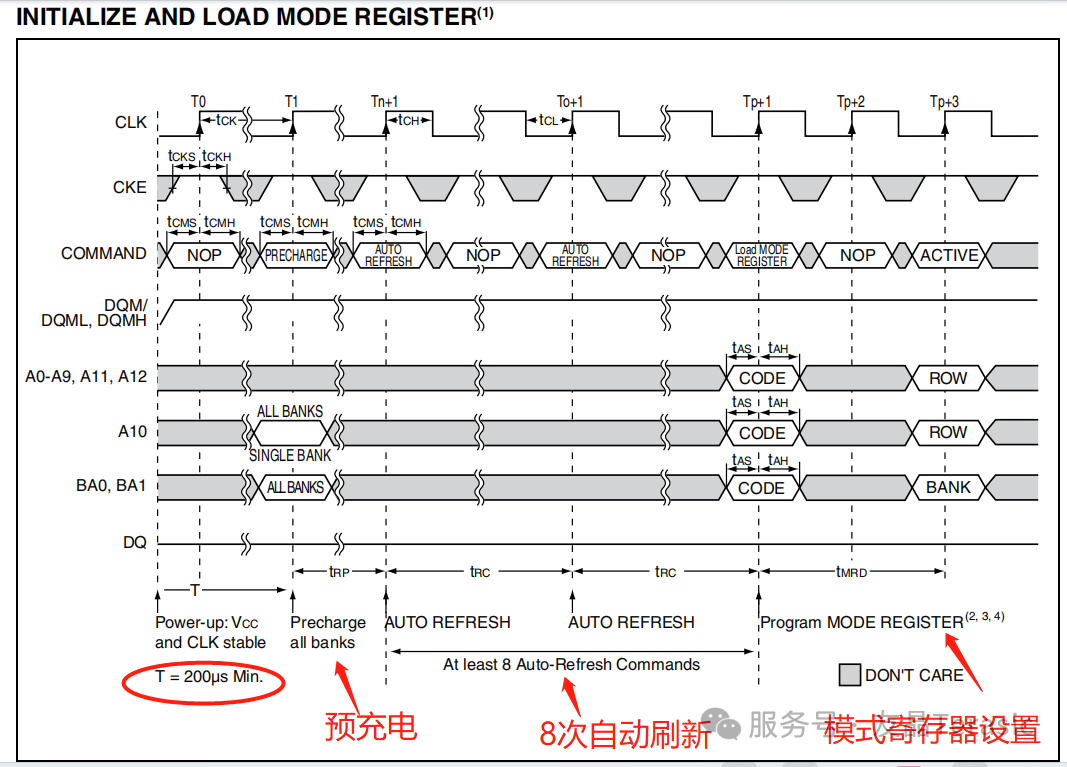

上电后SDRAM器件要先初始化之后才能正常工作。不同型号的SDRAM器件其初始化要求可能不同,详细要看对应的 datasheet。

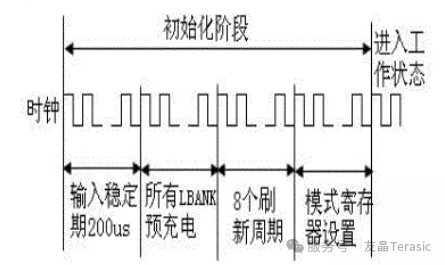

IS42R16320D的初始化过程是至少等待200us(用于等待power和时钟稳定),然后进行1次预充电(对所有bank)和8次自动刷新操作,然后设置模式寄存器。其时序图如下:

其中预充电命令发送以后要经过tRP时间才能完成预充电操作,自动刷新命令发送以后要经过tRC时间才能完成自动刷新操作,模式寄存器设置命令发送以后要经过tMRD时间才能完成寄存器设定。以上命令发送后的等待时间以及最初的200us延迟时间内,只有NOP命令有效。

其实把这个时序简化一下就是这样:

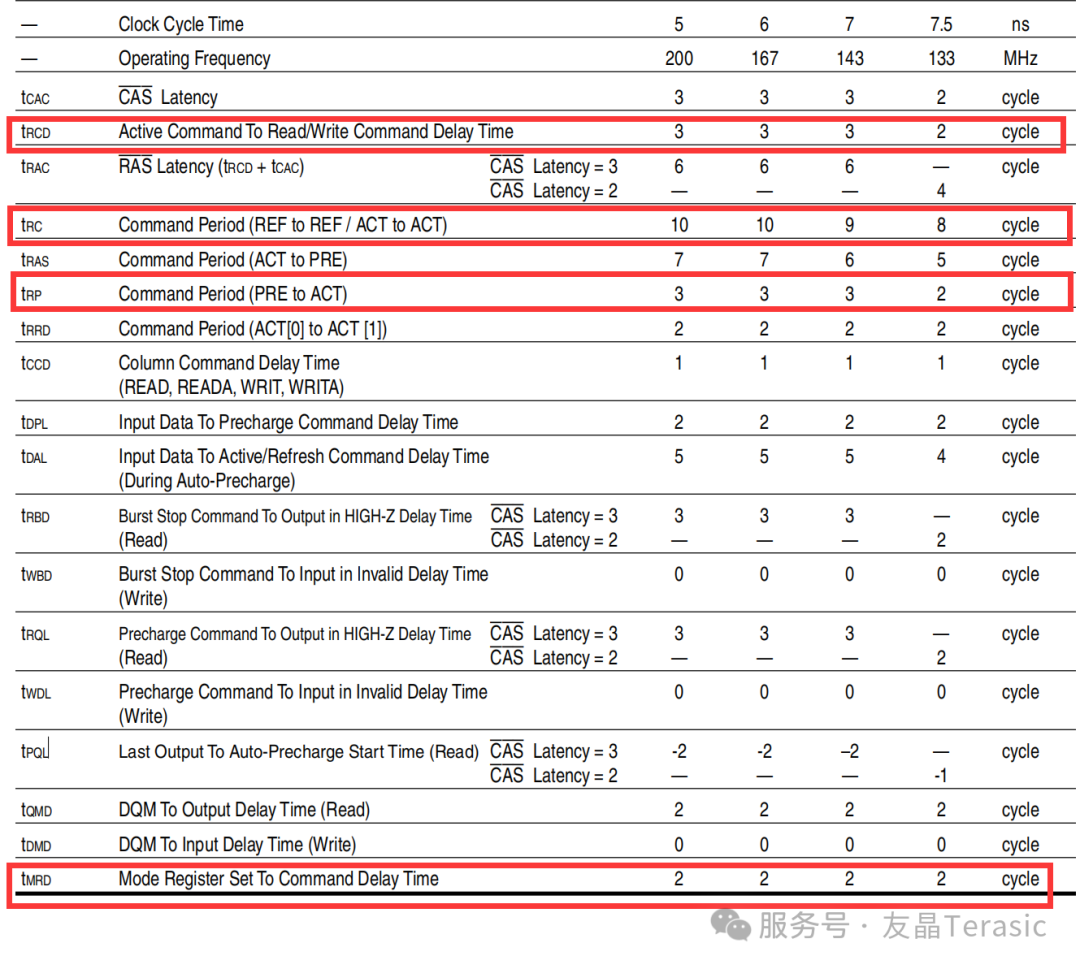

IS42R16320D数据手册第19页可以看到,tRP时间是2-3个时钟周期,频率高一点(200MHz)至少要3个周期,频率低一点(133MHz)至少要2个周期,为了保险,在写Verilog代码的时候时间可以设定比这个长一点。比如本案例跑100M,一个时钟周期是10ns,那么预充电等待时间可以设定为2个时钟周期以上。

根据如下IS42R16320D数据手册截图可知tRP时间是2-3个时钟周期,本案例代码里面设定等待20个时钟周期;

tRC时间是8-10个时钟周期,本案例代码里面设定等待20个时钟周期;

tMRD时间是2个时钟周期,本案例代码里面设定等待20个时钟周期;

tRCD时间是2-3个时钟周期,本案例代码里面设定等待3个时钟周期。

1. 预充电

由于 SDRAM 的寻址具有独占性,所以在进行完读写操作后,如果要对同一 L-Bank 的另一行进行寻址,就要将原来有效(工作)的行关闭重新发送行/列地址。L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。

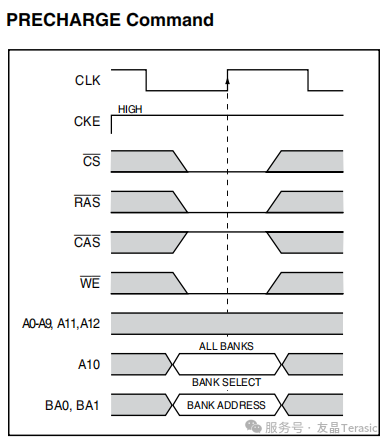

预充电时可以是对指定bank操作,也可以是对所有bank操作。通过地址线A10和BANK线BA0、BA1来决定。如果是对指定BANK操作时,A10设置为0,并由BA0、BA1指定某一BANK。如果是对所有BANK操作,A10设置为1即可。

SDRAM在初始化阶段要进行一次预充电操作。这个操作是对所有BANK进行的操作。

预充电要等待tRP时间。

预充电命令CS\RAS\CAS组合是010。

自动预充电

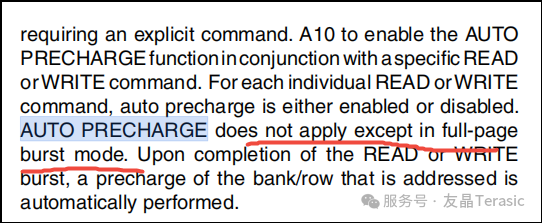

可设置让芯片每次读写操作后,自动进行预充电(在发送读写命令时通过A10信号线设置)。这样设计时无需要关心,只需要等待几个时间周期即可。

注意,突发模式下,当突发长度为全页时不支持自动预充电命令。

2.自动刷新

由于cell的电容很小,并且CMOS晶体管在关闭的时候,也存在漏电,这样电容上的电荷也在随着时间的变化,逐渐变少。时间一长,存储的信息就会丢失。为了解决这一问题,具体做法是对于每个单元行,每过一段时间就进行读取,等放大器暂存好信息后就立刻将其写回行。IS42R16320D数据手册第一页提到每64ms内就要对cell阵列进行一次全面刷新。

![]()

自动刷新要等待tRC时间。

自动刷新命令RAS\CAS\WE组合是001。

自动刷新期间不能做其他操作。

区别于自刷新(SELF REFRESH),这个是在SDRAM休眠下为确保数据不丢失的自动操作。在发出自动刷新命令时,将CKE置于无效状态,就进入了自刷新模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在自刷新期间除了CKE之外,所有外部信号也都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常工作状态。

关于SDRAM 自动刷新动画请参考B站视频:

3. 模式寄存器设置

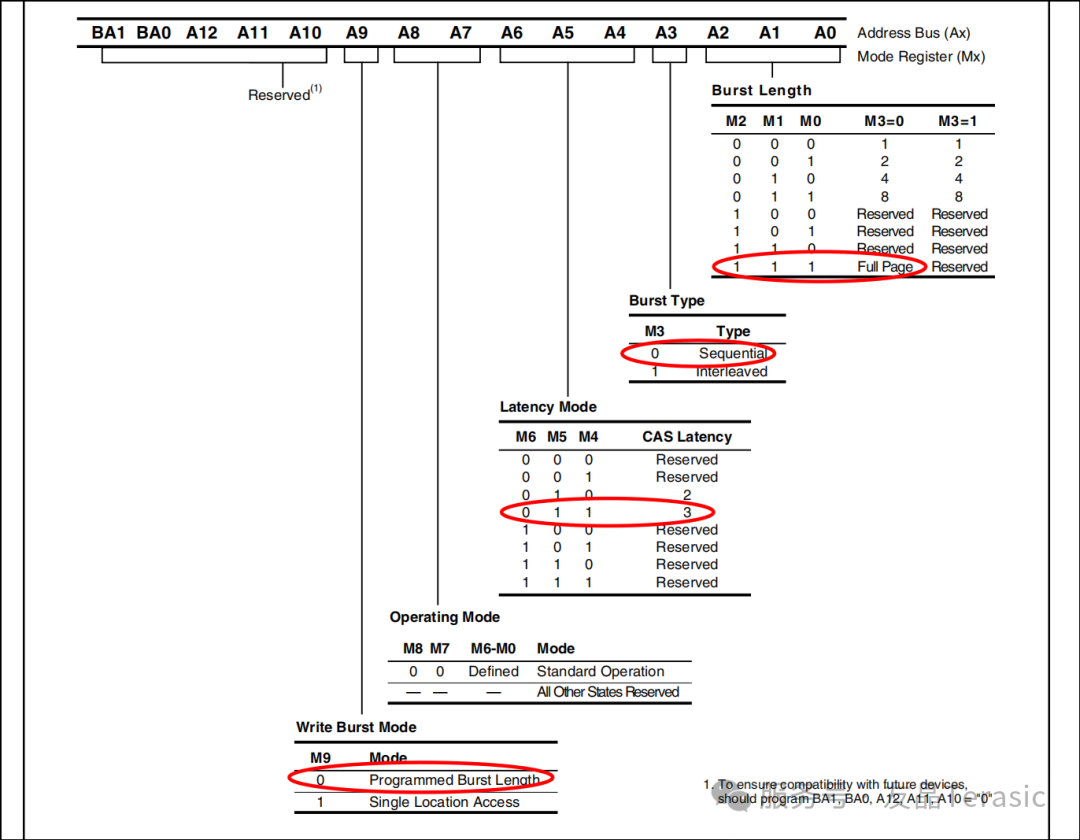

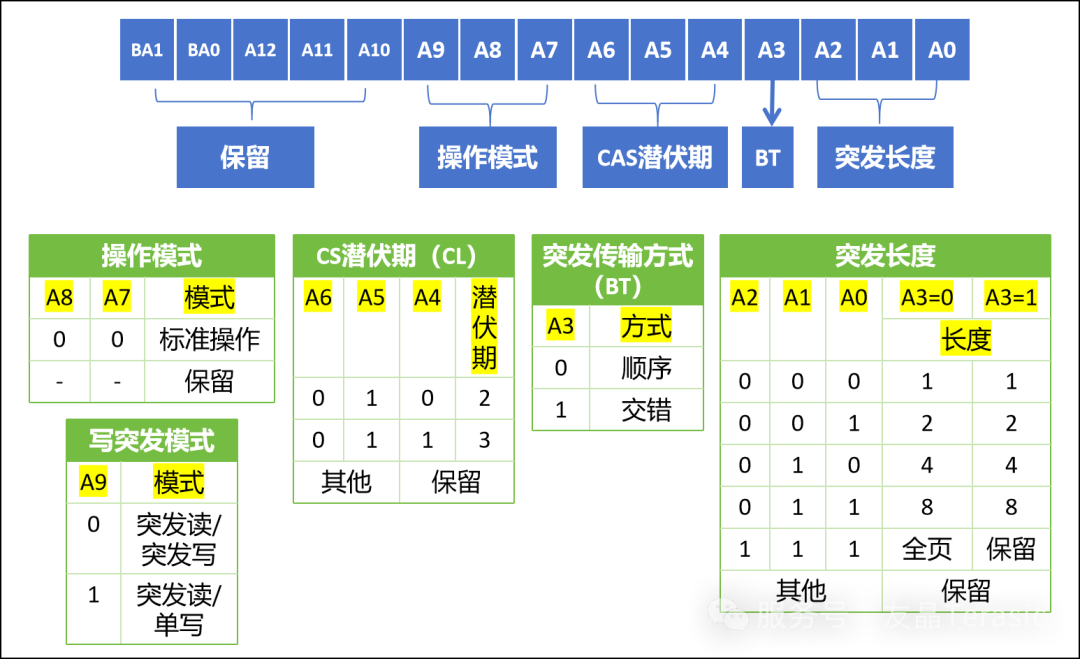

SDRAM芯片内部有一个逻辑控制单元,这个控制单元的相关控制参数是由MR(Mode Regisister模式寄存器)提供,SDRAM芯片每次进行初始化时都要将重新写MR。MR 中设置了 SDRAM 的运行模式:包括突发长度(BL)、突发类型(Burst Type)、CAS 延迟(CAS Latency)、运行方式(Operating Mode)和写入突发模式。

将上面表格翻译下如下:

突发 burst长度

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式。只需要在行激活后,给出一次读写命令和列起始地址以及突发长度,就开始读/写一定长度数据,列地址自动递增。

连续传输所涉及到存储单元(列)的数量就是突发长度(BurstLengths,简称 BL)。常见的突发长度是 1、2、4、8和全页(全页指的是一整行,比如IS42R16320D一个bank的一行是1024个存储单元,那么全页就是1024个)。

突发读写完或者提前结束突发读写时,需要发送突发停止命令(BURST TERMINATE),或者发送预充电命令(PRECHARGE)。

本案例设置突发长度是全页,A0A1A2设定为111。

突发类型

突发类型也叫突发传输方式,IS42R16320D突发类型支持顺序传输和交错传输。顺序传输就是连续地、依次地读后面的几个存储单元,交错传输就是隔一个读一个。

本案例设置为顺序传输(只有顺序传输支持全页的突发长度),A3设置为0。

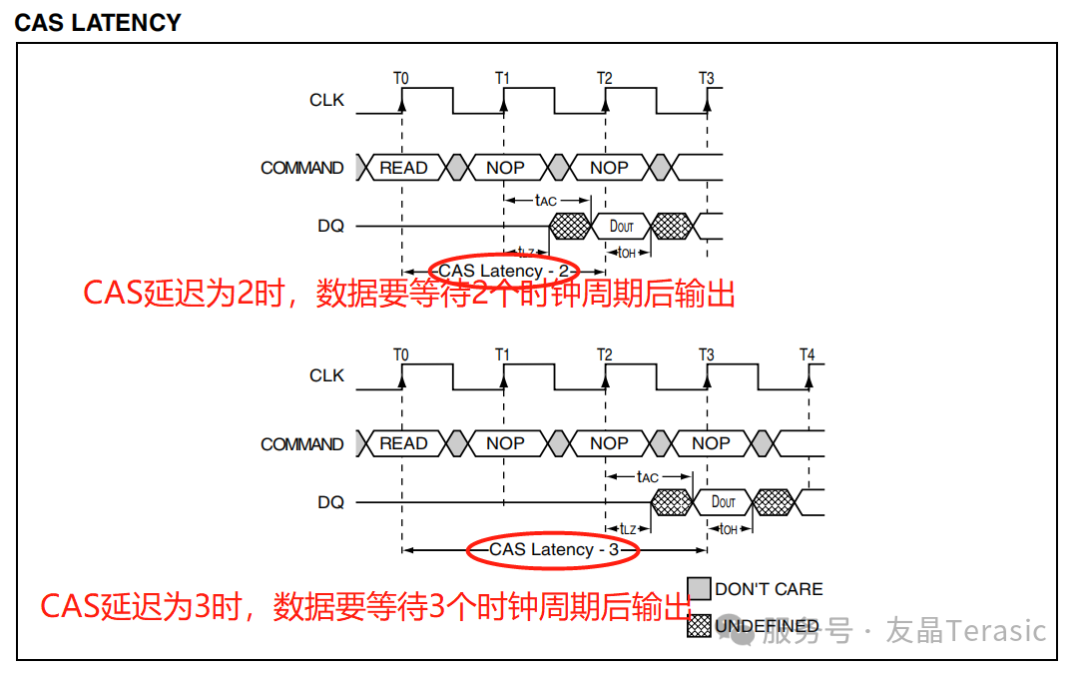

CAS潜伏期

在读命令发送了列地址后,数据并不是马上到达数据总线,而是要经过一段潜伏期,一般为2到3个时钟周期,注意潜伏期不是延迟,潜伏期是发送列地址后数据已经有效,只是还没有达到一定的高度,或者说是信号不够强,要经过一定的放大才能输出,所以说潜伏期不是延迟。

只有读操作时存在CAS潜伏期。

本案例设置CAS为3,A6A5A4设置为011。

突发操作模式

操作模式可以分为突发读/突发写,或者是突发读/单一写等。

突发读就是在读命令发送了起始列地址,在读取第一个数据之后,如果想读取这个存储单元后面的存储单元的数据的话,就不必再次发送行列地址了,他会自动的读取接下来的数据,至于读几个存储单元,就涉及到突发长度,比如若设置的是全页的方式,就是将这一行上的数据一连串的全部读出或写入。

本案例设置为突发读和突发写,A9设置为0。

设置模式寄存器操作要等待tMRD时间,一般是2个时钟周期。

模式寄存器设置的命令RAS\CAS\WE组合是000。

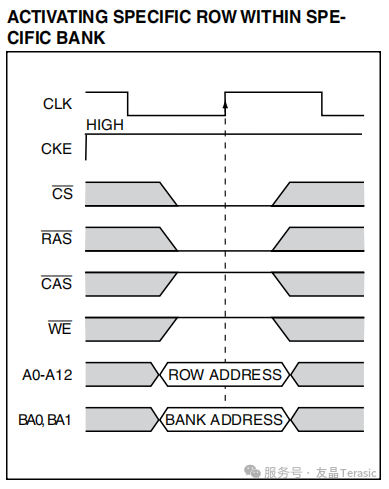

4. 激活

初始化完成后,要想对某个bank进行读写操作之前,先要对这个bank中的阵列进行寻址,首先要确定行(Row),使之处于活动状态(Active),然后再确定列。虽然之前要进行片选和L-Bank 的地址,但它们与行有效可以同时进行。

激活操作要等待tRCD时间,一般是2-3个时钟周期,本案例设置为3个时钟周期(SC_RCD=3)。

激活命令RAS\CAS\WE组合是011。

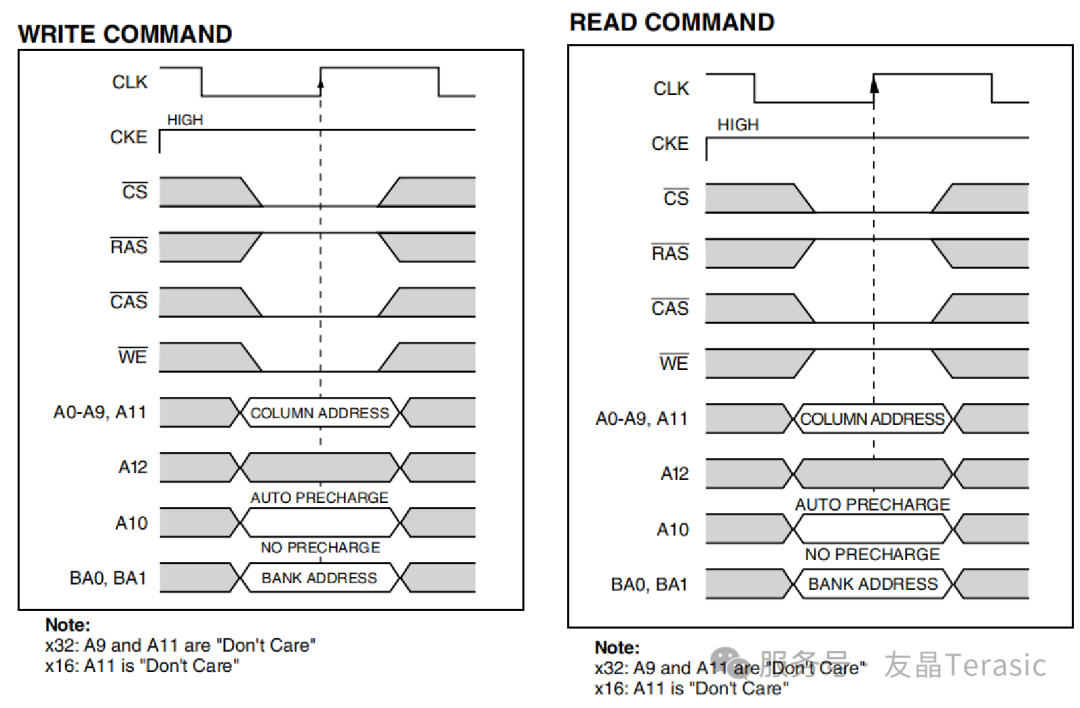

5. 读写操作

行地址确定之后,就要对列地址进行寻址了。在SDRAM中,行地址与列地址线是共用的,列地址线是 A0-A10。读/写命令是通过WE#信号的状态去区分的,当WE#为低电平有效时是写命令,为高电平无效时是读命令。列寻址信号与读写命令是同时发出的。虽然列地址线与行寻址共用,当CAS为有效电平时,地址线输入的地址作为列地址;(当RAS有效时,地址线输入的地址作为行地址)。列读写时序如图所示。

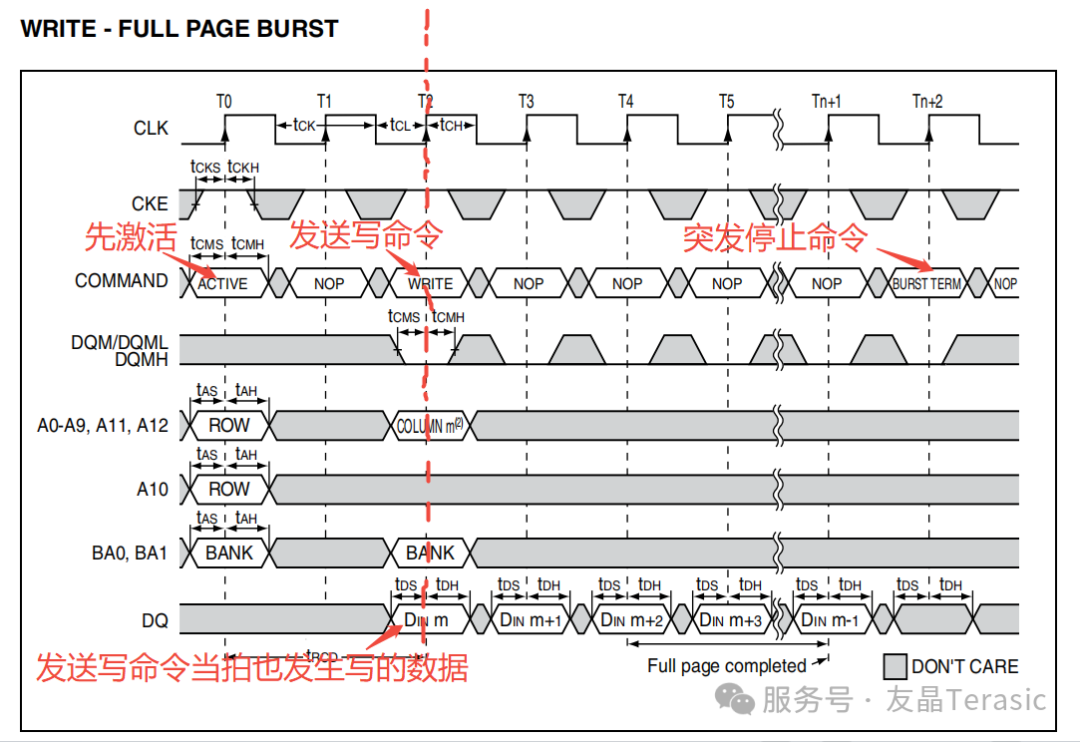

本案例设置的是突发读写, 突发写的时序图如下:

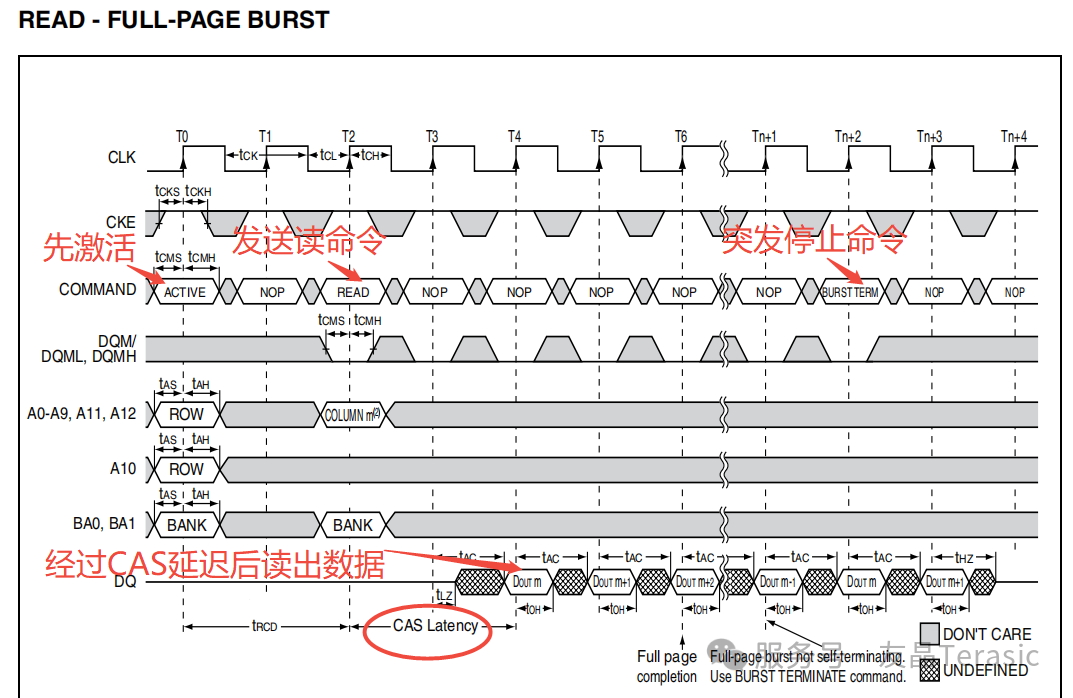

突发读的时序图如下:

往期阅读:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?