参考过的文章:

- ace-lite用来连接不带cache的io硬件设备,这些设备需要访问缓存一致性的内容。

- ace的组件和拓扑:

- 缓存主设备:具有缓存能力的主设备,能够发起事物并管理自己的缓存。

- 发起主设备:发起事物的主设备,可以是缓存的或者是非缓存的。

- 被监听主设备:能够接收并响应其他主设备发起的snoop事物的缓存主设备。

- 下游缓存:位于发起主设备下游的缓存。

- 本地缓存:主设备自身的缓存。

- 对等缓存:与发起主设备在同一层级的缓存,根据发起主设备的操作来更新自己的缓存。

- 监听过滤器:决定是否需要对特定的内存访问进行监听。

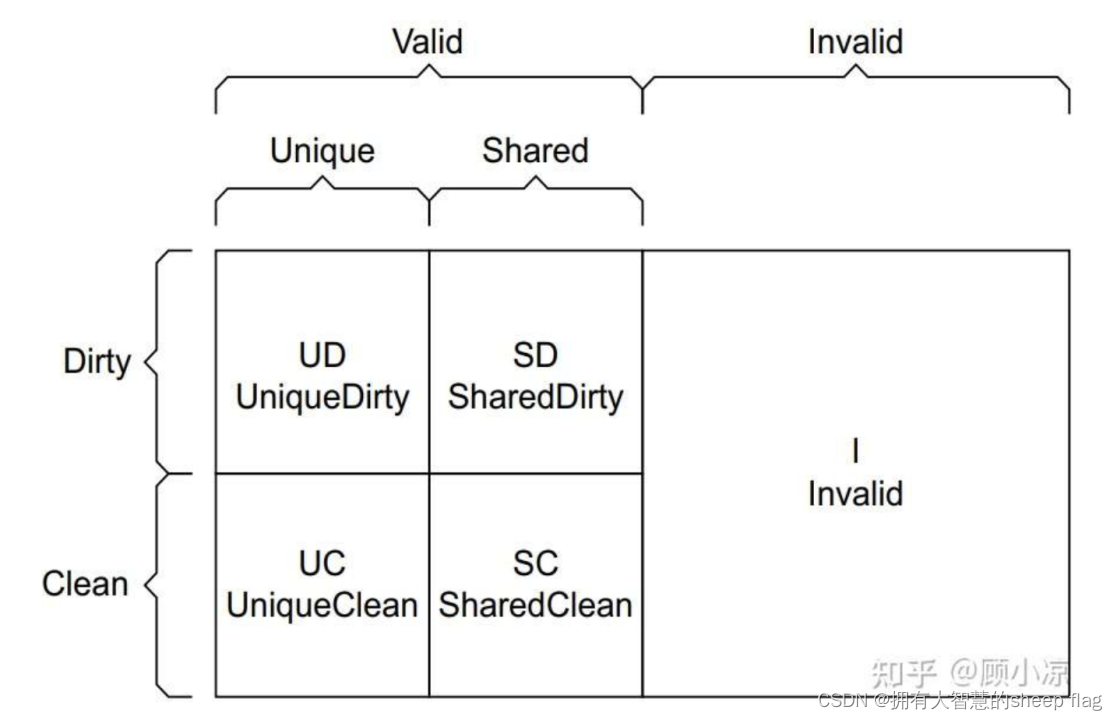

3、ace定义的五种状态模型:

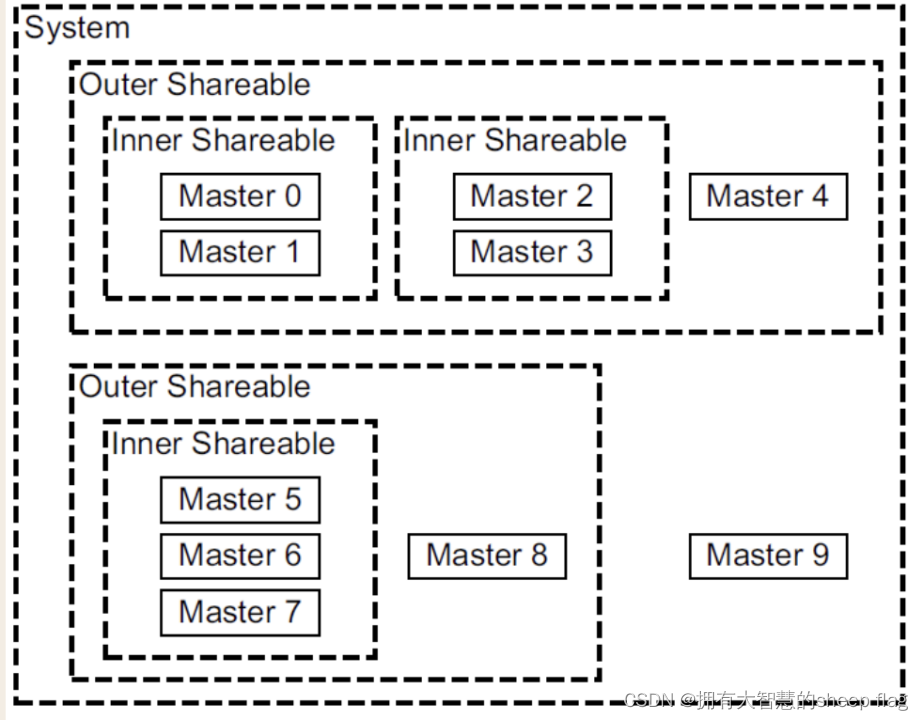

4、ace中定义的4种domain:

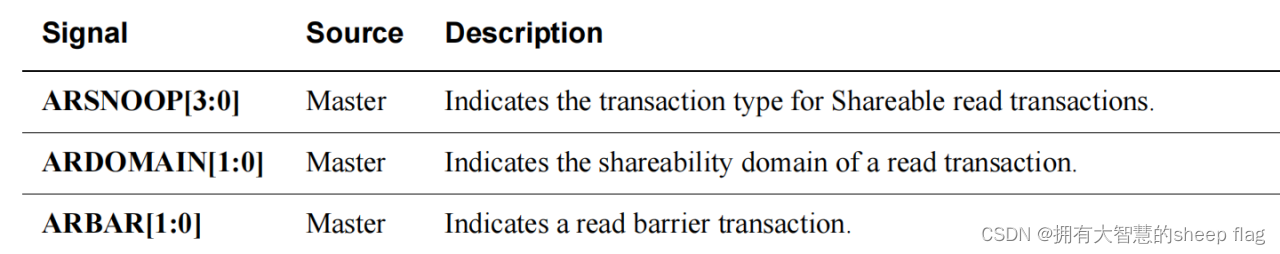

5、ace在ar通道增加的信号

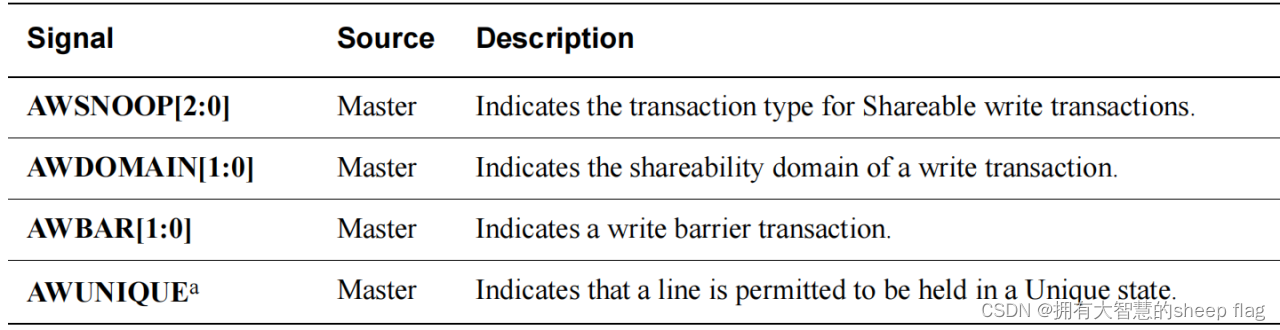

在aw通道增加的信号:

在R通道上增加的信号:

| RESP[2] | PassDirty | cacheline is dirty |

| RESP[3] | IsShared | 读回来的数据是share的状态 |

另外在r通道和w通道增加了ack信号指示ace传输的完成。

AC、CD、CR的通道是为了使master之间相互通信。

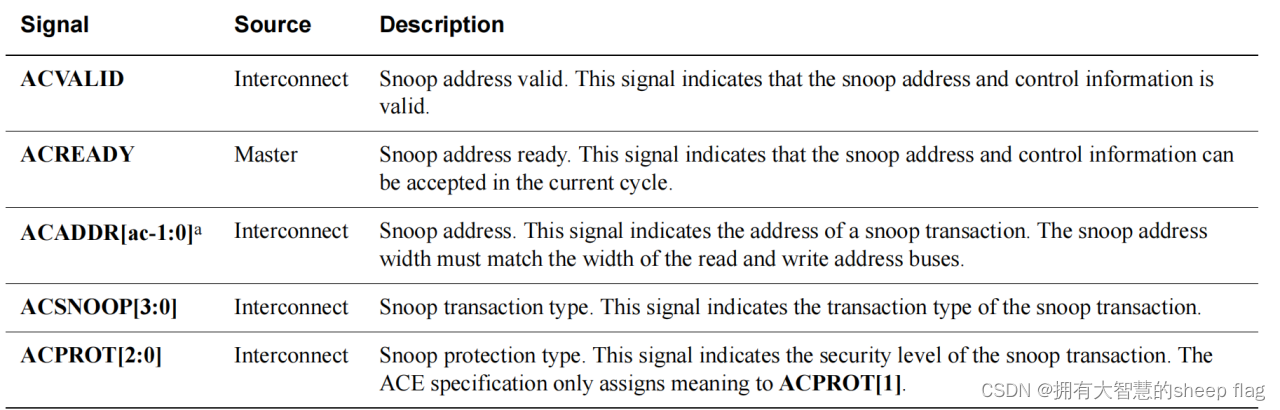

增加的AC通道:

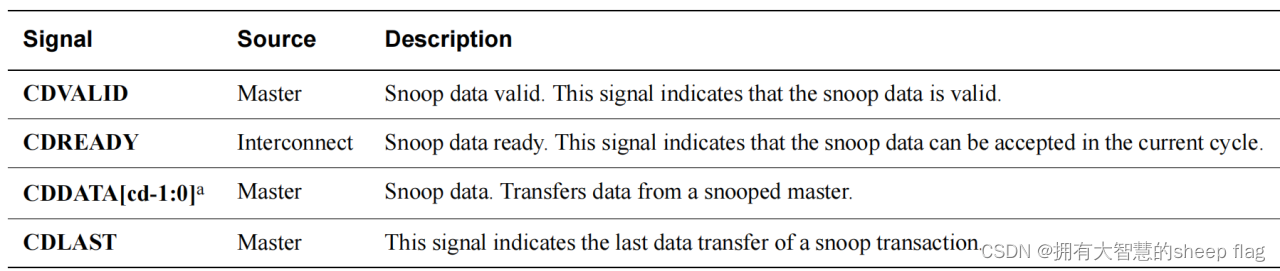

增加的CD通道:

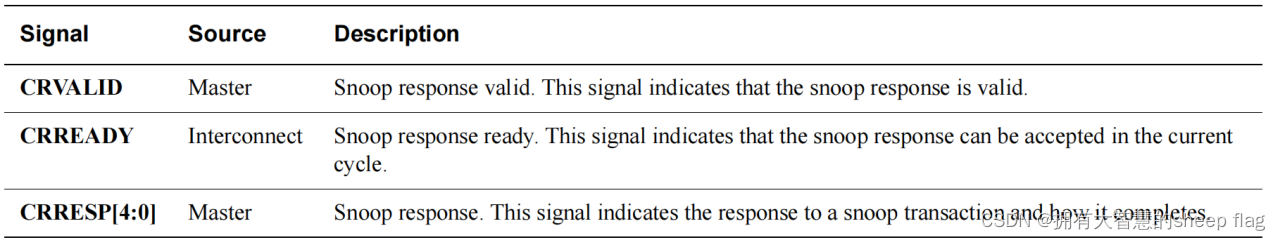

增加的CR通道:

6、ACE中的事物主要分为non-snooping、coherent、mem update、cache maintenance、barrier、virtual mem几种。

- non-snoopng:WriteNoSnoop、ReadNoSnoop,其他核心不需要监听。

- coherent:访问共享的内存地址,可能保存在其他master中,ReadClean,ReadNotSharedDirty,ReadShared,ReadUnique,CleanUnique,make unique,ReadOnce,WriteUnique,WriteLineUnique

- mem updata:WriteBack,WriteClean,WriteEvict(将数据更新到低一级cache,不需要更新到mem),Evict(特定组件中的高速缓存行能被跟踪,用于构建snoop fliter等应用),其他核心不需要监听。

- cache maintence事物:clean shared、clean invalid、make invalid。

- barrier事物:mem barrier,synchronization barrier(在屏障之前的事物全部接收到响应)

- DVM事务:在分布式虚拟内存系统组件之间传递消息。

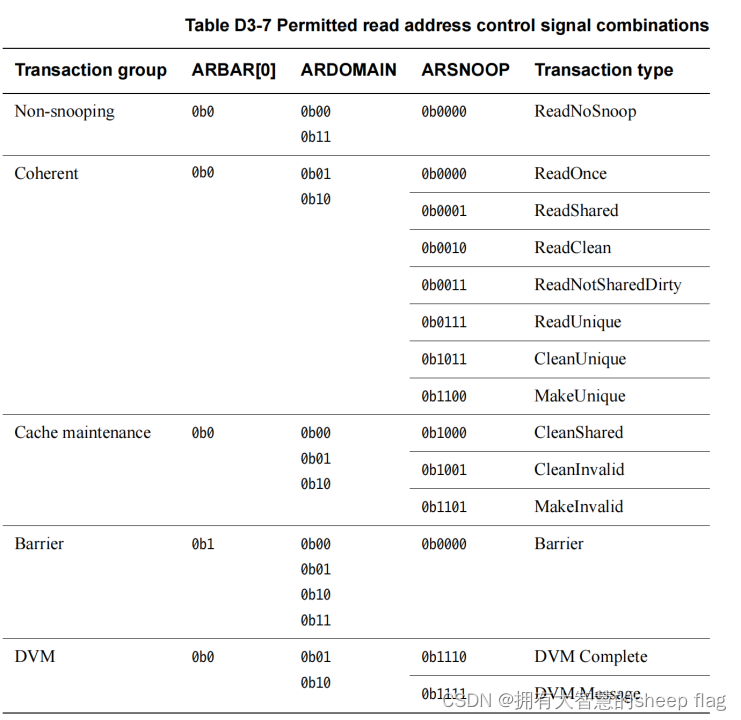

7、读通道相关的信号,其发出以下几种事务,bar,domain snoop信号的置位如图所示,ReadNoSnoop,ReadOnce,ReadClean,ReadNotSharedDirty,ReadShared,ReadUnique,clean transcations的相关事物(no data):CleanUnique,Cleanshared,Cleaninvalid,make transcations相关的事物(no data):make unique,makeinvalid and readbarrier transcation。

8、写通道的信号:write transcation包括WriteNoSnoop,WriteUnique,WriteLineUnique,WriteBack,WriteClean,WriteEvict。evict transcation and write barrier transcation

9、对应的组合信号如下所示。

读操作的一般流程:

- 发起端 mst 通过AR通道发出读 tr 到 cci ;

- cci 将读命令发送给其他 mst.cache,通过其他 mst 返回的 resp 信号,判断在其他 mst.cache 中是否存在相同地址的 cache line;

- 如果 resp 表示存在对应的 cache line,对应的 mst会通过 CD channel传递出 data;

- 如果有 mst.cache 传出了 data,CCI 会将 data 通过 RD 通道传递给发起端的 cache;

- 如果其他 mst.cache 中没有对应的 cache line,那么:a. CCI 会将发起端发出的读 tr 发送到主存或者总线buffer返回;b. 读数据会像标准 tr 一样,返回到发起端的 cache;

- 发起端 cpu 收到读数据完成后,会向 CCI 返回一个 RACK 信号。

写操作的一般流程

(1)在写操作之前,发起端mst有对应的cacheline副本。

- 发起端 master 通过AR通道发出 CleanUnique tr 来请求作为唯一副本; (这个 tr 不会返回 cache line 的数据,只会返回一个 resp,用于清理其它 mst.cache 中对应的 cache line)

- CCI 通过 AC通道向其他 cache 发出 snoop_tr。被监控的 mst 会在 CR通道返回 resp 来表示: ① 对应的 cache line 已经被移除了;② 是否有 dirty 状态的 cache line 需要被写入主内存;

- 如果有②的情况,dirty 属性的 cache line 会通过 CD通道发送到 CCI 中,然后 CCI 会将这个 dirty 属性的 cache line写入主存,并且这个 cache line 会被清理;

- CCI 将 resp (exok)信号返回到发起端的 cache,(只返回的 resp,不返回 data)

- 发起端 mst 完成对 cache 的写操作;并发出 RACK ,用来表示 CleanUnique tr 的操作完成。

(2)在写操作之前,发起端mst没有对应的cacheline副本,写部分cacheline。

- 发起端 mst 要先获取对应的 cache line,然后通过AR向其他 CCI 发送 ReadUnique tr,用来删除其他 cache 中对应地址的 cache line;

- CCI 将地址通过的 AC 传递给其他 cache;

- 如果其他 mst 有对应地址的 cache line,那么它会向 CCI 返回以下数据: ① 通过 CR 通道返回一个响应信号[3:2]=0,[0]=1,表示存在对应的 cache line,并且已经删除; ② 通过 CD 通道返回对应的 data;

- CCI 会通过 RD 通道向发起端的 mst 返回 resp 和 data 信号;(如果没有其他 cache 响应,就向主存获取 cache line 参数)

- 发起端的 mst 写完对应 cache line 之后,会发出 RACK 信号到 CCI,表示已经获取 cache line 完成。

(3)在写操作之前,发起端mst没有对应的cacheline副本,写整个cacheline。

- 发起端的 cache 通过向 CCI 发送 MakeUnique tr,使其他 mst 中对应地址的 cache line 无效;

- CCI 通过 AC 通道传递 MakeUnique tr 对应的 snoop_tr;

- 如果其他 mst 中有对应的 cache line,那么它会通过 CR 通道向 CCI 返回 resp=0,表示对应的 cache line 已经被删除;

- CCI 通过 RD 通道将步骤3 的 resp 发送给发起端 mst。(这里只传递了 resp,没有 data)

- 发起端 mst 进行写操作,并发出一个 RACK 信号,表示之前的 MakeUnique tr 步骤完成。(这里的写,是直接在空的,或者 invalid cache line 中,写入对应的数据,写之前不需要获取 cache line)

写覆盖操作,两个mst同时对一个cacheline写操作,cci确定发生顺序,此处假设m1优先。

- M1 执行正常的写操作(如上)

- M2 通过它的 snoop_tr 获取 M1的写操作,然后根据覆盖写操作时自身缓存中有无对应 cache line和发出的写操作类型进行以下操作之一来完成任务:如果 M2 发出的是写部分 cache line,且 cache 中没有对应地址的 cache line,它会在自己的(CleanUnique)事务完成时接收 cache line 数据,然后正常地进行自己的写操作;如果 M2 发出的是写完整 cache line,M1 在写的过程中,会将 M2 中的对应地址的 cache line 进行 invalid。M2可以在自己的(MakeUnique)事务完成时继续处理自己的完整 cache line 写。

- 如果 M2 发出的是写部分 cache line,且 cache 中有对应地址的 cache line,因此正常情况下不用(向主存或者其他 cache)请求 cache line 的副本。但是要注意 M1 在写的过程中,会将 M2 中的对应地址的 cache line 进行 invalid,因此 M2 的 CleanUnique tr 操作完成后,需要使用以下两种方法之一:(因为是 CPU1 和 CPU2 同时发出 tr, 然后才是 CCI 判断 M1 先进行写操作,因此在当前 M2 是 partial store 的情况下,M2 已经发出了 CleanUnique tr,表示不要获取新的 cache line)所以需要进行下边二选一的额外步骤: )为了让 M2 中有最新的 cache line,M2 需要重新进行发出 ReadUnique tr 的操作;M2 直接 partial store 到主存,此时M2 还是没有对应的 cache line,为了之后的时间可能还会用到这部分内存,M2 还得再次获取这个 cache line。

10、介绍一下CR通道的resp

| CRRESP[0] | DataTransfer | 1、在CD上提供cacheline data |

| CRRESP[1] | Error | 1、cacheline数据是错的 |

| CRRESP[2] | PassDirty | 1、dirty的cacheline |

| CRRESP[3] | IsShared | 1、表示cacheline的clean的副本 |

| CRRESP[4] | WasUnique | 1、unique cacheline |

11、关于barrier事件:

- Memory barriers:如果适当域中的另一个 mst 可以在 barrier 之后观察到任何事务,那么它必须能够在 barrier 之前观察到每个事务。

- Synchronization barriers:Manager 组件发出同步屏障,以保证当 barrier 事务完成时,在屏障之前发出的所有事务都可以被适当域中的每个 mst 观察到。此外,还有一个额外的要求,在 barrier 事务之前发出的所有事务必须在屏障完成之前到达它们要到达的端点下级。

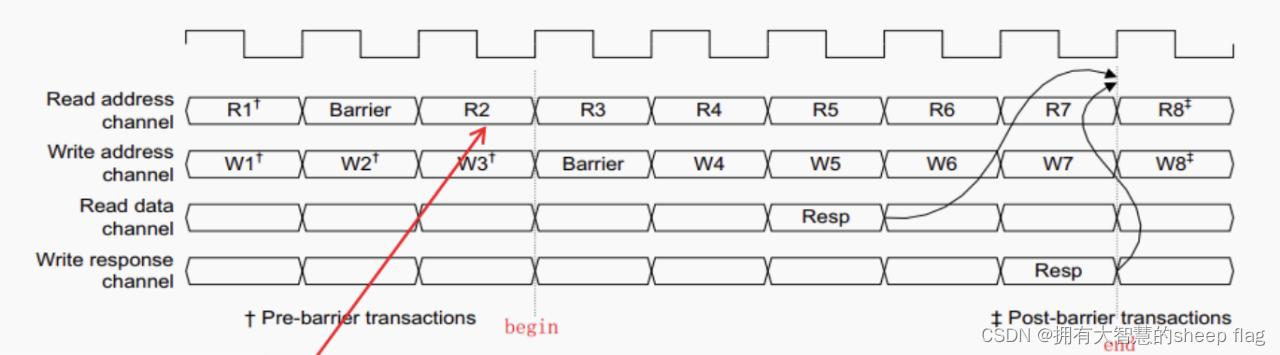

- 如图时序图:barrier 事务有一个地址(开始)阶段和一个响应阶段,但不发生数据传输。Mst 组件必须在读地址通道和写地址通道上发出屏障事务。barrier可以强制排序,因为只有barrier 之前发出的事务全部完成之后,barrier 的读写事务才会有 resp 返回,因此可以保证:barrier 之后的事务一定是建立在 barrier 发出前的事务全部完成基础上的。

- 应用:某些场合需要前后的串行执行,就需要mem fence。

12、ace推荐的最小cacheline大小位16B或者数据位宽,最大为2048B或者burst 16的最大data bus。

13、在store命令发生时,保证所有的cache中只有一个coppy的cache存在,store操作后允许一份cache有多个copy对象,更新mem时,允许copy的cache存在,不推荐这样做。

1641

1641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?