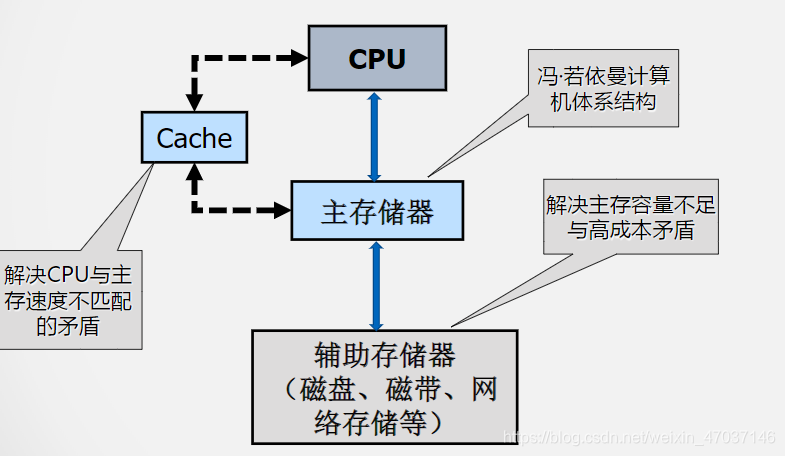

存储系统的层次结构

-

基本的存储系统

由存储程序和程序控制组成,分别对应主存和CPU。

输入设备将数据与程序写入主存——>CPU取指令——>CPU执行指令期间读数据——>CPU写回运算结果——>输出设备输出结果. -

存储系统的层次化结构

-

存储程序层次化的局部性

时间局部性:就是一个信息可能先后多次访问,体现在循环结构中;

空间局部性:访问一个信息周围的信息,体现在层次结构中。

主存中的数据组织

存储字长

- 存储字长是一个存储单元中所包含的二进制位数。

- 大多数计算机的主存按字节编址,存储字长有16位、32位、64位等

数据存储与边界关系

- 按边界对齐的数据存储

不同数据类型的首地址应该是所占据空间的整数倍,会造成空间浪费; - 未按边界对齐的数据存储

不同数据挨着存储,节省空间但增加了访问的次数。

大端存储与小端存储

- 大端存储:最高字节地址作为数据存储的起始地址

- 小端存储:最低字节地址作为数据存储的起始地址

大端存储:大端模式,是指数据的高字节保存在内存的低地址中,而数据的低字节保存在内存的高地址中,这样的存储模式有点儿类似于把数据当作字符串顺序处理:地址由小向大增加,而数据从高位往低位放。小端存储:小端模式,是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

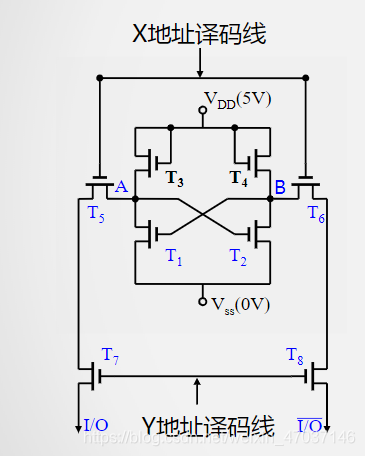

静态存储器的工作原理

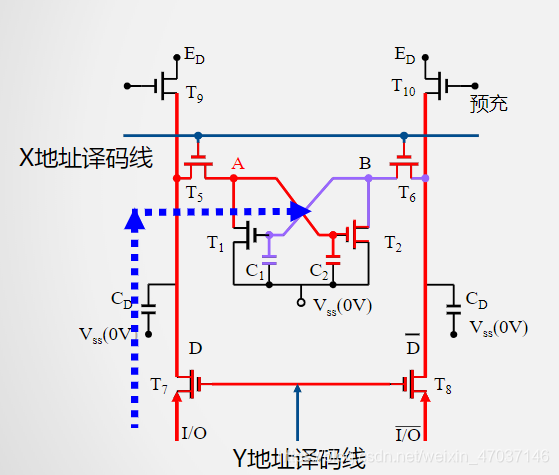

SRAM存储单元结构

-

工作管:T1、T2,保存数据

-

负载管:T3、T4,补充电荷

-

门控管:T5、T6、T7、T8

X选通时,T5、T6导通,A与位线相连

Y选通时,T7、T8导通,A与I/O相连 -

写过程

X、Y选通时,A与I/O和位线导通,B与I/O非和位线相连,如果I/O=1,则A点是高电平,使T4导通,B与地相连,为低电平;写0时与此类似。 -

读过程

X、Y选通,根据I/O和I/O非电流的流向判断读出的是0还是1。 -

保持

X、Y撤掉,由VDD提供电压,保持稳定互锁状态。

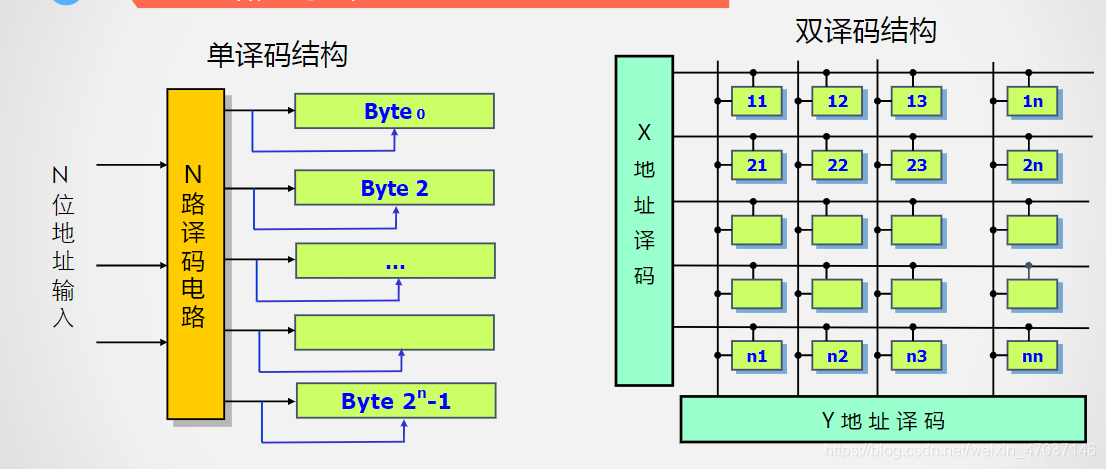

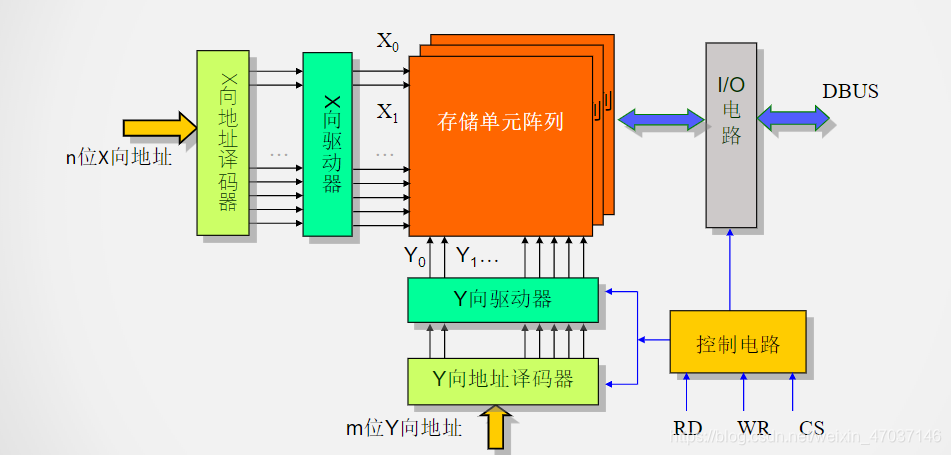

静态存储器的结构

单译码结构可以访问2n个存储单元,需要2n根译码线

双译码结构可以访问2n个存储单元,需要2(n/2)+1根译码线。

动态存储器

-

动态存储单元

-

读操作

Y选通,I/O输入到位线,X选通,与电容连通,也就是通过电容的充放电实现互锁。 -

写操作

首先给预充电通电,使两个Cd充电,然后X选通,右边的电容给C1放电,左边的电容给C2充电,使状态保持;然后Y地址选通,左边的电容还没放完电,所以在左右两边存在电势差,根据电流的流向判断输出的是1还是0. -

保持操作

X和Y信号撤离,电容中有电,可以保持状态的互锁。 -

刷新操作

由于电容的电量有限,保持的时间很短,需要进行刷新保持状态。

先预充电,使左右两边的电容有电,然后X选通,就和上边写操作第一步一样了,不过不需要Y选通,就是不用读出数据,只需使状态保持。

- 刷新周期:两次刷新操作之间的时间间隔。刷新时按行刷新。

- 刷新地址由刷新地址计数器给出。

- 刷新方式:

集中刷新:所有存储单元都访问过后一起刷新,平均的读写时间短,但读写存在延迟。

分散刷新:读写一次刷新一次,平均读写时间扩大二倍。

异步刷新:将刷新周期平均分为存储单元行数个,每读写一行刷新一行,平均读写时间和集中刷新一样。

此外,动态存储芯片的行和列线分开,用于刷新时选用。地址线也复用做选片的线。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?