大家好,最近写了几个分频器。实现奇数分频和偶数分频效果,且占空比满足50%,代码已经经过测试,需要可自取。感谢关注。

一、上代码

`timescale 1ns / 1ps

//

module CLK_DIV_ODDandEVEN50P

#(

parameter Multiple = 11 //Multiple表示的是倍频倍数。

)

(

input sys_rst,

input sys_clk,

output clk_div ,

output [15:0] cnt

);

wire odd ;

wire even ;

assign odd = (Multiple[0]==1'b1)?1'b1:1'b0; //奇数判断

assign even = (Multiple[0]==1'b0)?1'b1:1'b0; //偶数判断

assign clk_div = (odd)?clk_odd: (even)?clk_even:0; //将奇数或者偶数分频结果输出

reg [15:0] cnt=16'b0;

always@(posedge sys_clk)

begin

if(sys_rst) //复位信号,高有效

begin

cnt <= 16'b0;

end

else

if(cnt == (Multiple -1))

begin

cnt <=16'b0;

end

else

begin

cnt <= cnt + 1'b1 ;

end

end

//--------奇数分频过程------start---------//

reg clk_oddP=1'b0;

always@(posedge sys_clk)

begin

if(sys_rst) //复位信号,高有效

begin

clk_oddP <= 1'b0;

end

else

if(cnt <= (Multiple /2 ))

begin

clk_oddP <= 1'b0 ;

end

else

begin

clk_oddP <= 1'b1 ;

end

end

reg clk_oddN=1'b0;

always@(negedge sys_clk)

begin

if(sys_rst) //复位信号,高有效

begin

clk_oddN <= 1'b0 ;

end

else

if(cnt <= (Multiple /2))

begin

clk_oddN <=1'b0;

end

else

begin

clk_oddN <= 1'b1 ;

end

end

wire clk_odd ;

assign clk_odd = clk_oddP | clk_oddN ; //通过或运算实现50%占空比。

//--------奇数分频过程------end---------//

//--------偶数分频过程------start---------//

reg clk_even=1'b0;

always@(posedge sys_clk)

begin

if(sys_rst) //复位信号,高有效

begin

clk_even <= 1'b0;

end

else

if(cnt <= (Multiple /2 -1))

begin

clk_even <= 1'b0 ;

end

else

begin

clk_even <= 1'b1 ;

end

end

//--------偶数分频过程------end---------//

endmodule

二、上仿真代码

`timescale 1ns / 1ps

/

module CLK_DIV_ODDandEVEN50P_TB;

// Inputs

reg sys_rst;

reg sys_clk;

// Outputs

wire clk_div;

wire [15:0] cnt;

// Instantiate the Unit Under Test (UUT)

CLK_DIV_ODDandEVEN50P uut (

.sys_rst(sys_rst),

.sys_clk(sys_clk),

.clk_div(clk_div),

.cnt(cnt)

);

initial begin

// Initialize Inputs

sys_rst = 1;

sys_clk = 0;

// Wait 100 ns for global reset to finish

#100;

sys_rst = 0;

forever #500 sys_clk=~sys_clk;

// Add stimulus here

end

endmodule

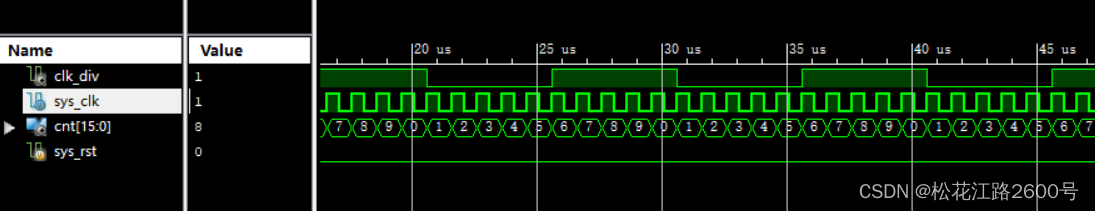

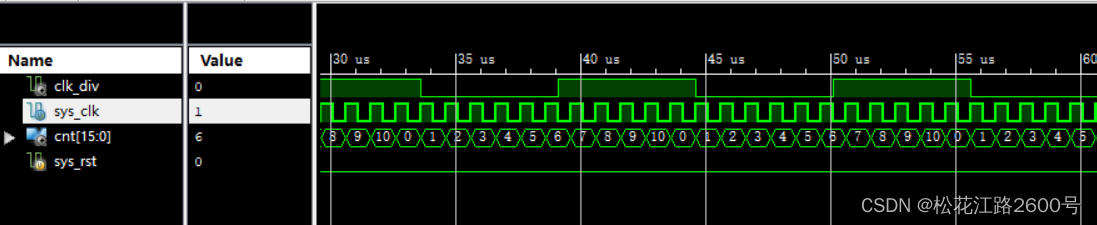

三、上仿真结果

由图1和图2可知,仅仅通过带边变量multiple的值可以实现不同分频,且满足50%占空比。其中:

①sys_clk是系统时钟,本代码中作为被分频时钟。

②clk_div是分频后时钟。

③cnt是计数器,作为分频计数使用。

④sys_rst是复位信号,高有效。

感谢关注。

这篇博客分享了一个用Verilog编写的分频器模块,能够实现奇数和偶数分频,并确保分频后的时钟占空比为50%。代码包括了奇数和偶数分频的详细过程,并附有测试代码及仿真结果,展示了10分频和11分频的效果。系统时钟、分频后时钟、计数器和复位信号是关键元素。

这篇博客分享了一个用Verilog编写的分频器模块,能够实现奇数和偶数分频,并确保分频后的时钟占空比为50%。代码包括了奇数和偶数分频的详细过程,并附有测试代码及仿真结果,展示了10分频和11分频的效果。系统时钟、分频后时钟、计数器和复位信号是关键元素。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?