问题1. 检测序列1001001,输入单bit,检测成功的次数用cnt表示,使用verilog描述?

Module AAA

#(

parameter width = 4 ;

)

(

Input clk,

Input rst_n,

Input data_in,

Output reg [width-1:0] cnt

);

//可以使用真实状态表示,也可以用gray或者binary表示。

Parameter idle = 7’b0000000;

Parameter s1 = 7’b0000001;

Parameter s2 = 7’b0000010;

Parameter s3 = 7’b0000100;

Parameter s4 = 7’b0001001;

Parameter s5 = 7’b0010010;

Parameter s6 = 7’b0100100;

Parameter s7 = 7’b1001001;

Reg [6:0] state_current ;

always@(posedge clk or negedge rst_n)

begin

if(rst_n==0)

begin

state_current <= idle ;

cnt <= 0;

end

else

begin

case(state_current)

idle:

if(data_in==0) state_current<=idle;

else state_current<=s1;

s1:

if(data_in==0) state_current<=s2;

else state_current<=s1;

s2:

if(data_in==0) state_current<=s3;

else state_current<=s1;

s3:

if(data_in==0) state_current<=idle;

else state_current<=s4;

s4:

if(data_in==0) state_current<=s5;

else state_current<=s1;

s5:

if(data_in==0) state_current<=s6;

else state_current<=s1;

s6:

if(data_in==0) state_current<=idle;

else state_current<=s7;

s7:

if(data_in==0) state_current<=idle;

else state_current<=s1;

default:

begin

state_current <= idle ;

cnt <= 0;

end

end

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n==0)

begin

cnt<=0;

end

else

if(state_current == s7)

cnt <= cnt+1 ;

end

endmodule

问题2:设计32bit计数器

问题3: 跨时钟域处理的几种方法,并用简单的代码进行描述

回答:

对于单bit信号使用两级寄存器

对于多bit信号,使用异步端口ram,异步fifo,格雷码转换。

问题4:

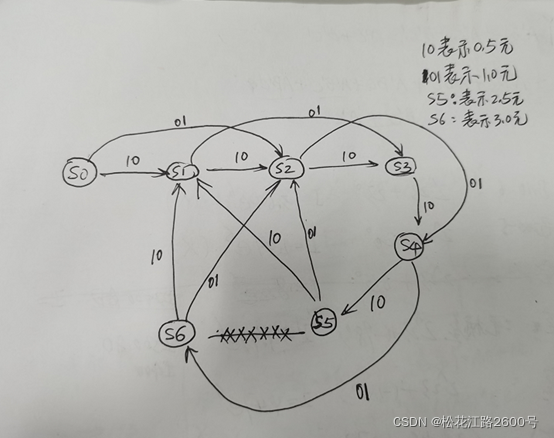

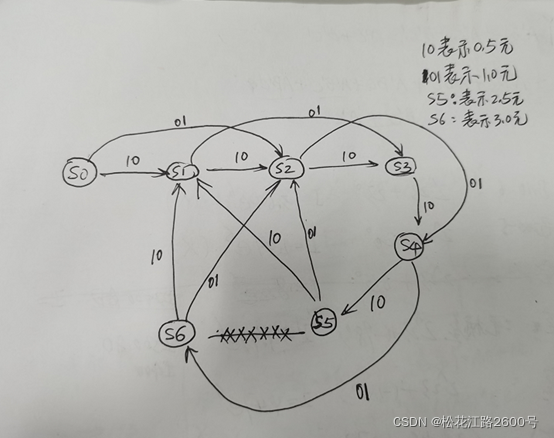

饮料价格是2.5元,每次投币一枚,分为0.5元和1元两种硬币。当投入2.5元时候,则售卖一瓶饮料,若投3元,则售卖一瓶饮料并找零0.5元,画出状态图,使用verilog描述?

Module AAA(

Input clk,

Input rst_n,

Input wujiao_in,

Input yiyuan_in,

Output sell,

Output zhaoling

);

Reg [3:0] currrent_state;

Parameter s0 = 3’b000; //0yuan

Parameter s1 = 3’b001; //0.5yuan

Parameter s2 = 3’b010; //1.0yuan

Parameter s3 = 3’b011; //1.5yuan

Parameter s4 = 3’b100; //2.0yuan

Parameter s5 = 3’b101; //2.5yuan

Parameter s6 = 3’b110; //3.0yuan

always@(posedge clk or negedge rst_n)

begin

if(rst_n==0)

begin

sell <= 0;

zhaoling <= 0 ;

currrent_state <= s0;

end

end

else

begin

case(currrent_state)

s0://0yuan

begin

sell <= 0;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s1;

else if(yiyuan_in) currrent_state<=s2;

end

s1://0.5yuan

begin

sell <= 0;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s2;

else if(yiyuan_in) currrent_state<=s3;

end

s2://1.0yuan

begin

sell <= 0;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s3;

else if(yiyuan_in) currrent_state<=s4;

end

s3://1.5yuan

begin

sell <= 0;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s4;

else if(yiyuan_in) currrent_state<=s5;

end

s4://2.0yuan

begin

sell <= 0;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s5;

else if(yiyuan_in) currrent_state<=s6;

end

s5://2.5yuan

begin

sell <= 1;

zhaoling <= 0 ;

if(wujiao_in) currrent_state<=s1;

else if(yiyuan_in) currrent_state<=s2;

end

s6://3.0yuan

begin

sell <= 1;

zhaoling <= 1 ;

if(wujiao_in) currrent_state<=s1;

else if(yiyuan_in) currrent_state<=s2;

end

default:

begin

currrent_state <= s0;

sell <= 0;

zhaoling <= 0 ;

end

endcase

end

Endmodule

该博客介绍了如何使用Verilog描述一个检测序列1001001的单bit计数器,以及设计一个根据硬币投入判断饮料售卖和找零状态的32位计数器。状态图详细展示了饮料售卖逻辑,包括0.5元和1元硬币的组合。

该博客介绍了如何使用Verilog描述一个检测序列1001001的单bit计数器,以及设计一个根据硬币投入判断饮料售卖和找零状态的32位计数器。状态图详细展示了饮料售卖逻辑,包括0.5元和1元硬币的组合。

2037

2037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?