参考正点原子相关资料

亚稳态的产生

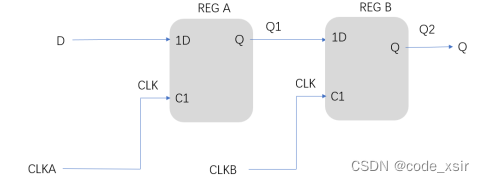

异步电路如果直接使用寄存器采样会出现问题,最常见的就是出现亚稳态。寄存器采样需要满足一定的建立时间(setup)

和保持时间(holdup),而异步电路没有办法保证建立时间(setup)和保持时间(holdup),所以会出现亚稳态。

因为两个时钟的相位和频率不同,寄存器B采样可能采样到寄存器A输出的任意状态,包括Q1的信号跳变沿

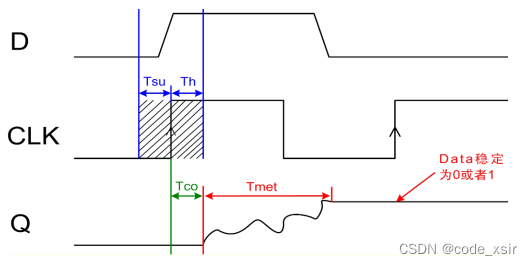

·而采样到D跳变沿时,信号跳变沿是一个信号上升的过程,时钟在信号跳变沿采样会采样到不同的电平。Q就会输出一段亚稳态,即在0和1之间变化,不稳定后趋于稳定,从不确定值到0或者1稳定值的持续时间称为决断时间。决断时间也随着初始电平而变化。

跨时钟域的信号同步

异步电路的设计就是要解决亚稳态的问题。

1、单 bit 信号:直接多级寄存器同步法,一般采用 2-3 级寄存器进行同步处理,这个 2-3 级寄存器也称作同步器,在 ASIC 设计中,一般都有提供专用的同步器库,因为同步器要求多级寄存器位置靠的越近越好,靠的越近,亚稳态消失的概率就越大。 FPGA 设计中,直接使用 2-3 级寄存器进行同步处理即可。

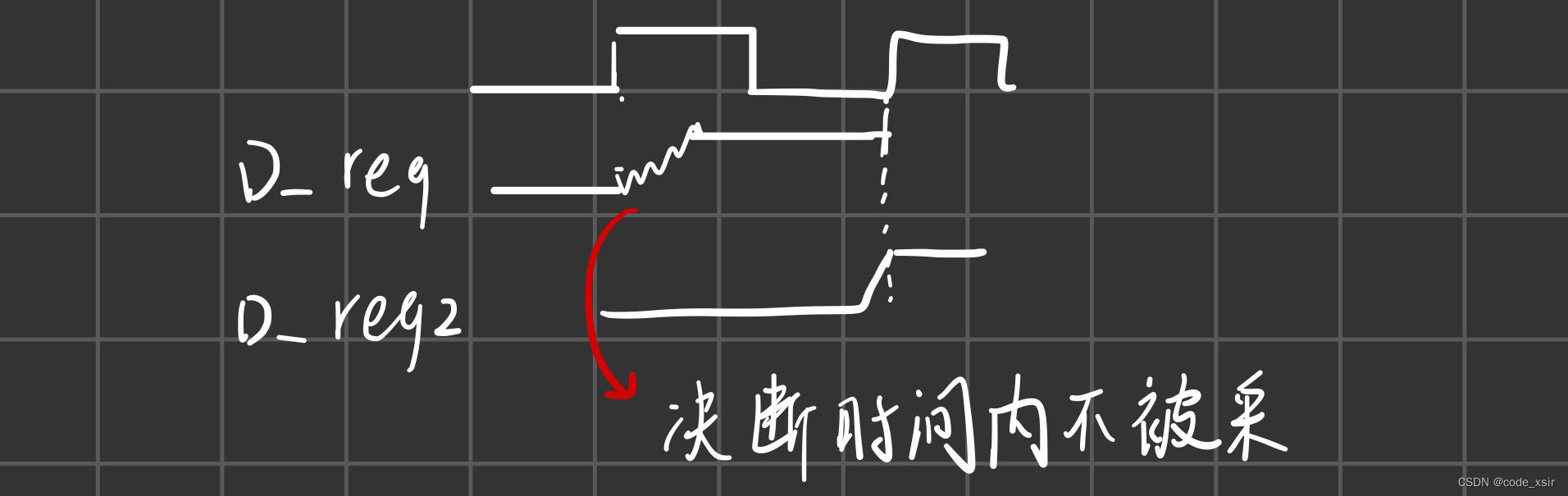

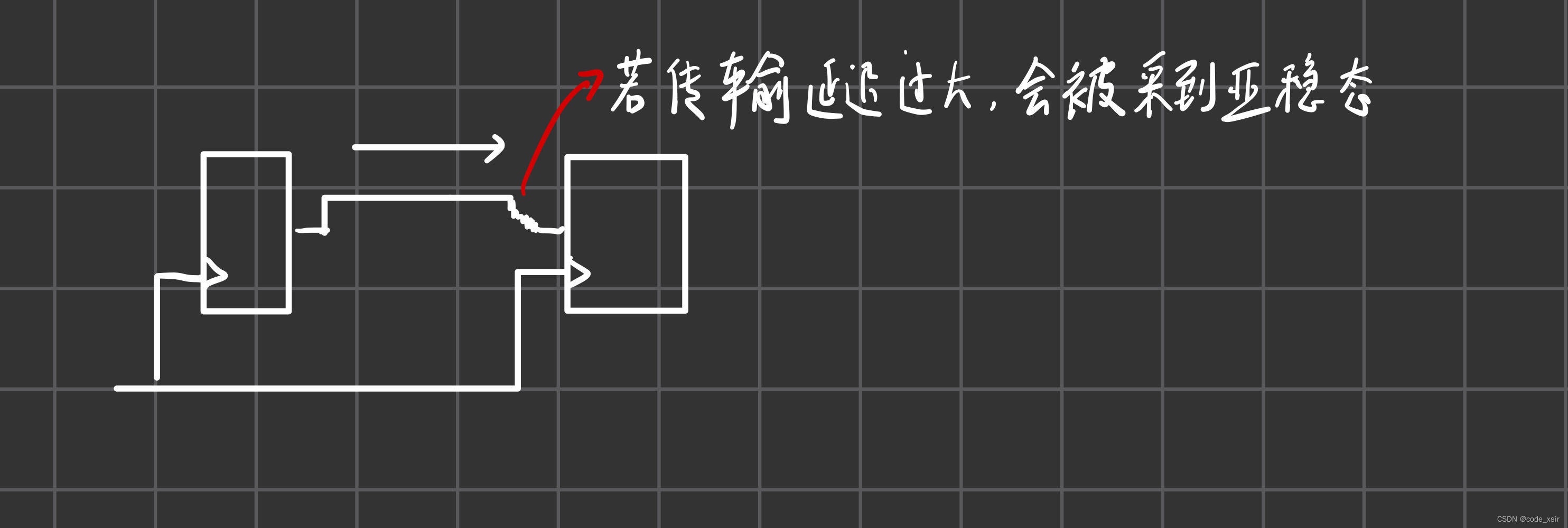

常用的“打两拍”同步:两个寄存器,第一个对跨时钟域信号进行采样,可以采样到亚稳态,第二个寄存器对第一个的稳定信号段进行采样,采样到的即是同步好的稳定信号。

注:

(1)要保证第一个寄存器的决断时间加上到第二个寄存器的传输延迟小于一个时钟周期,否则第二个寄存器采样到的仍有亚稳态。(一般设计中都能满足,决断时间较小,打拍寄存器有专用同步器库,之间的延迟也较小)

(2)明确亚稳态不是开始就被消除了,而是利用同步寄存器间的时钟可控(相位周期已知),保证第一个寄存器输出信号的亚稳态传输到第二个寄存器时,第二个寄存器不采样(采样沿是可控),而是在稳定信号段传输到时采。

2、多 bit 信号:异步 FIFO 或者使用多次握手同步方法。 在握手协议中,异步的 REQ/ACK 也需要使用单 bit 同步技术进行同步处理,异步 FIFO 也是如此。

本文讨论了异步电路中由于缺乏稳定的时间保证而产生的亚稳态问题,介绍了单bit信号通过多级寄存器同步以及打两拍同步方法来解决,同时提到了多bit信号处理的异步FIFO和握手协议的应用。

本文讨论了异步电路中由于缺乏稳定的时间保证而产生的亚稳态问题,介绍了单bit信号通过多级寄存器同步以及打两拍同步方法来解决,同时提到了多bit信号处理的异步FIFO和握手协议的应用。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?