数码管动态显示

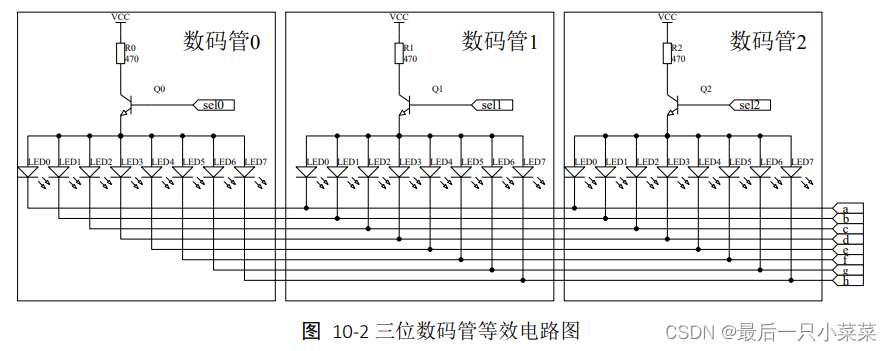

一、分析原理图

- 8个数码管 SEL

- 8个显示电路 a,b,c,d,e,f,g,h SEG

- 要使哪一个亮,则将SEL[X]置为1,X线拉低--------->使用一个3-8译码器,根据cnt[2:0]来选择哪一个数码管亮

- 所以不同的数都可以根据SEL和SEG来进行选择

- 根据输入的不同的数来进行显示,一共有8个数码管,一个数的范围是0-f 。需要4位,一共8个,所以需要32位------->[31:0] Disp_data

- 使用一个3-8译码器来选择,显示哪一个数字

二、代码实现

-

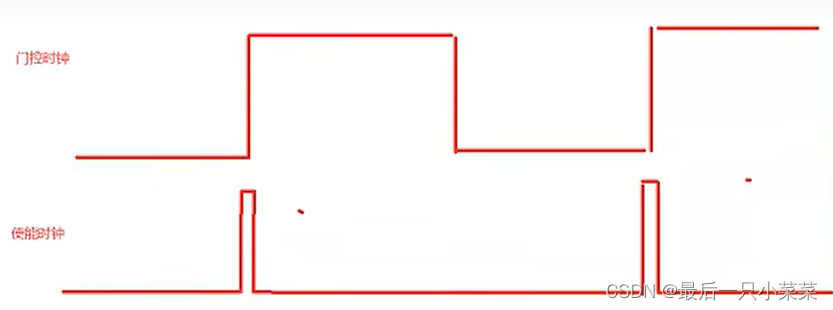

首先由于每个数码管是串行显示的(节省管脚数),如果需要同时显示,需要每个数码管在20ms内亮一次,达到视觉暂留的现象。

所以要求每个数码管在每20ms内都要点亮一次,所以20ms/8=2.5ms,所以每个灯点亮时间需要小于2.5ms。假设计数器以1ms的周期来计数 -

ACX720的时钟频率是50M,我们所需的是1K的时钟周期。所以要进行分频。周期为1ms,所以每500微秒翻转一次。也即计数500000ns/20ns=25000次

-

一般不能直接posedge 不是clk的时钟,不稳定且有延迟。可以改成使能时钟,例如EN。 所以计数一个周期即可。50000次

//计数器

reg [15:0] div_cnt;

always @(posedge Clk or negedge Reset_n) begin

if (!Reset_n)

div_cnt<=0;

else if (div_cnt>=50000-1)

div_cnt<=0;

else

div_cnt<=div_cnt+1'b1;

end

//这样写时钟信号的高电平只持续一个时钟周期,只有一个突起--P26 17C 20min

reg clk_lk;

always @(posedge Clk or negedge Reset_n) begin

if (!Reset_n)

clk_lk<=0;

else if (div_cnt>=50000-1)

clk_lk<=1;

else

clk_lk<=0;

end

//每过一个周期选择器加一,一共8个选择器,所以刚好[2:0]

reg [2:0] num_cnt;

always @(posedge Clk or negedge Reset_n) begin

if (!Reset_n)

num_cnt<=0;

else if(clk_lk)

num_cnt<=num_cnt+1;

end

- 根据不同的选择器,选择点亮哪一个数码管和需要显示的数字

//3-8译码器

always @(posedge Clk)

case(num_cnt)

0:SEL<=8'b00000001;

1:SEL<=8'b00000010;

2:SEL<=8'b00000100;

3:SEL<=8'b00001000;

4:SEL<=8'b00010000;

5:SEL<=8'b00100000;

6:SEL<=8'b01000000;

7:SEL<=8'b10000000;

endcase

//选择输入的8个数中的一个

reg [3:0] disp_tmp;

always @(posedge Clk)

case(num_cnt)

7:disp_tmp=Disp_data[31:28];

6:disp_tmp=Disp_data[27:24];

5:disp_tmp=Disp_data[23:20];

4:disp_tmp=Disp_data[19:16];

3:disp_tmp=Disp_data[15:12];

2:disp_tmp=Disp_data[11:8];

1:disp_tmp=Disp_data[7:4];

0:disp_tmp=Disp_data[3:0];

endcase

- 通过查找表选择哪一段点亮

//查找表-通过具体的值输出哪几段

always @(posedge Clk)

case(disp_tmp)

0:SEG=8'hc0;

1:SEG=8'hf9;

2:SEG=8'ha4;

3:SEG=8'hb0;

4:SEG=8'h99;

5:SEG=8'h92;

6:SEG=8'h82;

7:SEG=8'hf8;

8:SEG=8'h80;

9:SEG=8'h90;

4'ha:SEG=8'h88;

4'hb:SEG=8'h83;

4'hc:SEG=8'hc6;

4'hd:SEG=8'ha1;

4'he:SEG=8'h86;

4'hf:SEG=8'h8e;

endcase

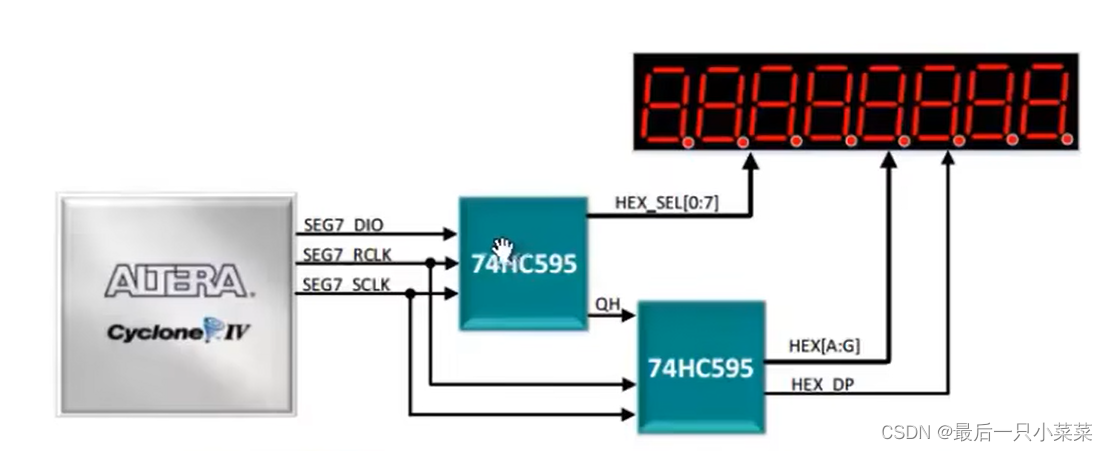

三、ACX720开发板的板级实验

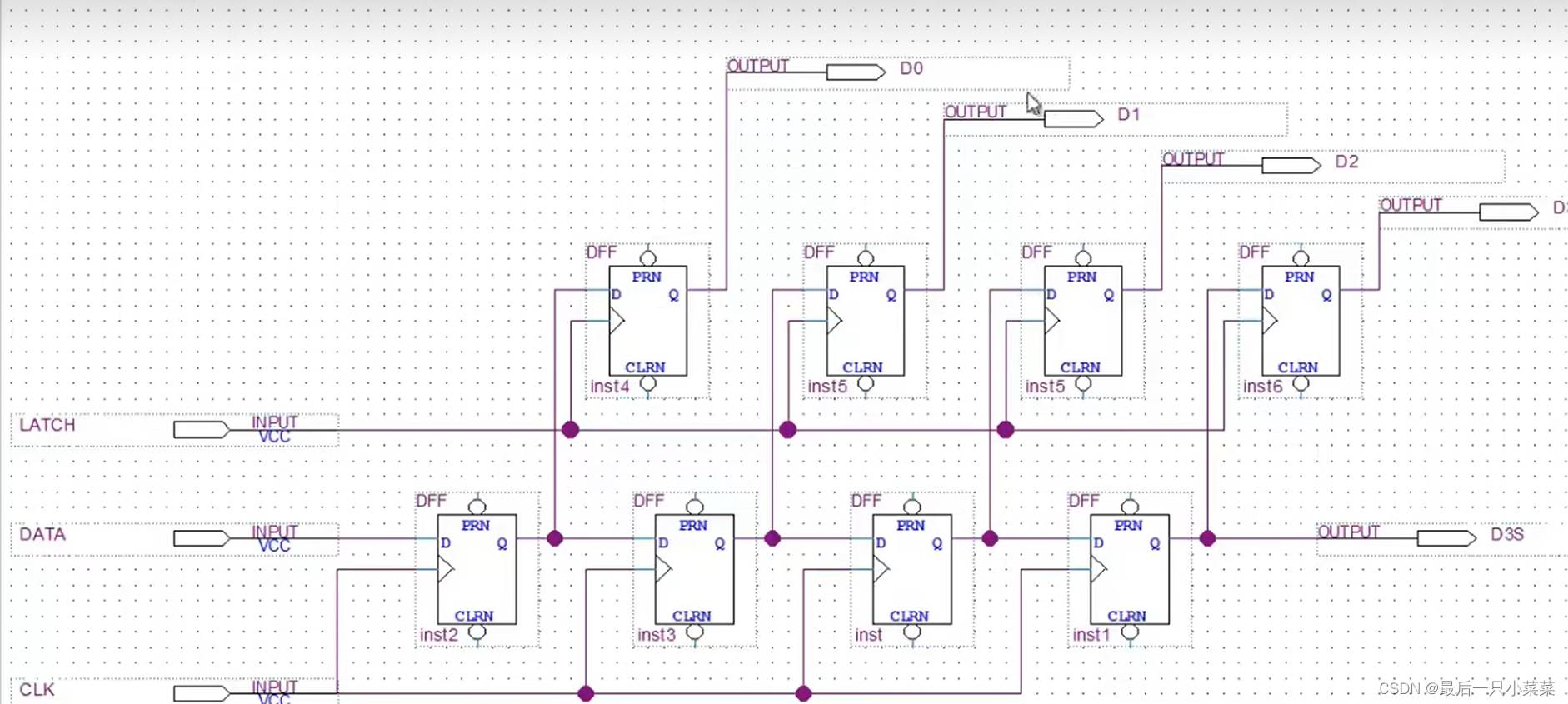

- 通过移位寄存器和输出锁存器来实现串转并的功能。

- 例如下图:在四个周期之后,所有的移位寄存器都接收到data的值,再统一通过LATCH信号,传输给D,实现并行输出。

- 这个功能就在74HC595里面实现。

- FPGA需要通过74HC595这个芯片把16位的数据(SEL+SEG) 变为并行端口用来驱动数码管

- FPGA通过三根数据线,也就是图中的Clk、Data、Latch信号

- 3.3V供电情况下,取SHCP的时钟频率为12.5MHz

1015

1015

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?