1. Verdi 如何将已经设置好的nSchematic view 保存下来,方便下次的使用

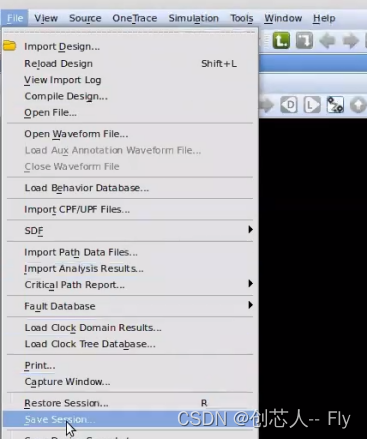

Step1:点击file的save_session,进去后直接保存文件;

Step2:下一次进入后打开nSchem后在此打开file点击restore session(save session)上边的按钮,找到之前保存的文件load进来就可以了。

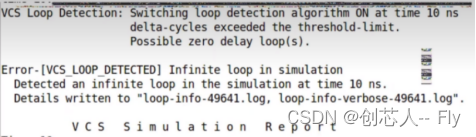

2. 如何在Vcs中快速debug hang 的问题

方法1:

分别在编译仿真的时候添加+vcs+loopreport/+vcs+loopdetect

%vcs test.v +vcs+loopreport -debug_access+all -l comp.log

%./simv +vcs+loopreport -l run.log

这样在仿真的过程中出现hang的时候会打印到log,如下:

方法二:

在编译中添加:

%vcs -Xvgprofile -Xmod=0x13;

当仿真挂起的时候再通过:

% pstack <PID> //ps -u

此时会打印hang的信息;

注意:方法二一般用在非死循环原因的hang

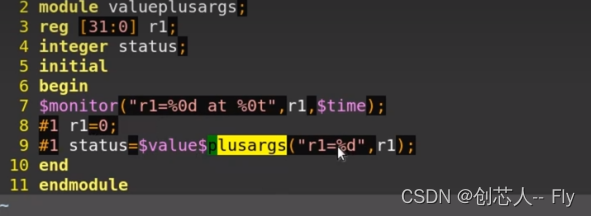

3. Vcs 仿真是如何给环境里变量赋值

$value$plusargs();

在仿真时添加:+r1=<想加入的值>;

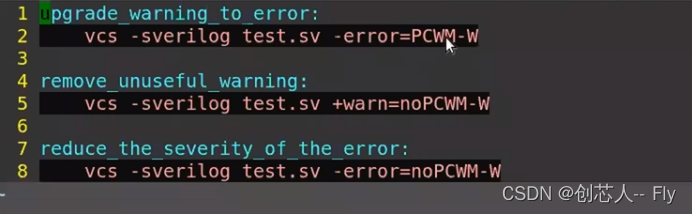

4. Vcs对编译的warning error进行动态调整

5. Vcs constraint error 时控制仿真立刻停止

% simv +ntb_stop_on_constraint_solver_error=1

6. 加速仿真的几种方法(先列出来,后续再深究)

PC

FGP

DPO

ICO

DTL

VSO.ai

distribution complie

distribution simulation

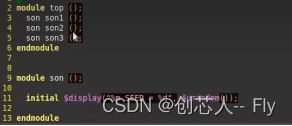

7. 一个module中多个instance 在随机时如何产生不同的随机数

可以在仿真时添加:

-xlrm hier_inst_seed

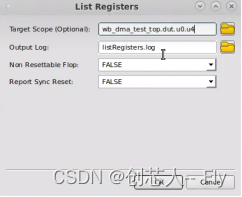

8. Verdi 如何快速把design所有寄存器找出来

Step1:在Verdi里边点击APP->design exploration->list registers,根据实际自行设置

Step2:在smartlog 中输出报告

9. Verdi中变频信号如何直观显示频率值

Step1:选中clk信号,点击菜单栏里边的analog->capture frequency,此时会显示频率;

Step2:如果此时不是很直观,可以继续右击点击digital waveform,通过直观的数字进行观察

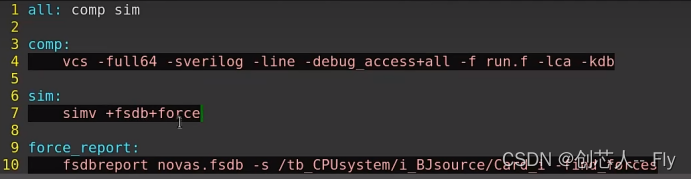

10. Verdi如何快速debug force信号

Verdi里边对force 的信号进行标记(source->active annotation 快捷键X)

输出report的命令:

fsdbreport <fsdb文件> -s <信号> -find_forces

Make force_report 会输出force文件

11. Verdi快速检查memory的值

Step1:选中要查找的mem,右击使用debug memory

Step2: 选中show memory contents 查看mem的值。

12. Verdi 如何将string dump到fsdb 中

Step1:首先将string储存到reg中或者写入到多bit中;

Step2:将regvar, strvar 拉到波形中,使用ASCII(set radix)

13. 如何不起Verdi 快速查看fsdb中的某个信号名

% fsdbreport <fsdb文件> -s <heri的信号名>

fsdbreport -h 获取帮助

14. 启动多个Verdi如何给各个Verdi加不同title

Verdi preTitle <自定义> &

15. Verdi 波形中如何更改real类型精度

Step1:选中信号点击analog->format and precision

Step2: 选择engineering 自行修改即可

16. Verdi 如何将需要的sequence 输出到一个文件

Step1:在波形中选中需要的sequence,file->report selected singles

Step2: 根据需要设置sequence范围,文件名,option(默认9位,更多位输出使用-w 位宽)

Step1:编译时添加-debug_access+all+reserve

Step2: 进入Verdi切换为交互式debug模式(window->interactive debug mode)

Step3: 确保reserve debug功能打开(tool->preferences->interactive debug->reserve debug勾选)

加reverse的优势:可以回退

17. Verdi merge multiple coverage databases

Step1: merge

%urg -dir <vdb1> <vdb2> -dbname merge.vdb

%urg -full64 -f vdb_filelist -dbname merge.vdb 适用于文件类型

Step2: verdi 打开

Verdi -cov -covdir merge.vdb

18. Verdi 对phase的快速断点方式

Step1:进入交互式debug模式(上边有讲)

Step2: 点击▼可在build、run、cleanup 中进行选择添加

19. Verdi如何dump你想要的波形

方法一:

Dump vcs 已经分类好的信号,example:

$fsdbDumpvars(“+Reg_Only”);

具体支持什么参数可以自行查找;

方法二:

Dump 某个instance的信号,example:

$fsdbDumpvars(0,“tb.dut.inst1”,”inst1.fsdb”);

$fsdbDumpvars(0,“tb.dut.inst2”,”inst2.fsdb”);

覆盖不到的场景可以参考linking novas files with simulators and enabling FSDB dumping

20. Verdi debug 状态机显示名字

波形显示状态机string状态方法:

Tool->extract interactive FSM

波形取消状态机string状态方法:

选中要取消的信号,点击waveform->set radix->remove alias

其他的有空在整理

本文详细介绍了Verdi工具在电路设计中的各种操作技巧,包括保存设置、VCS调试hang问题、变量赋值、fsdb使用、内存检查、波形格式调整等,旨在提升设计和调试效率。

本文详细介绍了Verdi工具在电路设计中的各种操作技巧,包括保存设置、VCS调试hang问题、变量赋值、fsdb使用、内存检查、波形格式调整等,旨在提升设计和调试效率。

212

212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?