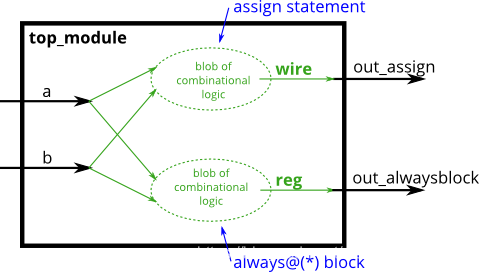

1、Alwaysblock1

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = a & b ;

always @(*) out_always = a & b ; //本身只有一句所以不用加begin/end

endmodule

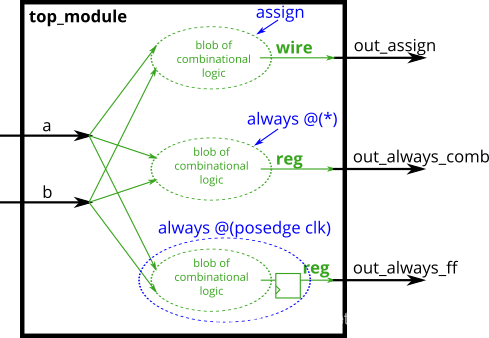

2、Alwaysblock2

要求:Build an XOR gate 3 ways

// synthesis verilog_input_version verilog_2001

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

assign out_assign = a ^ b;

always @(*) out_always_comb = a ^ b;

always @(posedge clk) out_always_ff <= a ^ b;

endmodule

Tips:阻塞分配与非阻塞分配

在Verilog中有三种类型的赋值

Continuous assignments (assign x = y;). Can only be used when not inside a procedure (“always block”).

Procedural blocking assignment: (x = y;). Can only be used inside a procedure.

Procedural non-blocking assignment: (x <= y;). Can only be used inside a procedure.

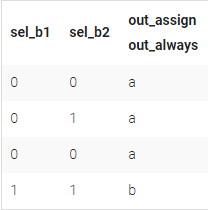

3、Always if

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

always @(*) begin

if (sel_b1 == 1 && sel_b2 == 1) begin

out_always = b;

end

else begin

out_always = a;

end

end

assign out_assign = (sel_b1 == 1 && sel_b2 == 1)? b : a;

endmodule

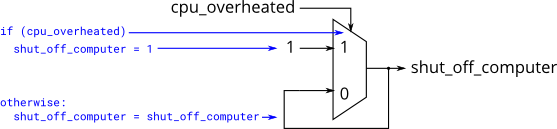

4、Always if2

注意:此题为改错题

我的代码:

// synthesis verilog_input_version verilog_2001

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer = 0;

end

always @(*) begin

if (arrived == 0 && gas_tank_empty == 0)//只有一句就没加begin\end上同

keep_driving = 1;

else

keep_driving = 0;

end

endmodule

5、Always case

说明:When sel is between 0 and 5, choose the corresponding data input. Otherwise, output 0.

// synthesis verilog_input_version verilog_2001

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'b000:out = data0;

3'b001:out = data1;

3'b010:out = data2;

3'b011:out = data3;

3'b100:out = data4;

3'b101:out = data5;

default:out = 0;//data0;

endcase

end

endmodule

6、Always case2

说明:A priority encoder is a combinational circuit that, when given an input bit vector, outputs the position of the first 1 bit in the vector. For example, a 8-bit priority encoder given the input 8’b10010000 would output 3’d4, because bit[4] is first bit that is high.

我的代码:

// synthesis verilog_input_version verilog_2001

module top_module (

input [3:0] in,

output reg [1:0] pos );

always @(*)begin

case(in)

4'd0:pos = 0;

4'd1:pos = 0;

4'd2:pos = 1;

4'd3:pos = 0;

4'd4:pos = 2;

4'd5:pos = 0;

4'd6:pos = 1;

4'd7:pos = 0;

4'd8:pos = 3;

4'd9:pos = 0;

4'd10:pos = 1;

4'd11:pos = 0;

4'd12:pos = 2;

4'd13:pos = 0;

4'd14:pos = 1;

4'd15:pos = 0;

default: pos = 2'b0;

endcase

end

endmodule

7、Always casez

注意: This is what casez is for: It treats bits that have the value z as don’t-care in the comparison.

为8位输入构建优先级编码器。

我的代码:

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @(*) begin

casez (in[7:0])

8'bzzzzzzz1: pos = 0; // in[3:1] can be anything

8'bzzzzzz1z: pos = 1;

8'bzzzzz1zz: pos = 2;

8'bzzzz1zzz: pos = 3;

8'bzzz1zzzz: pos = 4; // in[3:1] can be anything

8'bzz1zzzzz: pos = 5;

8'bz1zzzzzz: pos = 6;

8'b1zzzzzzz: pos = 7;

default: pos = 0;

endcase

end

endmodule

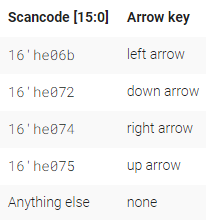

8、Always nolatches

这个题是判断按键按下

映射表:

我的代码:

(not sure)

// synthesis verilog_input_version verilog_2001

module top_module (

input [15:0] scancode,

output reg left,

output reg down,

output reg right,

output reg up );

always @(*) begin

up = 1'b0; down = 1'b0; left = 1'b0; right = 1'b0;

case (scancode)

16'he06b:left =1;

16'he072:down =1;

16'he074:right =1;

16'he075:up =1;

//default:

endcase

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?