目录

在本实验练习中,您将学习如何使用多个时钟域有效地实现具有多个数据速率的设计。

目标:

- 了解使用多个时钟域实现多速率设计的好处。

- 了解如何使用FIFO隔离层次结构,以创建用于传输异步数据的安全通道。

- 如何用不同的时钟实现层次结构。

本文实验包含三个部分:

- 学习如何在时钟域之间创建层次结构。

- 学习如何在层次结构之间添加FIFO。

- 了解如何为每个层次结构添加单独的时钟域。

本文实验环境:Vivado 2019.1、System Generator 2019.1、Matlab R2024a。

一、创建时钟域层次结构(Creating Clock Domain Hierarchies)

在这一步中,您将回顾一个设计,其中设计的不同部分以不同的数据速率运行,并将设计划分为子系统,以便在不同的时钟域中实现。

1、打开System Generator。

2、文件准备,这里使用Xilinx官网提供的UG948文档教程参考文件。

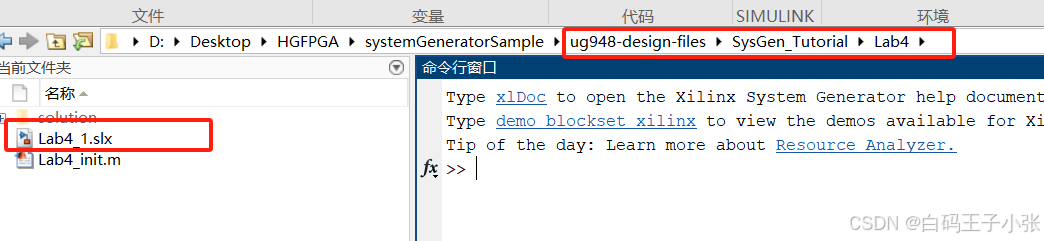

3、在Matlab中打开参考文件所在的目录,并双击打开Lab4_1.slx文件。

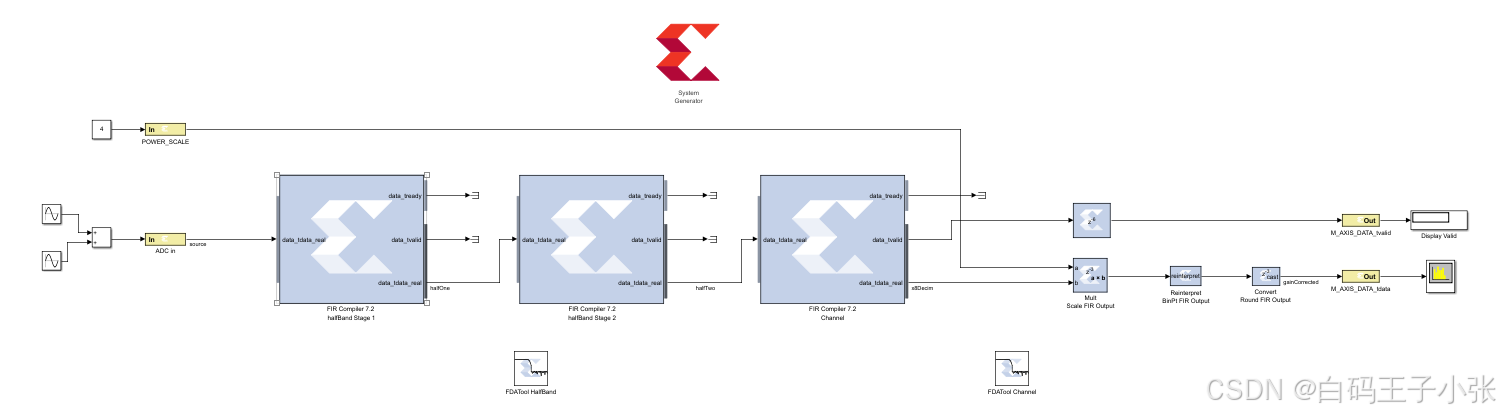

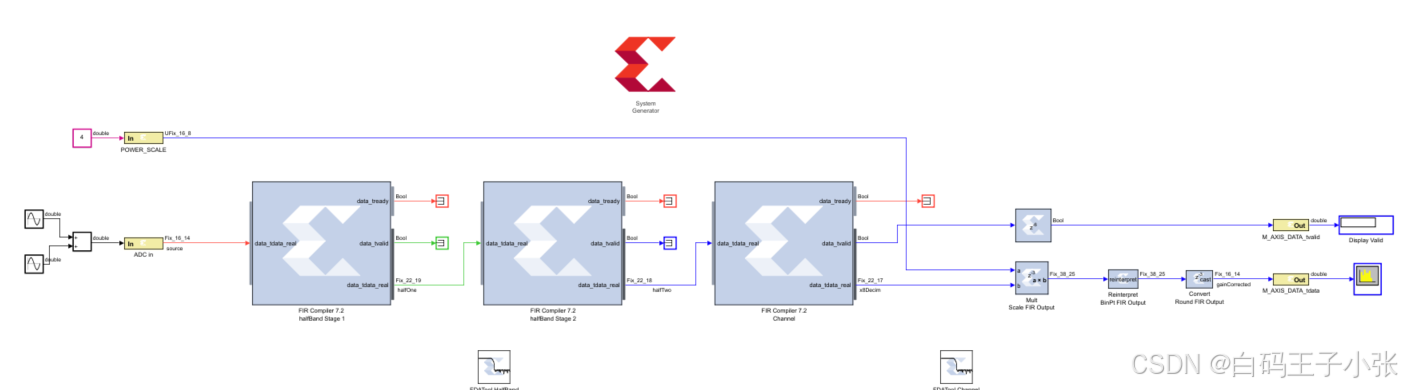

这将打开如下图所示的Simulink设计。本设计主要由三个基本部分组成:

- 通道滤波器将输入信号(491.52 MSPS)数字转换为近基带(61.44 MSPS)使用经典的多速率滤波器:使用两个半带滤波器,然后是2级滤波器的抽取,这比单个大滤波器需要的系数要少得多。

- 输出部分增益控制将使用该数据的后续块的输出。

- 增益由POWER_SCALE输入控制。

4、单击Run simulation按钮来仿真设计。

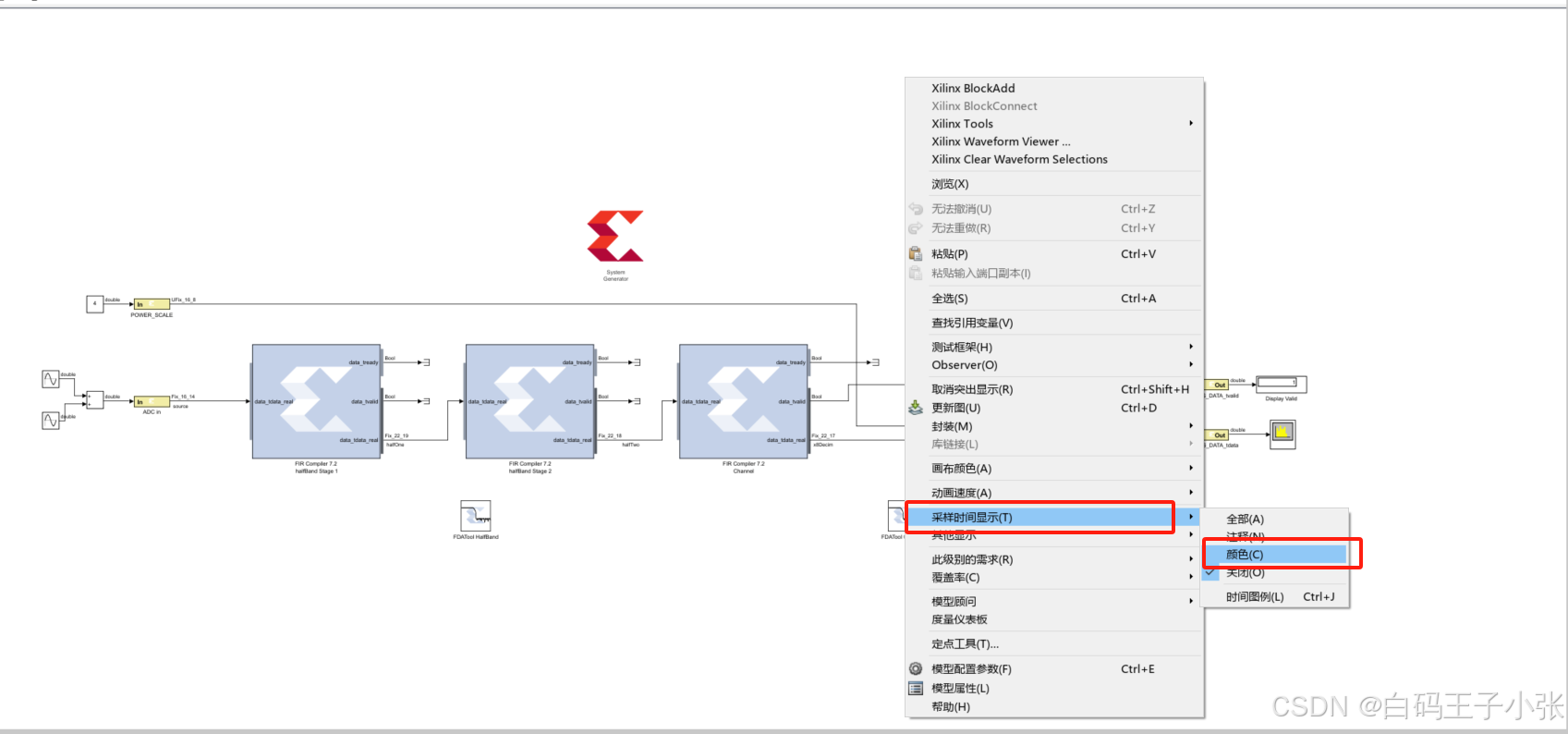

在下图中采样时间显示(Sample Time Display)是有颜色的(在画布中右击>Sample Time Display>Colors),并且清楚地表明该设计在多种数据速率下运行。

5、System Generator环境通过设计自动传播不同的数据速率。

当在硬件中实现这样的多速率设计时,最理想的实现是使用与数据相同频率的时钟;然而,在这种环境中,时钟是抽象出来的。下面的方法演示了如何以最有效的方式创建这个理想的实现。

6、为了使用System Generator有效地实现多速率(或多时钟)设计,您应该使用自己的System Generator令牌在其自己的层次结构中捕获以相同数据速率(或时钟频率)运行的每个部分。然后应该将单独的层次结构与FIFO链接起来。

7、目前的设计有两个明显的时钟域和一个不太明显的时钟域:

- 增益控制输入POWER_SCALE可以从CPU配置,因此可以与CPU相同的时钟频率运行。

- 输出级上的实际增益控制逻辑应该以与FIR输出数据相同的频率运行。这将允许它更有效地连接到系统中的后续块。

- 不太明显的区域是过滤链。在实验1中,复杂的IP提供System Generator,如FIR编译器,自动利用超频提供最有效的硬件。例如,与其使用以100MHz运行的40个乘数,

- 如果时钟为500 MHz (= 40*100/500), FIR编译器将仅使用8个乘法器。因此,整个滤波器链可以被分组到单个时钟域。第一个FIR Compiler实例将以最大时钟速率执行,随后的实例将自动利用过采样。

首先将这些区域分组到不同的层次结构中。

8、选择滤波器链中的所有块-所有这些都在同一时钟域中,包括FDATool实例—如下所示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2309

2309

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?