定点补码加法器设计

先行进位加法器

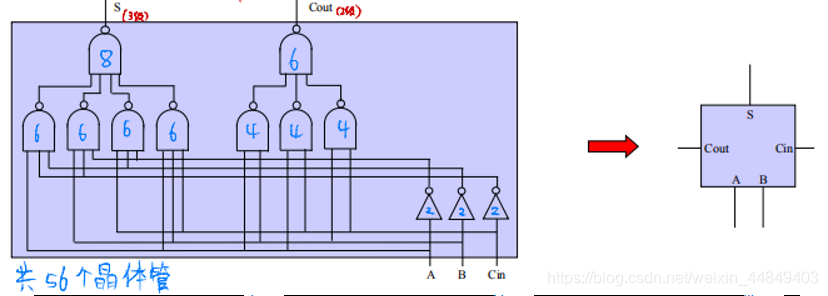

(1)一位全加器:

1)引脚:

- 三个输入: A, B, Cin

- 两个输出: S, Cout

2)逻辑真值关系:

3)逻辑框图:

- 需要2,3级门延迟:

- 进位传递2级延迟;

- 产生结果3级延迟; - 两级与非相当于与或:^ ( ^ ( AB ) ^ ( CD ) ) = AB+CD;

(2)串行进位加法器(以16位加法器为例):

- 进位从低位到高位传送, 形成c16需要32级门延迟;

- 延迟随位数增长线性增长;

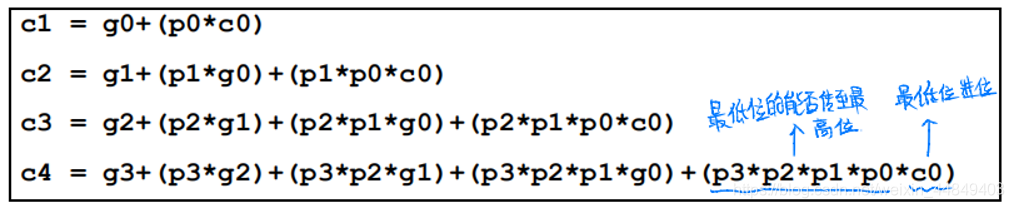

(3)并行进位逻辑:

1)进位传递:

- 推导:

c i + 1 = a i b i + a i ∗ c i + b i ∗ c i = a i ∗ b i + ( a i + b i ) ∗ c i = g i + p i ∗ c i ci+1 = aibi+ai*ci+bi*ci = ai*bi+(ai+bi)*ci = gi+pi*ci ci+1=aibi+ai∗ci+bi∗ci=ai∗bi+(ai+bi)∗ci=gi+pi∗ci

g i = a i ∗ b i gi=ai*bi gi=ai∗bi(进位生成因子): 只要gi为1, 就有进位;

p i = a i + b i pi=ai+bi pi=ai+bi(进位传递因子):只要pi为1, 就把低位进位向前传递; - 四位进位传递举例:

- 结论:只要低位有一个进位生成, 而且被传递, 则进位输出为1

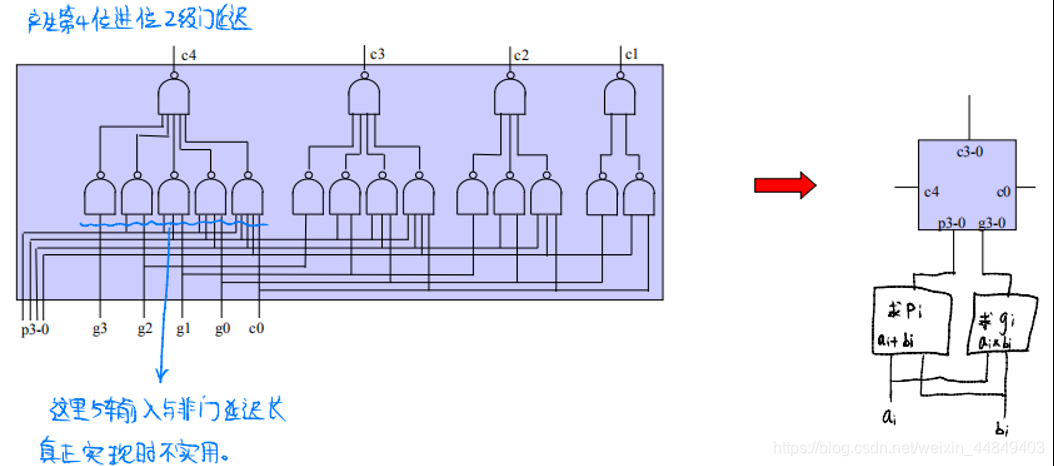

2)4位并行进位加法器逻辑框图:

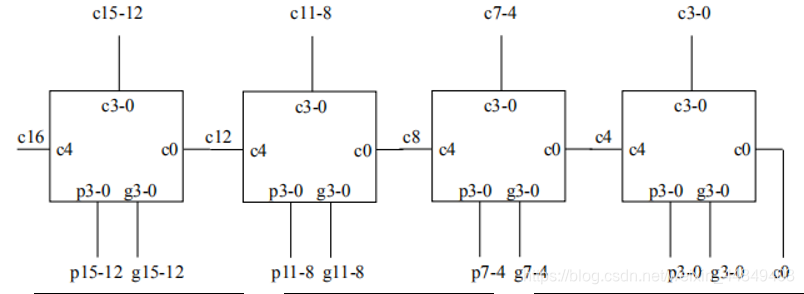

3)改进:以16位加法器为例—分块,块内并行(先行进位),块间串行

- 输入为pi、gi,输出为ci;

- 每次并行产生4位进位,从pi、gi产生c16只要4级传递,8级门延迟(产生运算结果还需要一个异或)。原来从ai、bi产生c16需要16级传递,32级门延迟;

4)进一步改进:以16位加法器为例—分块,块内并行,块间并行

① 进位推导:

- 老办法:产生每块的进位传递因子和进位产生因子

- 进位传递因子:每一位的传递因子都为1时才能传递

P = p 0 ∗ p 1 ∗ p 2 ∗ p 3 P = p0*p1*p2*p3 P=p0∗p1∗p2∗p3(本块可以传递低位进位) - 进位产生因子:块内产生进位, 不考虑进位输入

G = g 3 + ( p 3 ∗ g 2 ) + ( p 3 ∗ p 2 ∗ g 1 ) + ( p 3 ∗ p 2 ∗ p 1 ∗ g 0 ) G = g3+(p3*g2)+(p3*p2*g1)+(p3*p2*p1*g0) G=g3+(p3∗g2)+(p3∗p2∗g1)+(p3∗p2∗p1∗g0)(本块有进位生产)

c 4 = g 3 + ( p 3 ∗ g 2 ) + ( p 3 ∗ p 2 ∗ g 1 ) + ( p 3 ∗ p 2 ∗ p 1 ∗ g 0 ) + ( p 3 ∗ p 2 ∗ p 1 ∗ p 0 ∗ c 0 ) = G + ( P ∗ c 0 ) c4 = g3+(p3*g2)+(p3*p2*g1)+(p3*p2*p1*g0)+(p3*p2*p1*p0*c0)= G +(P*c0) c4=g3+(p3∗g2)+

本文详细介绍了定点补码运算器的设计,包括先行进位加法器的逻辑实现,如一位全加器、串行和并行进位加法器的优化,并探讨了补码乘法器的设计原理和Booth算法。此外,还阐述了定点ALU的构造,如判断相等、判断大小和移位操作的逻辑。通过对补码减法算法的解析,展示了如何实现定点运算器的高效计算。

本文详细介绍了定点补码运算器的设计,包括先行进位加法器的逻辑实现,如一位全加器、串行和并行进位加法器的优化,并探讨了补码乘法器的设计原理和Booth算法。此外,还阐述了定点ALU的构造,如判断相等、判断大小和移位操作的逻辑。通过对补码减法算法的解析,展示了如何实现定点运算器的高效计算。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?